# Silicon Interposer Design: Architecture through Implementation

Bill ACITO IC Packaging Product Engineer MEPTEC Nov 2012

cādence®

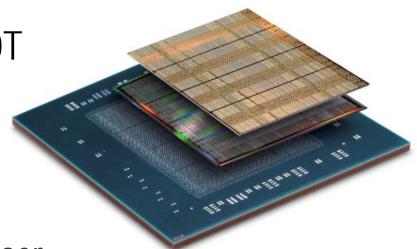

# Silicon Interposer Design

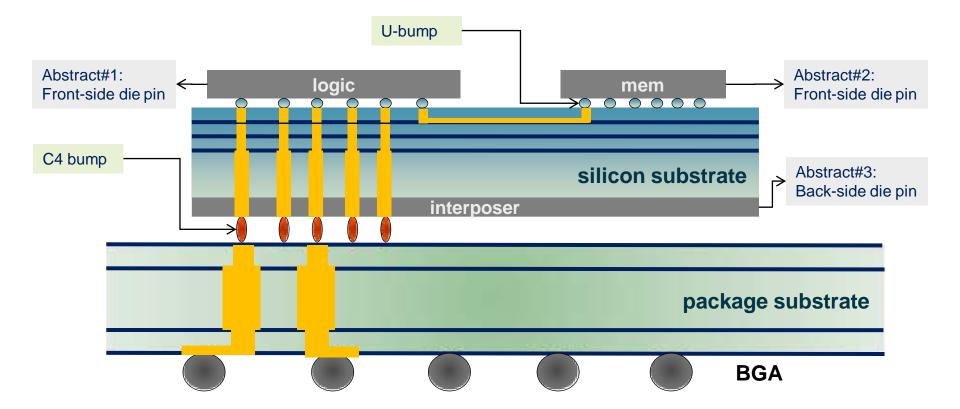

- Today's interposer serves as a bridge between the higher density of today's die, and the IC package

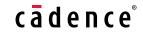

- Is interposer design an IC design challenge, or a IC packaging design challenge?

# Interposer: Bridges IC and Package design

| Interposer Features | "Coarse"                               | "Fine"                               |

|---------------------|----------------------------------------|--------------------------------------|

| Metal Line/Space    | > 5um/5um                              | < 1um/1um                            |

| Provider            | Package house, using RDL manufacturing | Foundry, using IC manufacturing      |

| RDL Metal           | Cu                                     | Al, Cu                               |

| RDL Thickness       | 3-5um                                  | <1um                                 |

| Passive Devices     | Yes                                    | Yes                                  |

| Cost                | Lower                                  | Higher                               |

| Application         | Low I/O Count                          | High I/O Count                       |

| Design Rules        | Package-Like                           | IC-Like                              |

| Design Tool         | APD/SiP (EDI/VLE for Validation)       | EDI/VLE (APD/SiP for<br>Feasibility) |

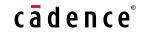

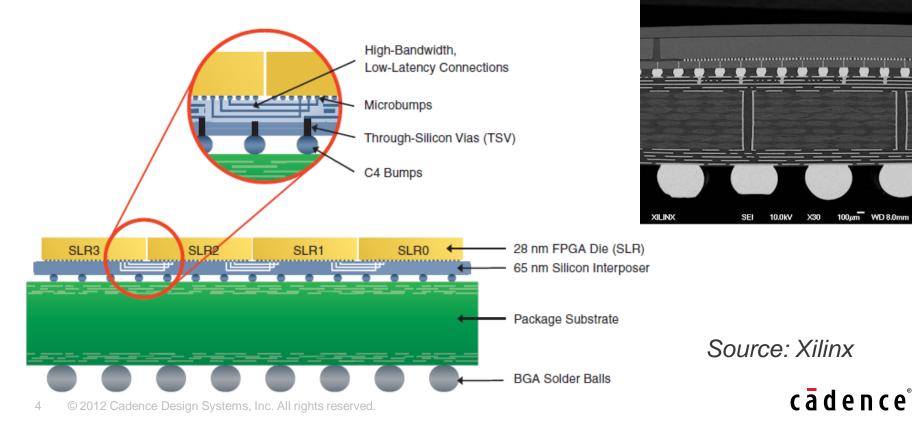

# "Classic" Interposer: Virtex-7 2000T

- "Stacked Silicon Interconnect"

- 6.8 Billion transistors

- Four 28nm die on a "fine" Interposer

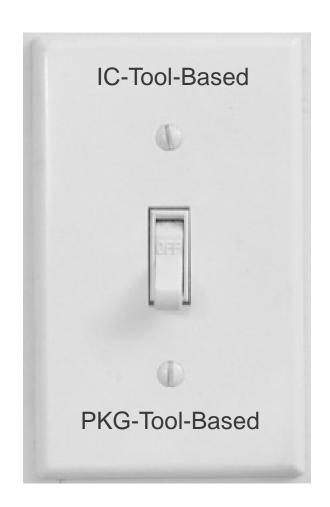

# IC-Based 2.5D vs PKG-Based 2.5D

#### •IC Technology-Based Solution

- •Analysis include Core logic

- •Design for TEST

- •Timing Analysis (STA)

- •Manufacturing ready DRC

- TSV implementation

#### •PKG/PCB Technology-Based Solution

System Interconnect Analysis

System Optimization thru all domains

Package Routing Technology

Core areas could be Black box

TSV proposal

## cādence°

## Perfect World: Interposer Design

# Reality

- Who "owns" the design (IC team, PKG team)? What tools are available?

- What design process node? Course or fine width? What geometry design rules? What IC design structures are needed (power stripes, redundant via)? What layer materials for metal and dielectric?

- Who is making the silicon? (in house, external)

- What is required for IC implementation/mask generation?

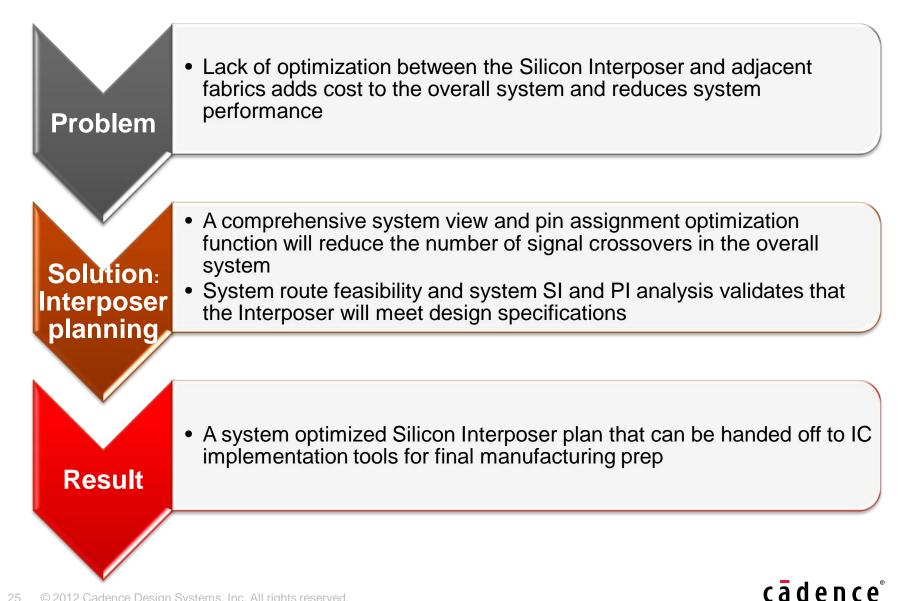

# Why use Packaging tools for Si Interposer Planning?

#### Sorting out the optimization

When considering fixed components on the board, the system (chip-interposer-package-board) can be optimized from the board up

#### **Preliminary system analysis**

- When System route planning validates the route-ability of the system

- System Signal and Power Integrity can be analyzed early

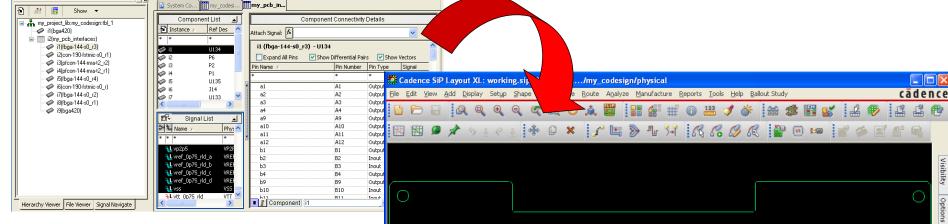

#### Hand off the Interposer plan to IC tools

IC Packaging tools can create a representation of a silicon interposer that includes die placement, TSV locations, and feasibility routing that can be transferred to an IC tool for final detailed implementation using IC Design rules

## cādence®

## **Possible Interposer Flows**

- Design completely in IC Design Tool

- Prototype in IC PKG design tool, Complete in IC Design

- Use separate databases for interposer and package

- Use one unified "substrates" database

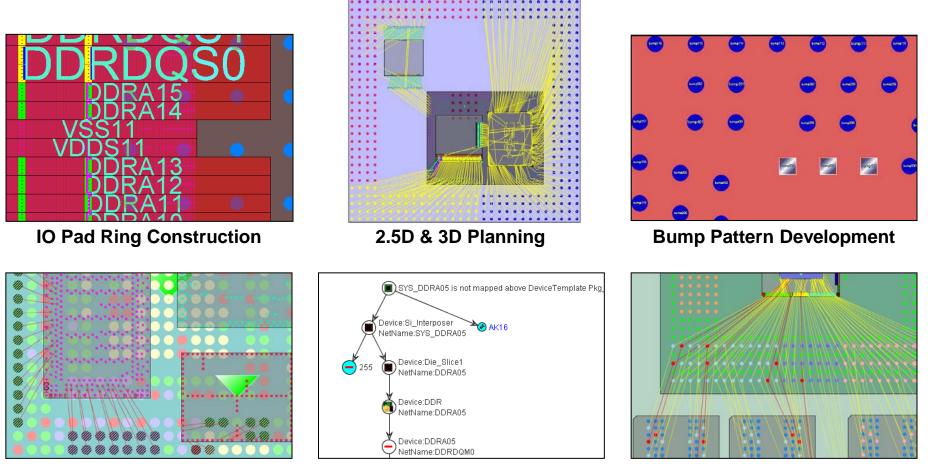

## Common Database: Design Overview

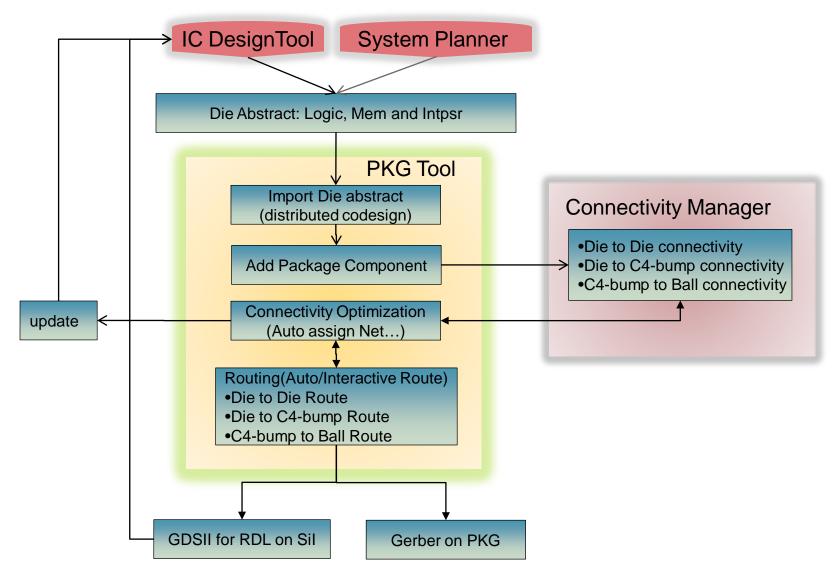

# Interposer/Package Co-design Planning Flow

11 © 2012 Cadence Design Systems, Inc. All rights reserved.

#### cādence°

# **Co-Design and System Feasibility Planning**

**Multi-Die Support**

System Connection Planning

cadence

Single Canvas Optimization of Chip-Interposer-Package-Board

# Die Abstract is Self-contained with ...

- IC technology information

- Library

- I/O drivers

- I/O pins

- Netlist

- IC Net name inherited from Verilog

- Flight line between bumps and I/O drivers

- Physical

- Bumps

- IC Cells/Pins

- Die boundary

## Connectivity Management Net management over multiple domains

| 5iP Digital Architect GXL - System Connectivity Manager - D:\Allegro_PE_Team\Product\3                        | DIC\inter\interposer_t | top.cpm - [sil_pkg [In Master]] |                            |                                 |                 |

|---------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|----------------------------|---------------------------------|-----------------|

| <u>File Edit View Project D</u> esign <u>O</u> bject T <u>a</u> ble <u>T</u> ools <u>W</u> indow <u>H</u> elp |                        |                                 |                            | cādence                         |                 |

|                                                                                                               | 🔒 1º 💣                 | D 🔢 🔉                           |                            |                                 |                 |

|                                                                                                               |                        |                                 |                            |                                 |                 |

| →→ Show ▼ Show ▼                                                                                              |                        |                                 |                            |                                 |                 |

| Component List                                                                                                | <b>_</b>               |                                 | Component Connectivity De  | tails                           |                 |

| Instance ∠ Ref Des Cell                                                                                       | i 🍾                    | Attach Signal: 🌾                |                            |                                 |                 |

| 12(logic)                                                                                                     | * *                    |                                 | 1                          |                                 |                 |

| i3(interposer)                                                                                                |                        | i1 (mem) - MEM                  | i2 (logic) - LOGIC         | i3 (interposer) - INTERPOSER    |                 |

| i2 LOGIC logic                                                                                                |                        | Expand All Pins Show Diff       | Expand All Pins Show Diff  |                                 | fferential Pair |

| i3 INTERP interposer                                                                                          |                        | Pin Name 🛆 Pin Number Sigr      | Pin Name 🛆 Pin Number Sigr | Pin Name 🛆 Pin Number           | Signal          |

|                                                                                                               |                        | * * *                           | * * *                      | *                               | *               |

|                                                                                                               |                        | clk_mem_0_CLK_MEM_0_vss         | P_A[0] FRONTBUMP           | backbump_99 BACKBUMP_99         |                 |

|                                                                                                               |                        | clk_mem_1 CLK_MEM_1 vss         | P_A[1] FRONTBUMP           | backbump BACKBUMP_105           |                 |

|                                                                                                               |                        | clk_mem_2 CLK_MEM_2 vdd         | P_A[2] FRONTBUMP           | backbump BACKBUMP_106           |                 |

|                                                                                                               |                        |                                 | P_A[3] FRONTBUMP           | backbump BACKBUMP_115           |                 |

|                                                                                                               |                        | P_A_Fro FRONTBUMP p_a           | P_A[4] FRONTBUMP           | backbump BACKBUMP_160           |                 |

|                                                                                                               |                        |                                 | P_A[5] FRONTBUMP           | backbump BACKBUMP_167           |                 |

|                                                                                                               |                        | P_A_Fro FRONTBUMP p_a           | P_A[6] FRONTBUMP           | backbump BACKBUMP_172           |                 |

| Signal List                                                                                                   |                        | P_CEB_F FRONTBUMP vss           | P_A[7] FRONTBUMP           | backbump BACKBUMP_183           |                 |

|                                                                                                               |                        | P_CEB_F FRONTBUMP vdd           | P_A[8] FRONTBUMP           |                                 |                 |

| Phys Name 🗡 Phys Name                                                                                         | # 1                    | P_CEB_F FRONTBUMP vdd           |                            | C CEB BACKBUMP 122              |                 |

| * * * *                                                                                                       | * * *                  | P_CEB_F FRONTBUMP vdd           | P_A_To FRONTBUMP p_a       | C_CLK BACKBUMP_110              |                 |

| 1L a[80] A                                                                                                    | 5                      | P CLK F FRONTBUMP vdd           |                            |                                 |                 |

| L ceb CEB                                                                                                     | 2                      | P_D_Fro FRONTBUMP p_d           |                            |                                 |                 |

|                                                                                                               | 2                      | P_D_Fro FRONTBUMP p_d           | P_CEB_T FRONTBUMP P_G      | c_q[0] BACKBUMP_178             | ••              |

|                                                                                                               | 28                     | P_D_Fro FRONTBUMP p_d           | P_CEB_T FRONTBUMP p_ct     | c_q[1] BACKBUMP_177             |                 |

|                                                                                                               | 28                     | P_D_Fro FRONTBUMP p_d           | P_CEB_T FRONTBUMP p_ct     | c_q[2] BACKBUMP_176             |                 |

| 러노 mem_stat MEM_STAT<br>하노 mse[10] MSE                                                                        | 4                      | ······                          | P_CEB_T FRONTBUMP p_ct     |                                 |                 |

|                                                                                                               |                        | P_Qbus FRONTBUMP qbu:           |                            |                                 |                 |

| 1 p_a_0[80] P_A_0                                                                                             | 17                     | P_WEB FRONTBUMP vss             | P_CEB FRONTBUMP vdd        | c_q[4] BACKBUMP_174             |                 |

| 1 p_a_1[80] P_A_1                                                                                             | 17                     | P_WEB FRONTBUMP vss             | P_CLK_T FRONTBUMP p_d      | c_q[5] BACKBUMP_173             |                 |

| 1 p_a_2[80] P_A_2                                                                                             | 17                     | P_WEB FRONTBUMP vdd             | P_CLK_T FRONTBUMP p_d      | c_q[8] BACKBUMP_170             |                 |

| 1 <u>↓</u> p_a_3[80] P_A_3                                                                                    | 17                     | P_WEB FRONTBUMP vdd 🔫           |                            |                                 |                 |

| r File V Sign                                                                                                 | 1 -                    | Component Multiple Selecti      | ion _ <                    |                                 |                 |

| ter: All Update Options                                                                                       |                        |                                 |                            |                                 |                 |

| V Status (i) 7 Object                                                                                         | 1                      | Logical Design(sil_             | nka)                       | Physical Design(sil_pkg_qbus_rd | outed aip)      |

| Component Differences (3/3)                                                                                   | I                      | Logical Design(Sil_             | huð)                       | yaida deaigin(ai_pkg_qbus_ft    | acou.oip)       |

|                                                                                                               |                        | <b>X</b>                        | 1                          |                                 |                 |

| · · · · · · · · · · · · · · · · · · ·                                                                         |                        | *                               |                            |                                 |                 |

| LOGIC#1 (logic)                                                                                               |                        |                                 |                            |                                 |                 |

| INTERPOSER#1 (interposer)                                                                                     |                        | ×                               |                            | ×                               |                 |

| Net Differences (792/792)                                                                                     |                        |                                 |                            |                                 |                 |

|                                                                                                               |                        | <u></u>                         |                            |                                 |                 |

|                                                                                                               |                        | <b>X</b>                        |                            | <b>v</b>                        |                 |

| Session Log Violations Command Window Assoc Comp Viewer Visual Design Differences                             |                        |                                 |                            |                                 |                 |

| elp, press F1                                                                                                 |                        |                                 | NUM                        | OVR                             |                 |

|                                                                                                               |                        |                                 | 1, 1,12,11                 |                                 |                 |

|                                                                                                               |                        | LVS                             |                            |                                 |                 |

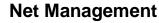

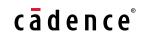

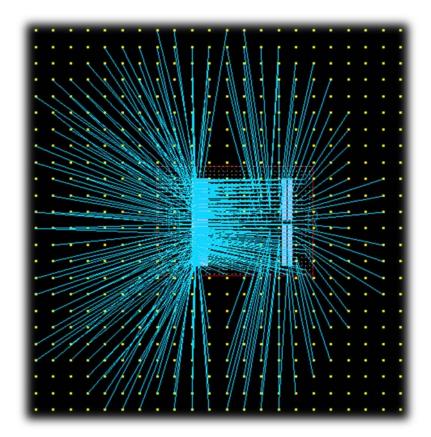

## Automatic Die micro-bump $\rightarrow$ Interposer C4-bump $\rightarrow$ Package Ball Connection Optimization

#### cādence<sup>®</sup>

# Bump and Micro-Bump Assignment Optimization

#### Before auto-assign net

After auto-assign net

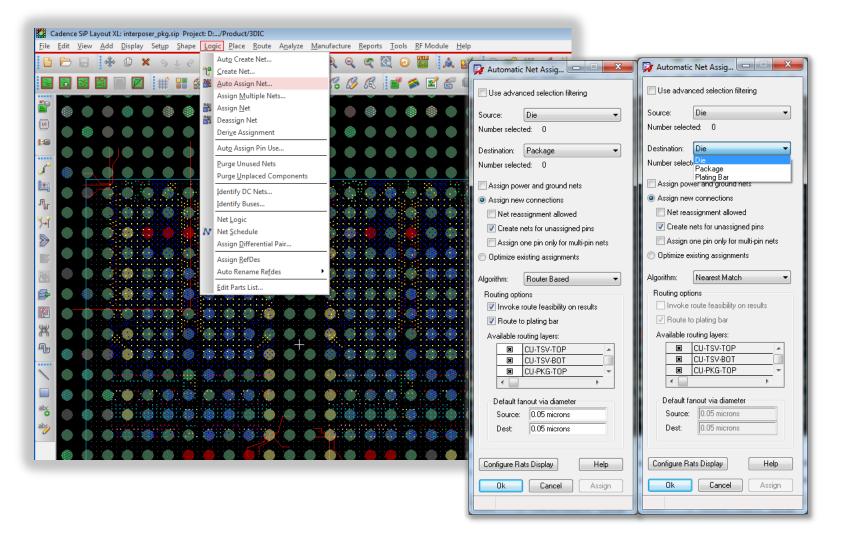

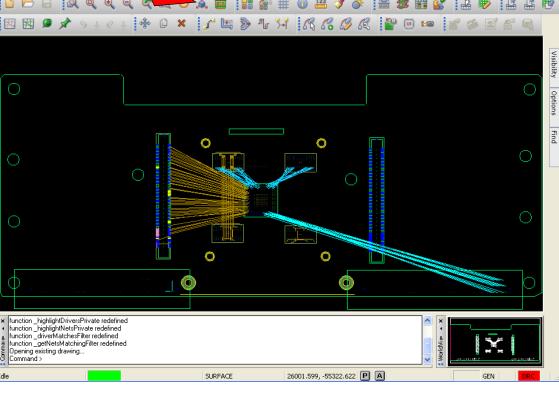

# Auto RDL Routing Feasibility

| Top su<br>Bottom<br>Concersion of the top<br>Concersion of the top<br>Concersi | Destrate Layer Config         ubstrate layer:         Image: Image |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>× Grids are drawn 16.000, 16.000 apart for enhanced viewability.</li> <li>Grids are drawn 64.000, 64.000 apart for enhanced viewability.</li> <li>Grids are drawn 256.000, 256.000 apart for enhanced viewability.</li> <li>Grids are drawn 256.000, 2864.000</li> <li>Command &gt; config substrate layers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Quick Utilities       •         Bundle Properties       •         Edit Bundle       •         Split Bundle       •         Delete Bundle       •         Insert Flow Via       •         Slide Flow       •         Insert Flow Vertex       •         Move Flow       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Copy Flow<br>Plan Optimize Plan Status Commit Plan Convert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

## cādence<sup>®</sup>

# Export Modified Bump Assignment back to IC Tool

- While optimizing bump to bump connection, micro-bump assignments in logic and memory die and C4-bump assignments in the interposer could change.

- Updated die abstract file and IO location file can be written to update floor planning in IC tool.

| 📴 Die Abstract Write                | - • • |

|-------------------------------------|-------|

| Die to write abstract for:          |       |

| INTERPOSER (interposer)             | •     |

| ☑ Die abstract (.dia or .xda) file: |       |

| interposer.dia                      |       |

| Encounter I/O update (.txt) file:   |       |

| interposer_update.txt               |       |

| Close                               | Help  |

# Export GDSII to combine RDL routing data in IC tool

| Stream Out                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Layer conversion file: 2d5IC/tutorial/PKG/gds_rdl.cnv<br>Units<br>Drawing units: microns Output precision: 1000<br>Output units: microns Scale factor: 1.0000<br>Geometry<br>Endpoints: Round<br>Output all rectangles as boundaries Flatten geometry<br>Output all rectangles as boundaries Output to Dracula<br>Output cross-hatched shapes as segment boundaries<br>Output text height as magnification | <pre># This layer conver<br/># Stream layers and<br/># class/subclasses.<br/>#[stream layer]<br/>1<br/>2<br/>3</pre> |

| Top structure name:       Sil_Top_wideid         Output file name:       WidelO_RDL         Export       Viewlog         Close       Help                                                                                                                                                                                                                                                                  | Layer mapp<br>layout tool                                                                                            |

| # This layer conversion file is used to map<br># Stream layers and their data types to SiP |             |           |            |

|--------------------------------------------------------------------------------------------|-------------|-----------|------------|

| <pre># class/subclasse</pre>                                                               | з.          |           |            |

| <pre>#[stream layer]</pre>                                                                 | [data type] | [class]   | [subclass] |

| 1                                                                                          | -1          | pin       | SiLap      |

| 2                                                                                          | -1          | via class | Siivia23   |

| 3                                                                                          | -1          | conductor | SiLap      |

|                                                                                            |             |           |            |

Layer mapping between package & IC layout tool

# Extend Co-design into a "Single-Canvas View"

- Generate netlist

- Create flat view of

- PCB

- Package/Interposer

- IC

- Optimize interfaces between fabrics

20 © 2012 Cadence Design Systems, Inc. All rights reserved.

## Chip Scale Review Article on System **Interconnect Path Optimization**

The International Magazine for the Semiconductor Packaging Industry

Volume 15, Number 2

Worldwide IC Packaging Foundries WLCSP Market Technology Solutions. Reliable Low Cost for OFNs Die Bonding in a Mobile World TSVs in MEMS Development

New integrated design process concept

- Co-Design bridging of design teams

- Creates a global view and facilitates an early identification of problem areas

- System-wide co-analysis is now possible for SI, PI and timing closure prior to die fabout

designs are "thrown over the wall," the design of all three PDNs is clearly the design is typically done by someone with right approach.

20 Chip Scale Review \* March/April \* 2011 [ChipScaleReview.com]

istorically, a semiconductor little knowledge of the overall system constraints. With such a "siloed" design, the IC package designer may be forced to deal with a die design where the padring and bump array (for flip chips) or to the next design team. Quite often, the passivation openings (for wire-bonded PCB designer is challenged with the task chips) are located sub-optimally from a rackaoing perspective. Package-level signals

routed underneath and straight across core - potentially causing signal and integrity problems - and parallel erfaces may have different routing -causing signal skew across the bus. wires may be scattered around the se footprint with little regard to return causing more problems. Differential ire also sensitive to skew.

illy, these signals should have ed physical and electrical lengths er interface speeds, there's enough margin to overcome such mismatches, th GHz+ signaling rates, there is ly no margin to correct these tches on the PCB. Signal quality, ilk, and timing are all significant 1-level challenges even with an zed package. Trying to correct the on the board of a poorly designed kage on GHz+ interface speeds is o impossible.

in power-delivery systems at the ckage, and board levels are designed tely by different design teams, there pportunity to optimize the powerry network (PDN). Lack of, or per use of package decoupling packages have a large number of layers to tors can possibly be fixed with mal PCB decoupling for slowerboard designs, but today's highsystems require far better, more ated PDN design to avoid severe blems. Separately designed PDNs PCB, package, and die levels can te some unexpected results once

electrical and physical domains. When they're coupled together. Integrated co-

Figure 1. Un-optimized connectivity between a l

package and a connector on a PCB

Integrated co-design at the die, package,

and board levels can also help reduce the IC

packaging cost. ASIC packages come in two

types: ceramic and organic. Ceramic

distribute die signals, but they cost more and

are generally single-sourced. In contrast,

cheaper organic substrates are typically

limited to fewer signal layers, complicating

number of PCB layers. Engineering teams

often find themselves up against the maximum number of layers for a given

board thickness or cost. High ASIC pin

counts complicate matters because the

There are also practical limits to the

the efforts to break signals out of the die.

**Co-Design Reduces Package Costs**

Chip Scale Review, March-April 2011 p 20

Co-design Optimizes System Interconnect Paths from ASIC to Package to Board

By Real Pomerleau [Cisco Systems, Inc.] and Carlos Moll [Cadence Design Systems]

chip and the package and

PCB that house it have all

been designed independently. One design

is completed and "thrown over the wall"

of untangling interconnect that would

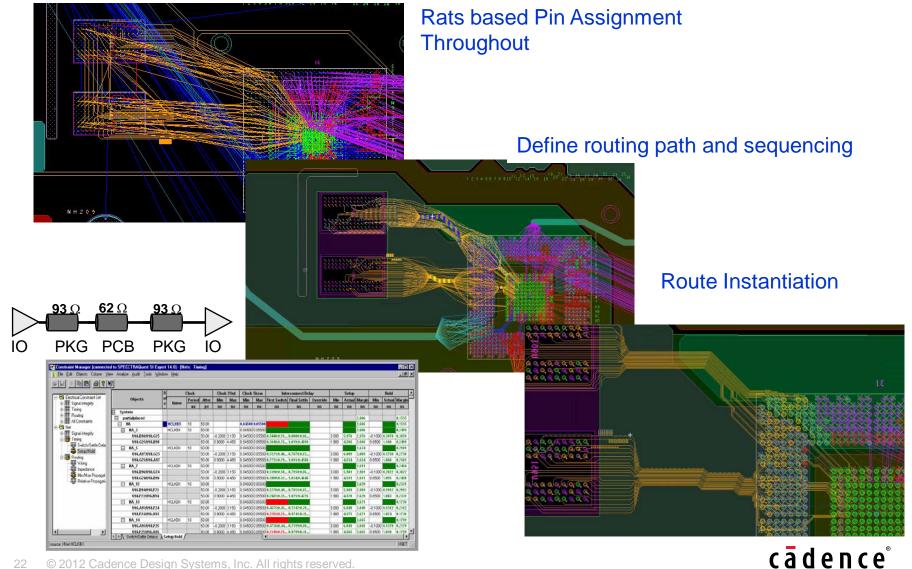

# **IC-IPSR-PKG-PCB** Optimization

© 2012 Cadence Design Systems, Inc. All rights reserved. 22

## System Planning & Single Canvas: **Complementary Solutions**

# Single-Canvas Extraction and Analysis

- Leverage SI analysis tools with common view

- Co-simulation of chip-package-board system view

- n-fabrics

- n-layers

- Board routing, package routing, RDL routing, vias

# Package-Driven Si Interposer Benefits

# cādence®