# The Future of Packaging ~ Advanced System Integration

MEPTEC Luncheon June 12, 2013 Biltmore Hotel, Santa Clara, CA

*Curtis Zwenger Sr. Director, Package Development*

Ron Huemoeller SVP, Adv. Product / Platform Development

RELIABILITY

Enabling a Microelectronic World<sup>®</sup>

#### **Product Segments**

#### **End Market % Share Summary**

| Communications<br>46%                                   | Consumer<br>22% | Computing<br>12% | Networking<br>11% | Automotive &<br>Industrial<br>9% |  |

|---------------------------------------------------------|-----------------|------------------|-------------------|----------------------------------|--|

| Smartphone                                              | Gaming          | PC / Laptop      | Server            | Infotainment                     |  |

| Tablet                                                  | Television      | Hard Disc Drive  | Router            | Safety                           |  |

| Wireless LAN                                            | Set Top Box     | Peripherals      | Switch            | Sensors                          |  |

| Note: Percentages represent share of LTM 3Q12 Not Sales |                 |                  |                   |                                  |  |

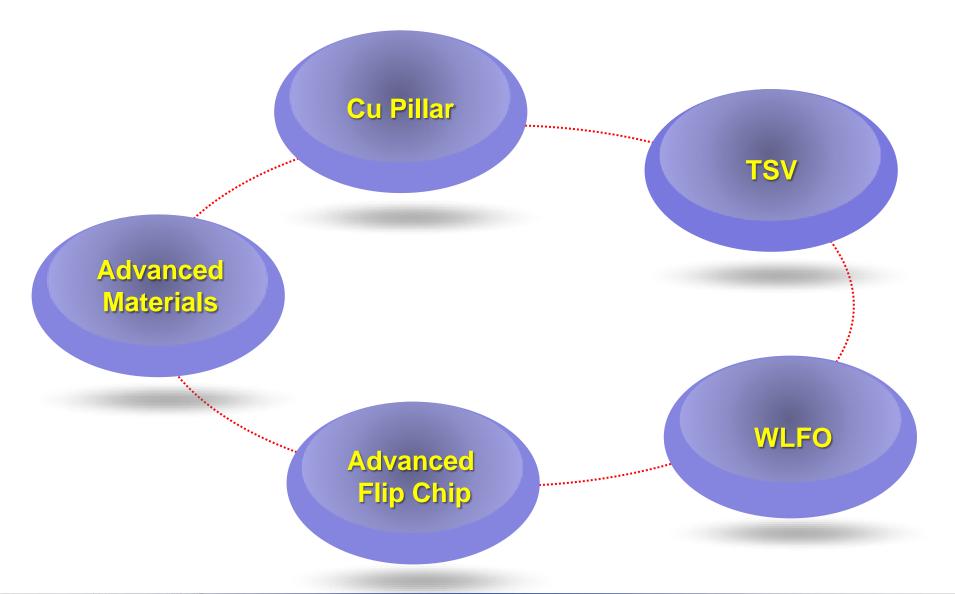

#### **New Product Technology Focus**

|                                                                        | Smartphone              | <ul> <li>Cumulative 5.3 Billion Unit Sales from 2012-2016 (18% CAGR)<sup>(1)</sup></li> <li>59% of Handsets by 2016<sup>(1)</sup></li> </ul>                                                                               | QUALCONN<br>TEXAS<br>INSTRUMENTS               |  |  |

|------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|

|                                                                        | Tablet                  | <ul> <li>Cumulative 1.1 Billion Unit Sales from 2012- 2016 (27% CAGR)<sup>(1)</sup></li> <li>2016 Tablet Traffic at 1.1 Exabytes per Month (Equal to Entire Global Mobile Network in 2012)<sup>(2)</sup></li> </ul>        | SAMSUNG<br>MICTON<br>TOSHIBA                   |  |  |

|                                                                        | Consumer<br>Electronics | <ul><li>Gaming Consoles</li><li>"Always Connected" Devices</li><li>Digital Home</li></ul>                                                                                                                                  | SONY<br>TEXAS<br>INSTRUMENTS<br>TOSHIBA        |  |  |

|                                                                        | Networking              | <ul> <li>2016 Global IP Traffic at 110<br/>Exabytes per Month (29% CAGR from 2011)<sup>(2)</sup></li> <li>2016 Global Mobile Data Traffic at 11<br/>Exabytes per Month (18-Fold Growth from 2011)<sup>(2)</sup></li> </ul> | LSI XILINX<br>BROADCOM<br>TEXAS<br>INSTRUMENTS |  |  |

| <sup>(1)</sup> Gartner, Mobile Devices Forecast Update, September 2012 |                         |                                                                                                                                                                                                                            |                                                |  |  |

<sup>(1)</sup> Gartner. Mobile Devices Forecast Update. September 2012

(2) Cisco Visual Networking Index Forecast. May 2012 and February 2012

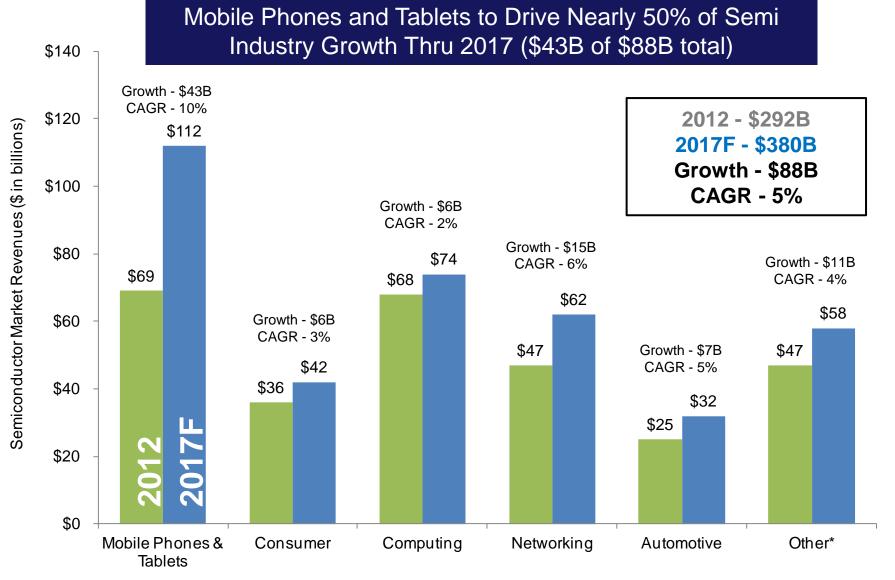

#### **Market Direction & Drivers**

Source: Prismark Partners. February 2013 \* Other includes Medical, Industrial, Military and Aerospace

# Interconnection Evolution (Wide Pitch to Fine Pitch)

#### Standard Solder Flip Chip

- Typically uses electro plated bumps redistributed in an <u>area</u> <u>array format</u>

- Mass reflow bonding

- Suited for High I/O, High Power, Very high speed, High thermal applications

#### Wide Pitch Cu Pillar Flip Chip

<u>Utilizes</u> common wafer bumping <u>infrastructure</u>

- Alternative to Standard Solder FC

- <u>Mass reflow or thermal compression</u> bonding capability

#### Fine Pitch Au Stud

Primarily developed and used in Japan

- Stud typically applied with a modified wire bonder, formed directly on the Aluminum bond pad

- Thermal sonic or compression bonding

- Stand-off defined by bump height

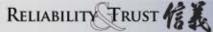

#### Fine Pitch Cu Pillar

Compatible with standard wafer level process technologies (200/300mm)

- Bump redistribution not required

- Adaptable from wirebond designs

- Less costly for high bump densities due to the wafer level bump process

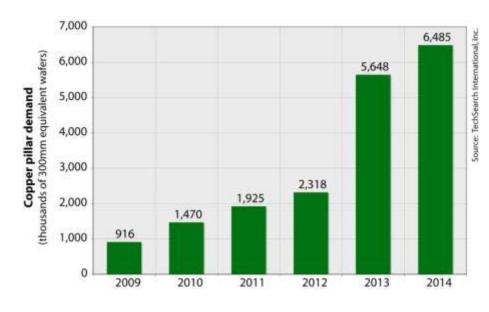

### Interconnection : Fine Pitch Cu Pillar

#### **Copper Pillar Platform**

- Fine pitch CSP

- ✓ Area array fine pitch BGA

- ✓ µBump F2F TSV

#### **Production Status**

- HVM since Q2 2010

- ✓ 40/80um 3-row CuP pitch

- 28/22nm under development

- Bonding method : TC/NCP, TC/CUF, TC/NCF  $\checkmark$

8

Jun-13

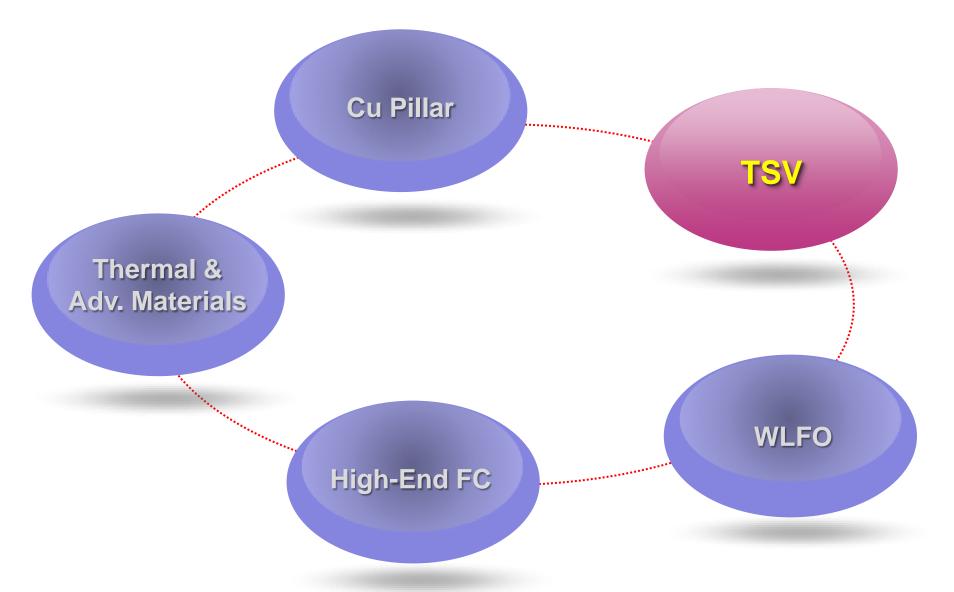

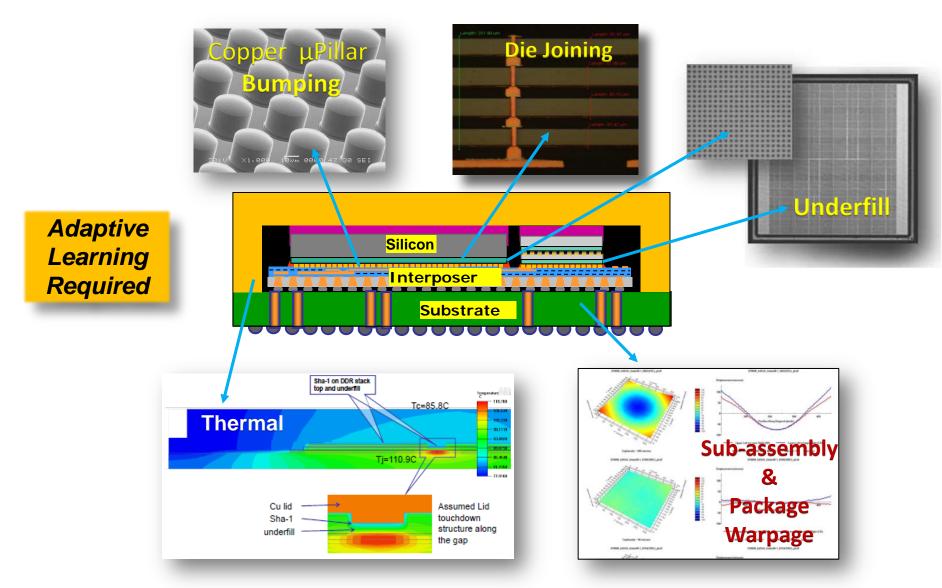

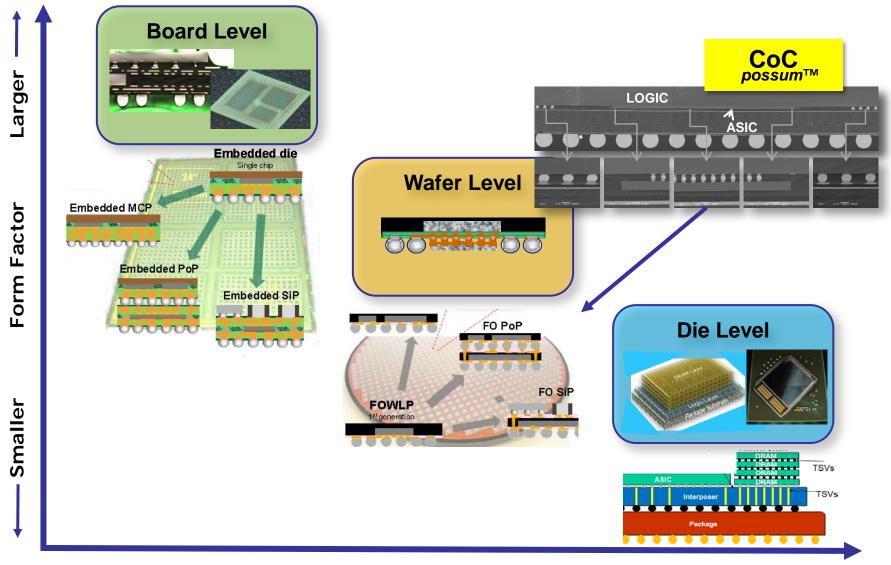

### Integration : Through Silicon Via (TSV)

#### Current Status

- World's first production of fully integrated TSV package platform completed

- "Logic dies on Si interposer" product is being produced

- ✓ Large number of customers engaged in active TSV development

- ✓ Target devices

- Logics on Si interposer

- Logics + memories on Si interposer

- Memory / Memory stack

- Memory / Logic combination

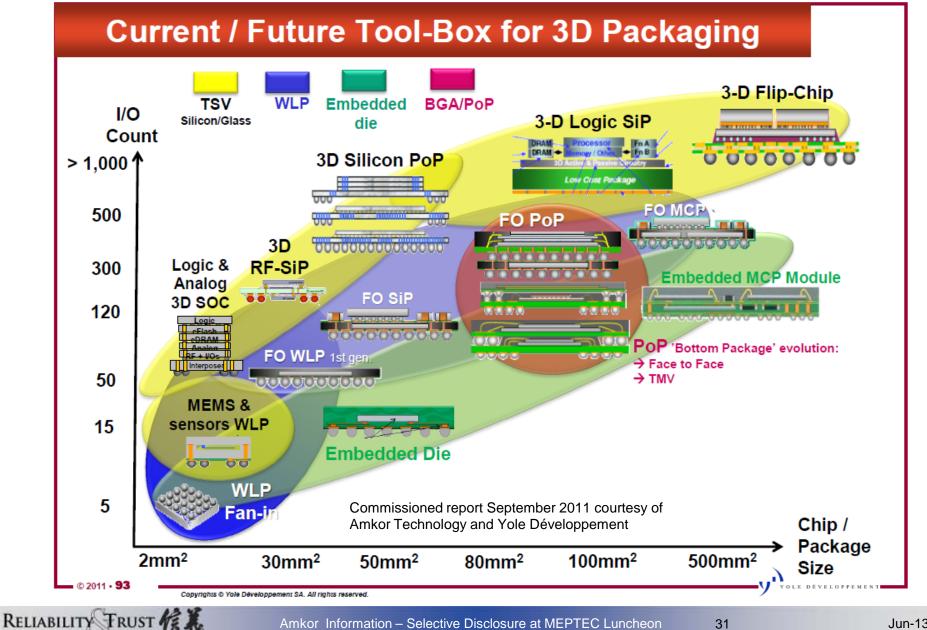

### 2.5D MCM Interposer Supply Chain

- High End Products : Networking, Servers

- Silicon interposers ; < 2um L/S, < 15nsec latency, > 25k µbumps per die

- Several foundries delivering silicon interposers today

- Others in consideration of adding capability to make use of unused assets

- Mid Range Products : Gaming, Graphics, HDTV, Adv. Tablets

- Silicon or Glass interposers ; < 3um L/S, < 25nsec latency, ~10k</li>

µbumps/die

- Glass <u>may</u> provide cost reduction path in future

- Glass interposers infrastructure still immature, but improving

- Lower Cost Products : Lower End Tablets, Smart Phones

- Silicon, Glass or Laminate interposer ; < 8um L/S, low resistance, ~2k</li>

µbumps

- Must provide cost reduction path to enable this sector; thick copper traces

- No laminate substrate ; So don't underestimate the reach & desire of the organic substrate manufacturers to survive

#### Memory

- Sources

- End customer choosing memory supplier

- 2 different sources today Elpida (Micron) & Hynix

- Logistics

- Plan is to receive memory as 'KGM' on tape and reel

- Activity

- Multiple programs in progress with stacked memory in wide I/O format

- Shipping single die, 2 die stacks and 4 die stacks

- Most development being completed with single memory in wide I/O

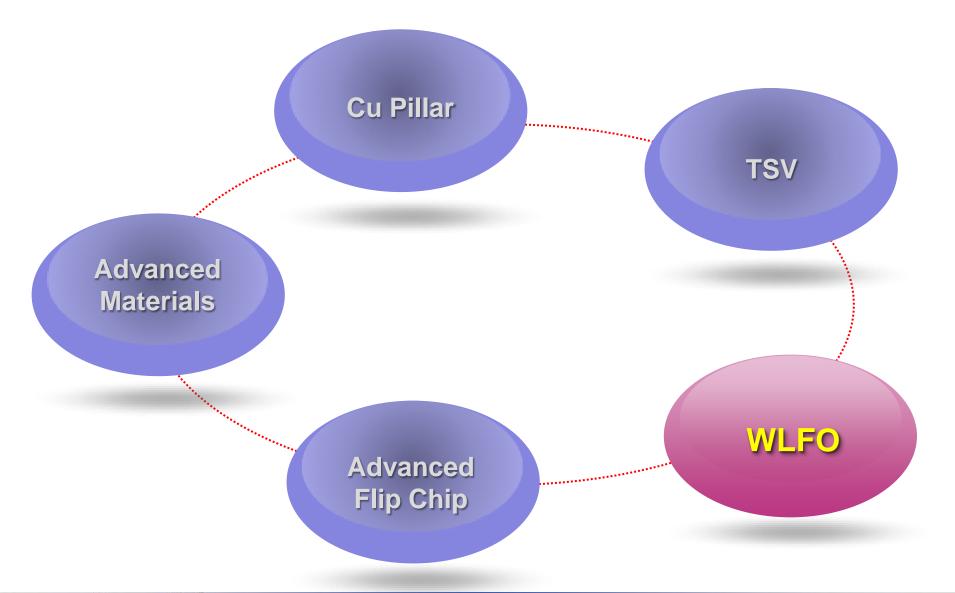

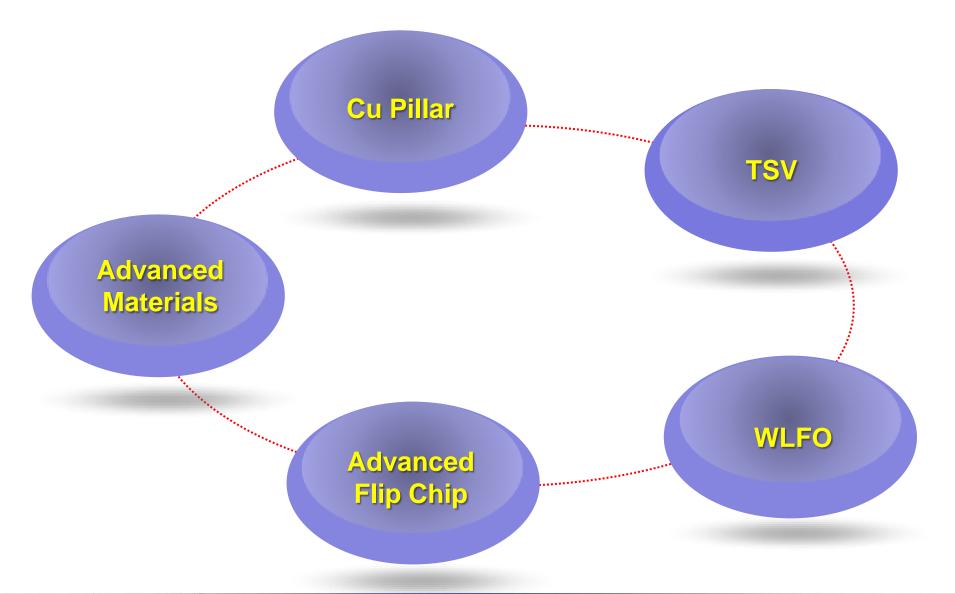

# Advanced Platform : Wafer Level Fan Out (WLFO)

- WLFO is now established as a viable alternative to conventional laminate-based and wafer-based packages

- The elimination of a conventional laminate substrate and utilization of wafer-level packaging's superior design and feature size capabilities provide many benefits for WLFO, including:

- Increased I/O density

- Reduced form factor (including z-height)

- Improved electrical and mechanical performance

- Multi-chip capability

- Outstanding cost/ performance capability

- Scalability within a heterogeneous assembly platform

- Opportunity for advanced 3D structures

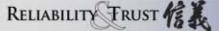

#### Wafer Level Fan-Out Revenue Forecast

• WLFO reached the \$100M market valuation in 2011

RELIABILITY TRUST

Predicted by Yole to reach \$250M market valuation in the 2015/16 timeframe once demand moves from IDMs to fabless wireless IC players and the OSAT supply chain expands

### Wafer Level Fan-Out Wafer Forecast

#### Breakdown by IC type (12"equiv wafers)

- Yole's wafer forecast model predicts 30% CAGR in the 2010-2020 time frame, leading to a ~ \$1B market in 2020

- This equates to nearly 500,000 wafers shipped in 2015 and more than 2.8 billion shipped in 2020

- Time will tell if the infrastructure for this emerging package technology will be strong enough to support this anticipated demand

RELIABILITY TRUST

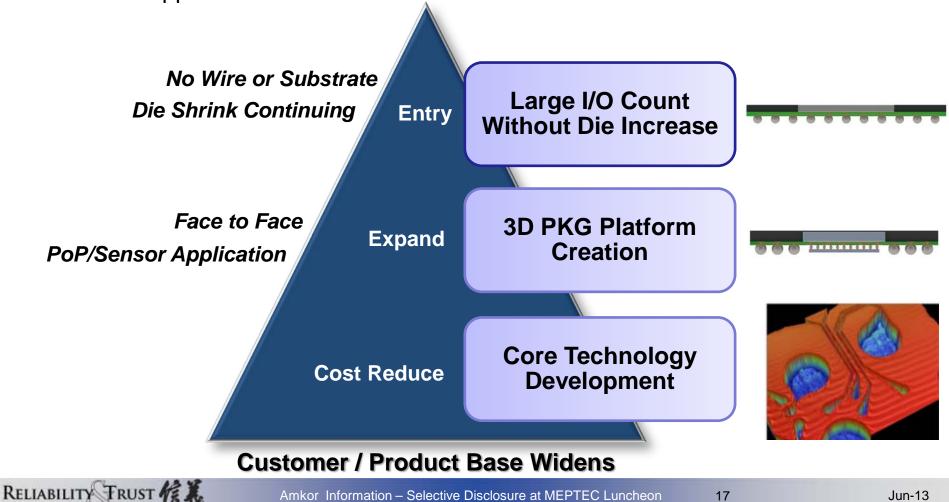

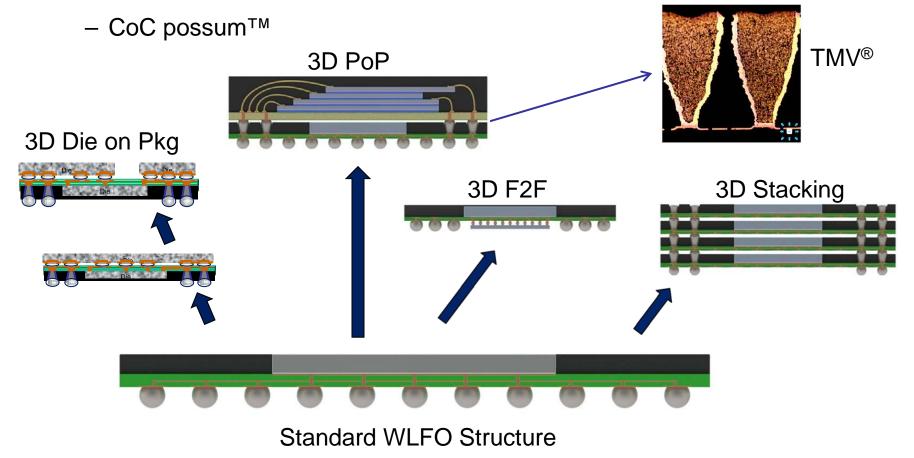

### Advanced Platform : Wafer Level Fan Out (WLFO)

#### Customer Interest

Hybrid Packages, RF Connectivity, Audio modules & Sensor Applications

### **Evolution of WLFO**

- Key enabling technologies for extensions into 3D

- Thru Mold Via (TMV<sup>®</sup>)

- Fine pitch copper pillar

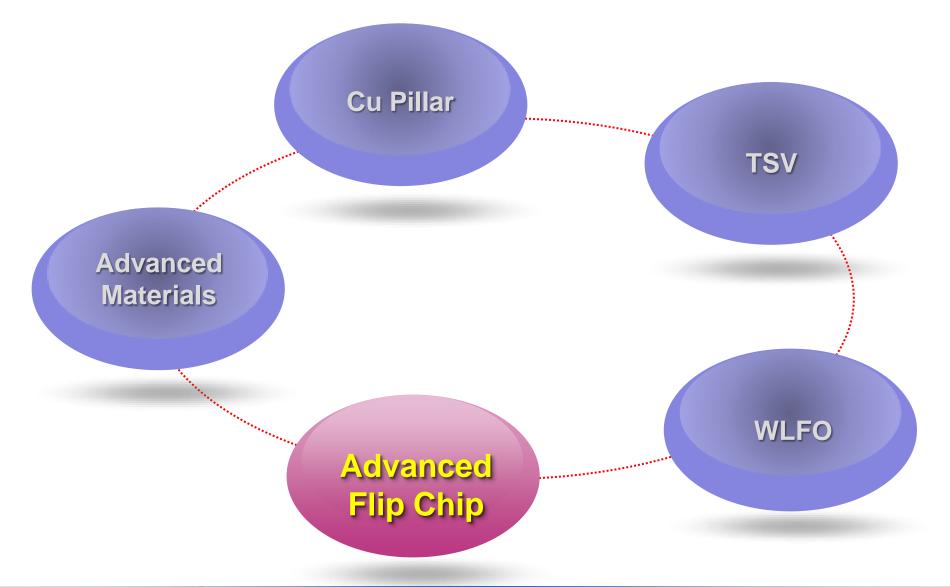

# **Advanced Flip Chip Continuing to Drive Growth**

- Migration to Flip Chip, 3D and Advanced Packaging Continues to Accelerate

- Driven by Strong Demand for Smartphones, Tablets, Gaming Devices, Network Infrastructure

- Enhances Device Performance, Reduces Power Consumption and Form Factors

- Higher Gross Margin and Returns Versus Wirebond

### **High Performance Flip Chip**

#### • Industry Direction

- ✓ Increasing body size (>55mm BD)

- ✓ Increasing die size (>26mm)

- ✓ 32/28nm in production with 20nm qualification in progress

- ✓ Cu Pillar to enable density / pitch below 150um bump pitch

- ✓ Coreless substrates in use for 32/28nm

- ✓ Multiple die per package .... With die count continuing to increase

#### **Advanced FC Packages : Chip on Chip**

- Next Generation of FC CoC<sub>POSSUM</sub>

- MEMs, Automotive, Networking

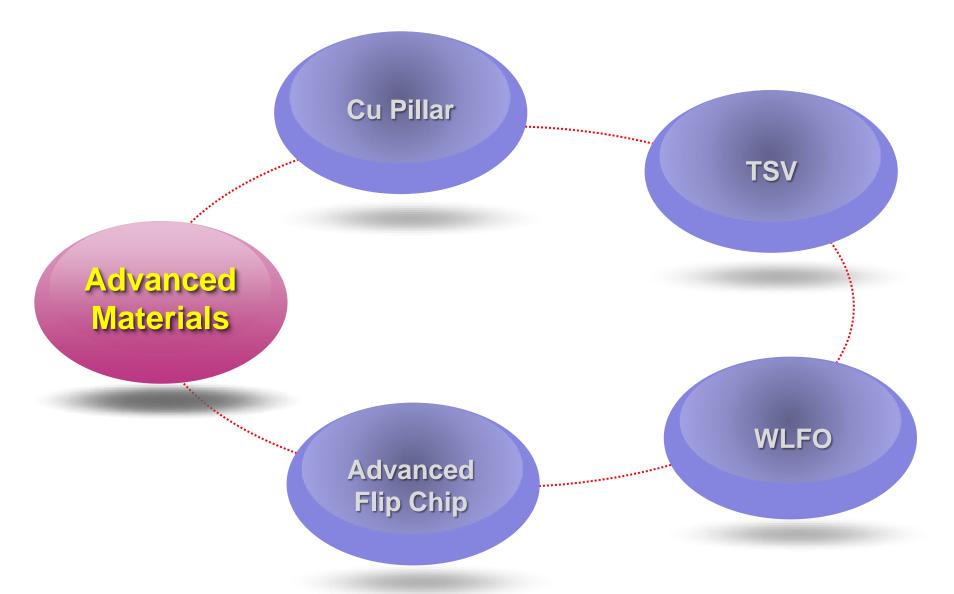

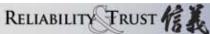

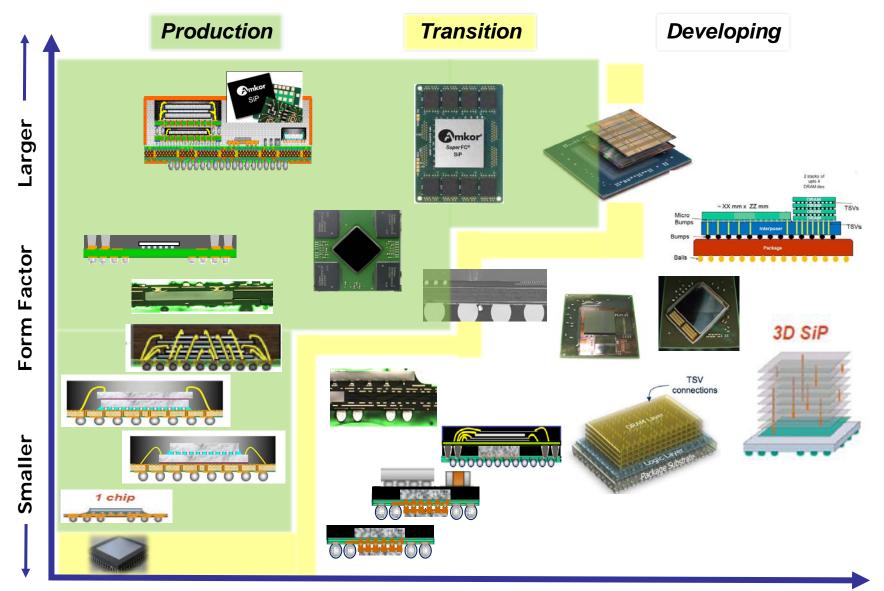

### Advanced Packaging & Technology Integration

### **Amkor Advanced Package Integration**

#### Interconnect Density & Functionality : Increasing

Amkor Information – Selective Disclosure at MEPTEC Luncheon

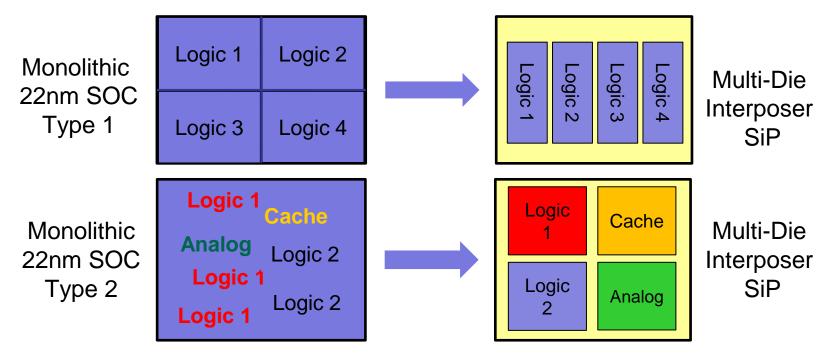

#### **Package Migration to SiP - MCM Integration**

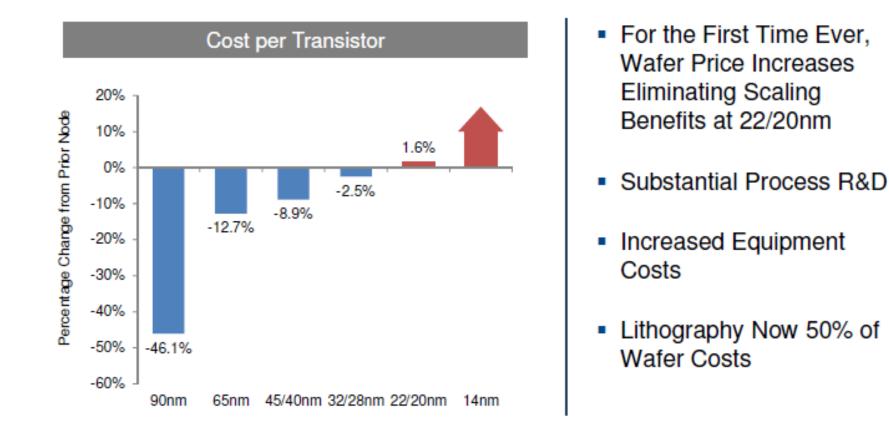

### **Advanced Silicon Nodes Driving Higher Costs**

#### Use Advanced Packaging to Minimize or Reduce the Number of Layers of Circuitry that Need to Be Created on the Wafer

Sources: IBS and Nvidia

# SOC to 2.5D TSV MCM SiP Drivers

Focus Process Node Development on Specific Application Functionalities

- Reduces complexity and mask layer count of process node

- ✓ Improves wafer yield

- ✓ Reduces wafer start cost

- ✓ Improves performance, power, and area of each application

### Industry Advanced Package Integration Roadmap

### Amkor Advanced Package Integration Roadmap

#### Interconnect Density & Functionality : Increasing

Amkor Information – Selective Disclosure at MEPTEC Luncheon

Enabling a Microelectronic World<sup>®</sup>