**STATSChi**

# eWLB: A Transformative Fan-out Packaging Technology for High Performance, Integration and Small Form Factors

Dr. Raj Pendse VP, Product & Technology Marketing, STATSChipPAC

# Outline

#### Introduction to eWLB

- Package Performance and Reliability

- 2<sup>nd</sup> Generation eWLB Technology

- Fine pitch and escape routing

- Thin eWLB

- Double sided & 3D eWLB

- 2.5D Heterogeneous Integration

- Extreme Small eWLB

- Large Panel Processing

- Summary & Conclusions

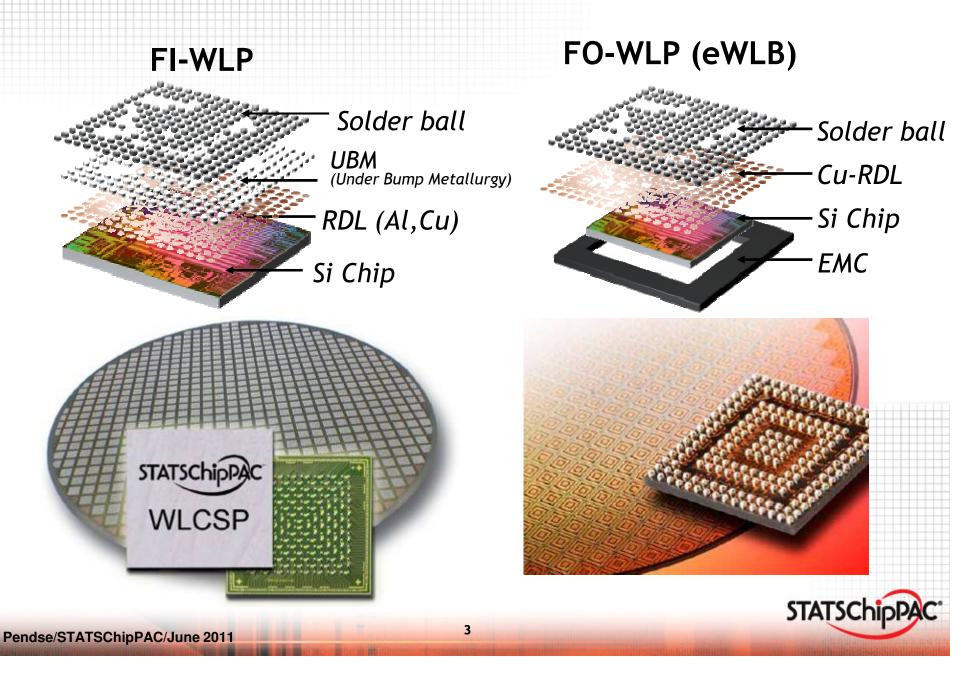

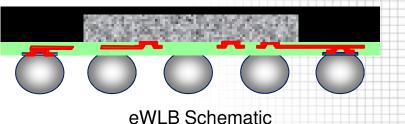

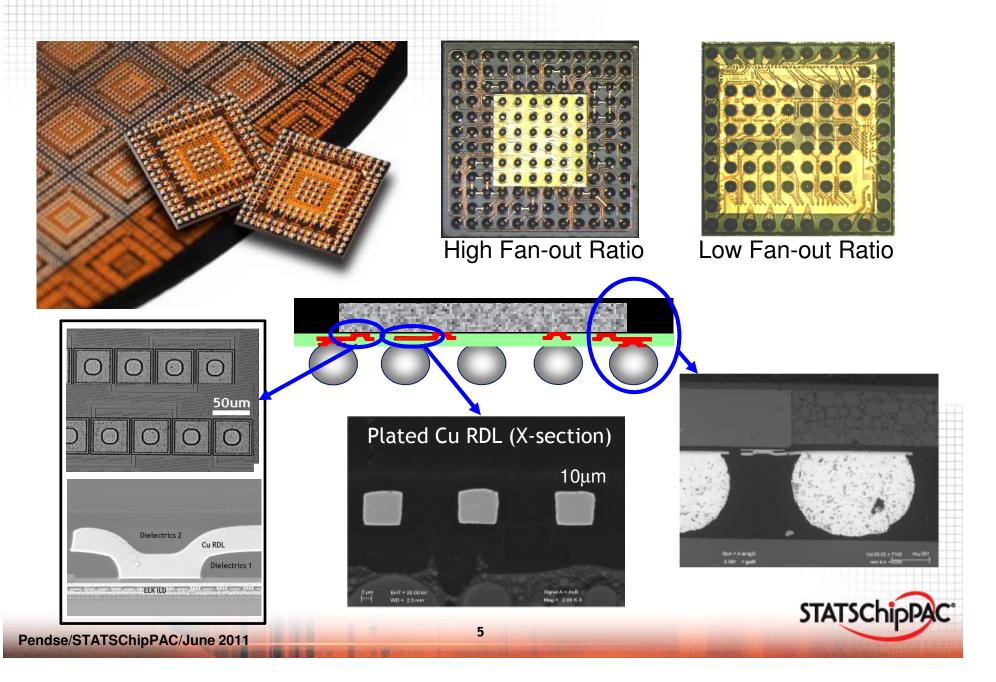

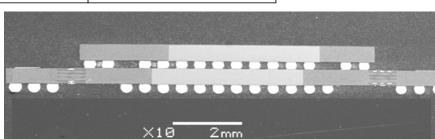

## **Package Structure**

## **eWLB** Process

- 1) <u>Reconstitution</u> of dies to "artificial" wafer

- ⇒ Single die or several (different) dies, actives and passives

- ⇒ Usage of FE-tested-good-dies (yield)

- ⇒ Materials well-known in BE technology

- ⇒ Molded artificial wafer is starting point for thin film technology

#### 2) <u>Redistribution</u>

- ⇒ Using thin-film-technologies

- ⇒ Using standard thin-film equipment

- ⇒ Using commercially available materials

#### 3) Ball Apply and Singulation

Standard backend assembly flow (and equipment)

#### 4) Test, Mark, Scan, Pack

- ⇒ Standard or wafer level based test flow

- ⇒ Standard assembly

# **Typical Package Structure**

# Performance & Reliability

## **High Electrical Performance**

|                              | fcFBGA           | eWLB        |  |

|------------------------------|------------------|-------------|--|

| PKG size (mm2)               | 11x11            | 10x9        |  |

| Die Size (mm2)               | 7.5x7.0          | 7.5x7.0     |  |

| Substrate<br>Thickness/Layer | 0.18mm / 2-layer | 1-layer RDL |  |

| Ball Count                   | 477 I/O          | 508 I/O     |  |

| Ball Pitch                   | 0.50 mm          | 0.40 mm     |  |

#### **Electrical Characterization** 2.5 2.0 R, Resistance (Ohm) **C Values** L, Inductance (nH) C, Capacitance (pF) **fcBGA** eWLB \_\_\_ ℃ 0.5 Solder bump + substrate **RDL** metal line metal line + substrate via + Solder ball + Solder ball fcBGA eWLB eWLB shows lower values of RLC electrical parasitics compared to fcBGA, due to short/removed interconnection. **STATSChipP**

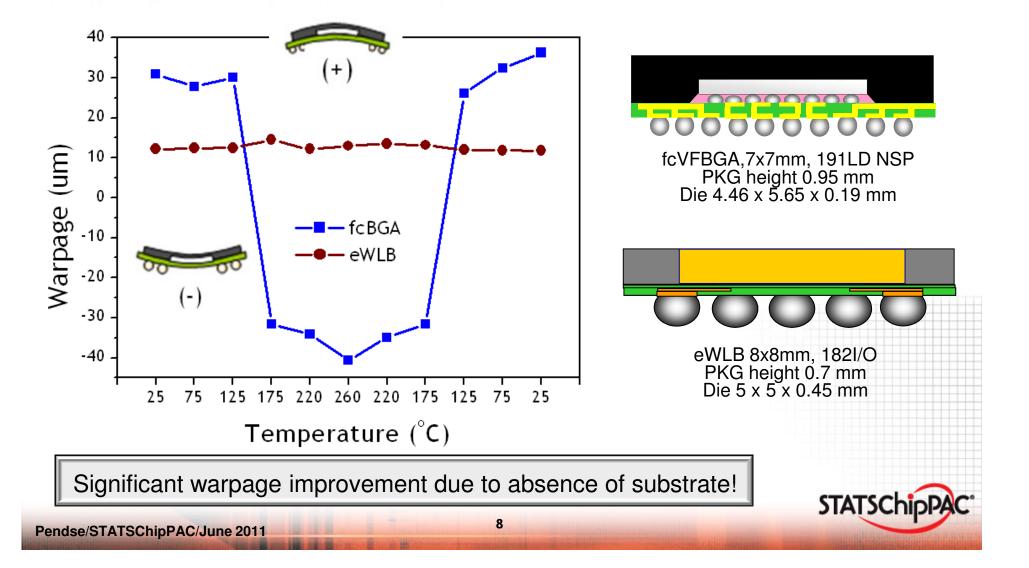

#### Low Warpage

#### • Std single-sided (1S) eWLB (Shadow Moiré data)

STATSChipPAC

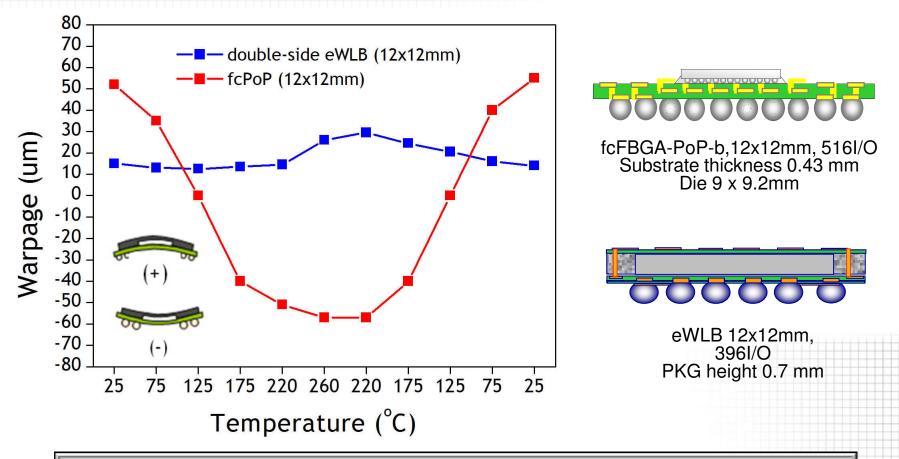

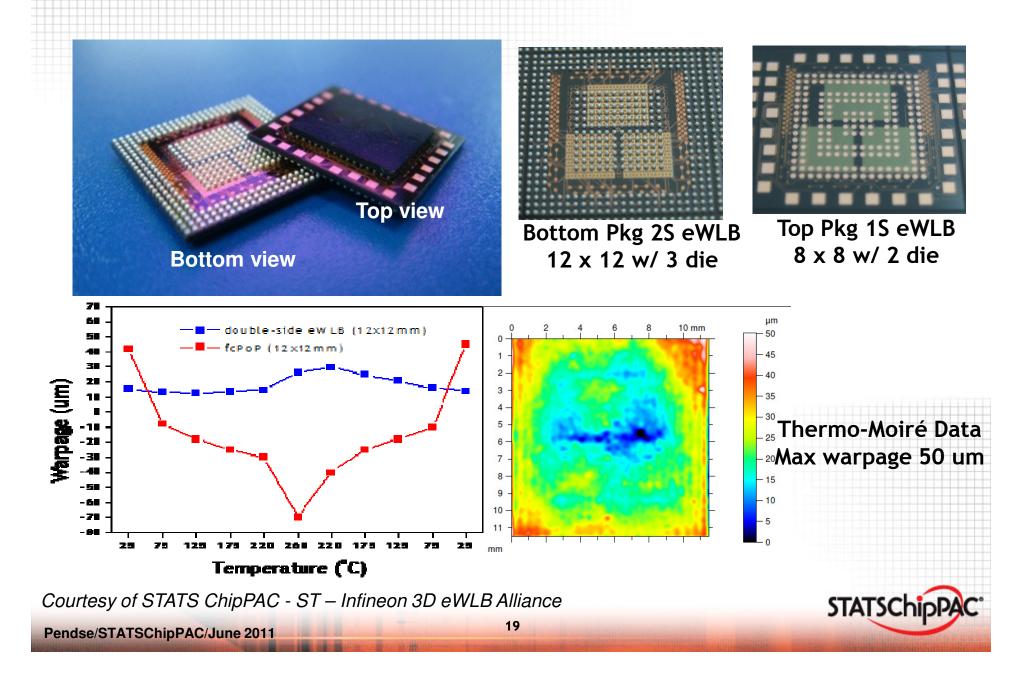

#### Low Warpage

#### • Double-sided (2S) eWLB

Dramatic improvement in warpage in 2S –eWLB lends itself to application to thin PoP solution for Mobile platforms

STATSCh

### **Component-level Reliability**

- Different package configurations

- Std 1S 1L eWLB, 5x5 mm die, 8x8 mm body

- Thin eWLB (250um Si thickness, 5mm x 5mm die , 8mm x 8mm body)

- 1S 2L eWLB (5mm x 5mm die, 8mm x 8mm body)

- Multi-Chip eWLB (two-chip, 5x2.5mm, 8mm x 8mm body)

| Test              |                                                      | Conditio                  | n     | Status                     |  |

|-------------------|------------------------------------------------------|---------------------------|-------|----------------------------|--|

| Package<br>Level* | MSL1<br>JEDEC-J-STD-020D                             | MSL1, 260C<br>Reflow (3x) | -     | Pass                       |  |

|                   | Temperature Cycling (TC) after Precon<br>JESD22-A104 | -40C to 125C              | 1000x | Pass;<br>some legs ongoing |  |

|                   | HAST (w/o bias) after Precon<br>JESD22-A118          | 130C / 85% RH             | 96hrs | Pass                       |  |

|                   | High Temperature Storage (HTS)<br>JESD22-A103        | 150C                      | 1000h | Pass                       |  |

|                   | BST after Multiple Reflow                            | 260C Reflow               | 20x   | Pass                       |  |

\* Tested for continuity (Open/Short) and mechanical integrity e.g. ball shear, package cracking etc

Courtesy of STATS ChipPAC - ST – Infineon 3D eWLB Alliance

-1-L eWLB -2-L eWLB -Thin eWLB -Multi Die eWLB -XL eWLB

STATSChip

Temperature Cycles

## Board-level Reliability (BLR)

| Board Level Reliability Test |                   |      |              |  |

|------------------------------|-------------------|------|--------------|--|

|                              | NOKIA             | Spec | 100          |  |

|                              | ТСоВ              | Drop | ()           |  |

|                              | -40/125C,2cyc/hr, |      | Rate (%)     |  |

|                              | 8-layer PCB       |      | Rat          |  |

| 2-RDL                        | Pass              | Pass | Failure 10   |  |

| Thin eWLB                    | Pass              | Pass |              |  |

| Multi Die                    | Pass Pass         |      | Accumulative |  |

| X-Large eWLB                 | Decc*             | Dage | nur          |  |

| (12x12mm)                    | Pass*             | Pass | Acci         |  |

| X-Small eWLB                 | Dage              | Dage | 1            |  |

| (2.7x2.7mm)                  | Pass              | Pass |              |  |

\* With larger ball pad size / FSP

Courtesy of STATS ChipPAC - ST – Infineon 3D eWLB Alliance

## eWLB Technology Roadmap

|                 | Itom                    | Current |       | 2011   |                      | 2042   |  |

|-----------------|-------------------------|---------|-------|--------|----------------------|--------|--|

| Item            | Current                 |         | 1H    | 2H     | 2012                 |        |  |

| •               | Max. Package size (mm)  | 8x8     | 10x10 | 12x12  |                      | >12x12 |  |

| eWLB<br>Package | PKG height w/ ball (mm) | 0.7     |       | 0.5 🔍  | 0                    | .4     |  |

|                 | Min. Ball pitch (mm)    | 0.5     |       | 0.4    | 0                    | .3     |  |

| eWLB<br>Routing | Min. RDL LW/LS (um)     | 15/15   |       | 10/10  | 8/8                  | <8/8   |  |

|                 | Die pad pitch (um)      | 75um    | 65um  | 60um 🤇 | 50um                 | <50um  |  |

|                 | RDL layer               | 1       |       | 2      | >                    | 2      |  |

|                 | Die No. in Package      | 1       | 2     | 3      | >3                   |        |  |

|                 | 3D Approach             |         |       | <      | PoP, SoW, SiP module |        |  |

| eWLB Mfg        | Carrier Size            |         |       | 8",12" |                      | Panel  |  |

HVM !

- Std 1S 1L eWLB in HVM (high vol manufacturing).

- New technology development in fine pitch 1<sup>st</sup> level interconnect (sub-50 um), 2L/2.5D, 3D and super-thin implementations

# 2<sup>nd</sup> Generation eWLB Technology

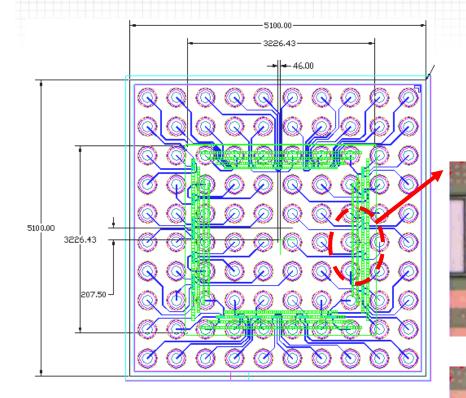

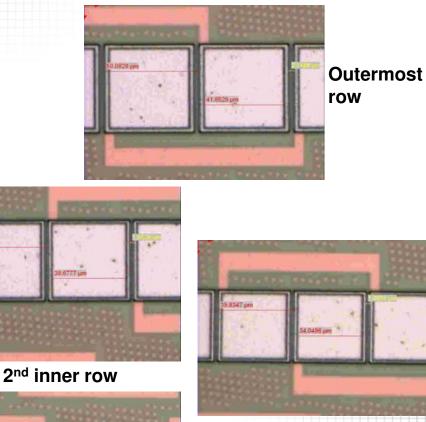

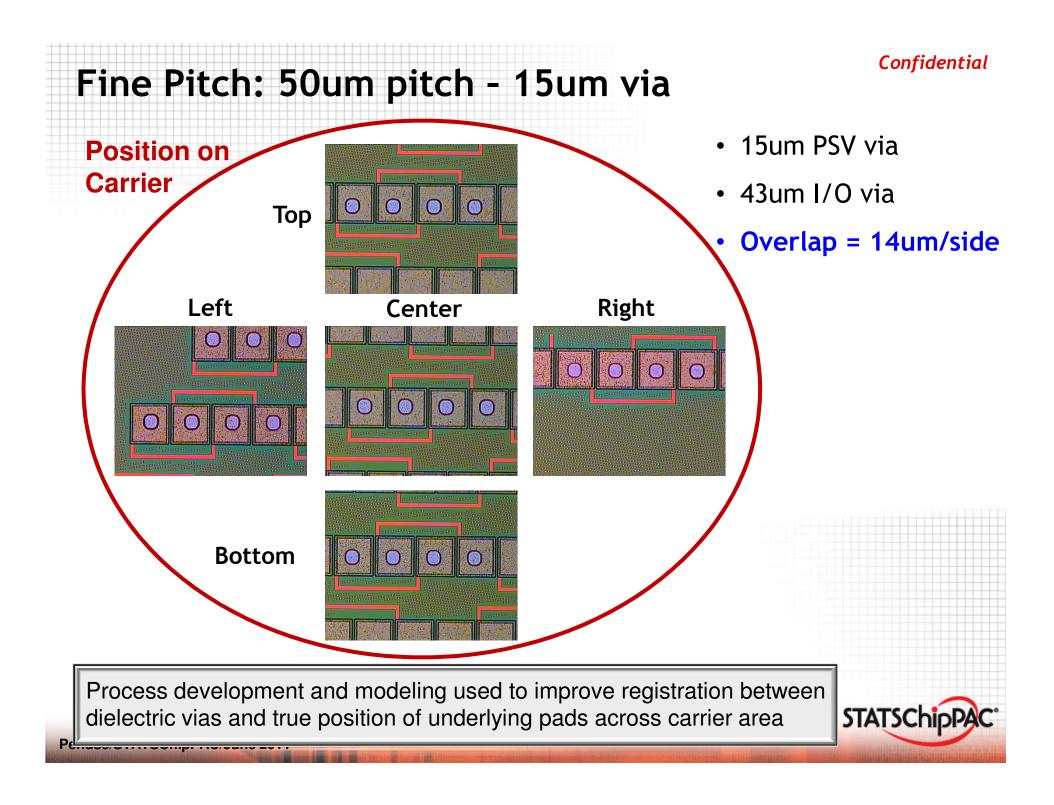

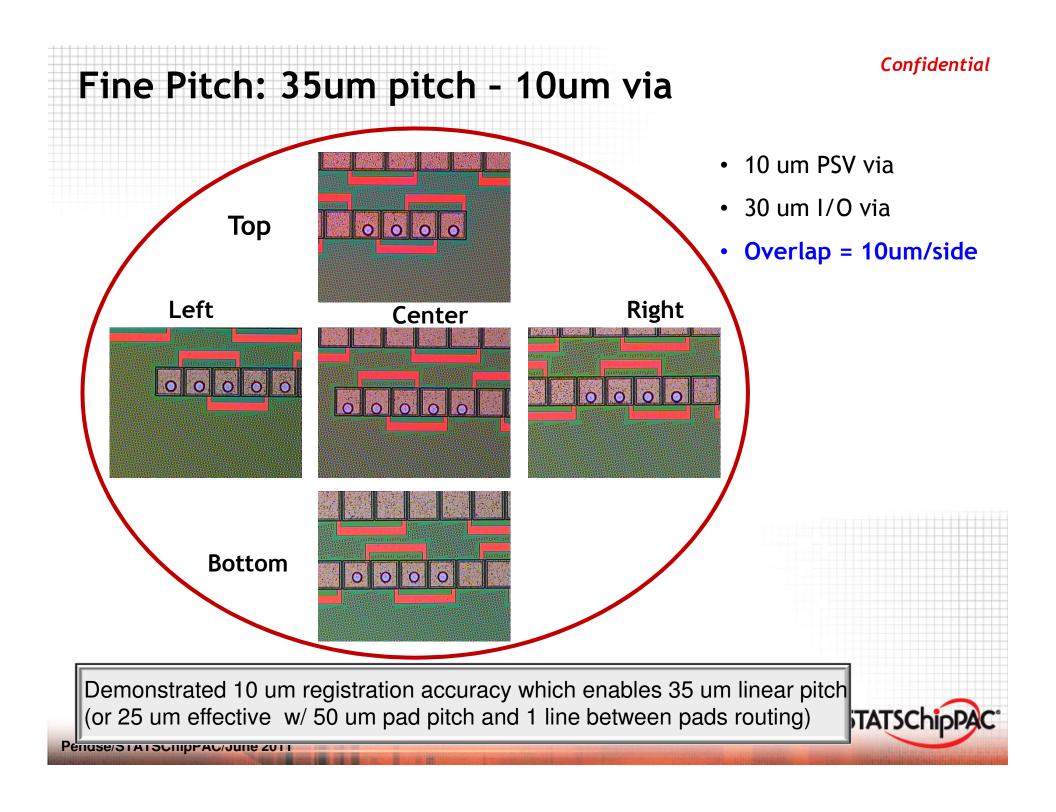

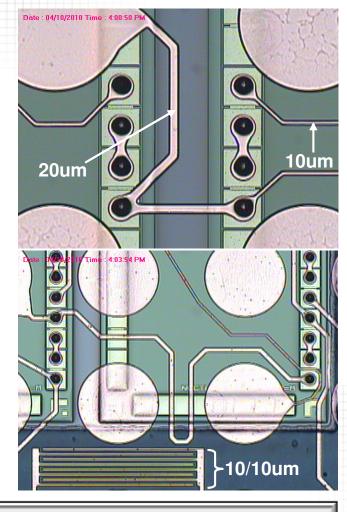

# **Fine Pitch: Sub 50um pitch 1<sup>st</sup> level Interconnection**

Innermost row

14

#### Test Vehicle Features

- Outermost row pitch 50um

- 2<sup>nd</sup> inner row pitch 45um

- 3<sup>rd</sup> inner row pitch 40um

- Innermost row pitch 35um

3<sup>rd</sup> inner row

Pendse/STATSChipPAC/June 2011

**JIAIJUNIOP**

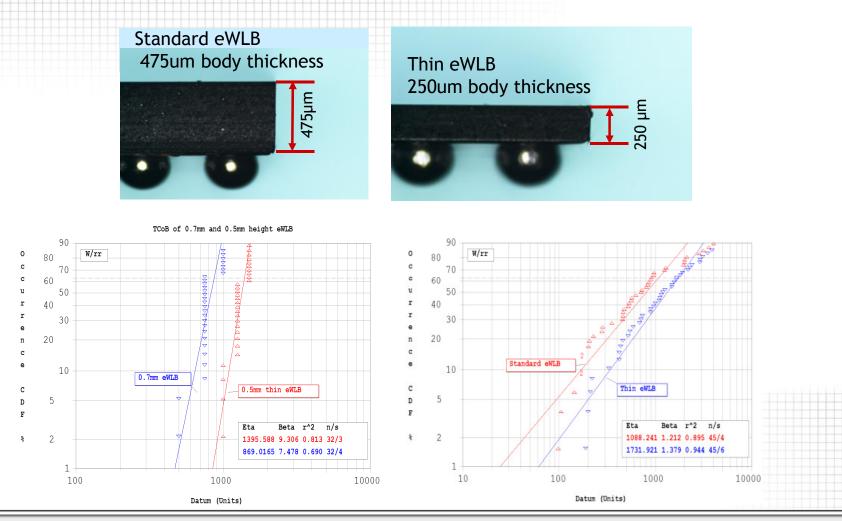

# Thin eWLB Solution

Super thin profile eWLB package developed for mobile applications

Superior BLR reliability by virtue of mechanical compliance of package body

**STATSChipP**

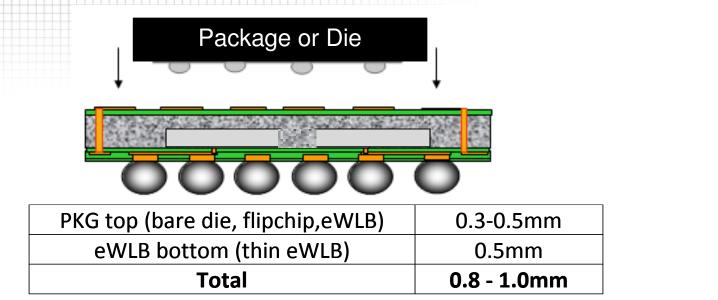

## 2S - eWLB for 3D Packaging

Courtesy of STATS ChipPAC - ST – Infineon 3D eWLB Alliance

- Breakthrough in density, performance and form factor !

- Provides compelling benefits for PoP packaging by virtue of sub-1.0 mm mounted height (PoPb + PoPt) and dramatic reduction in pkg warpage

### 2S eWLB for 3D Packaging

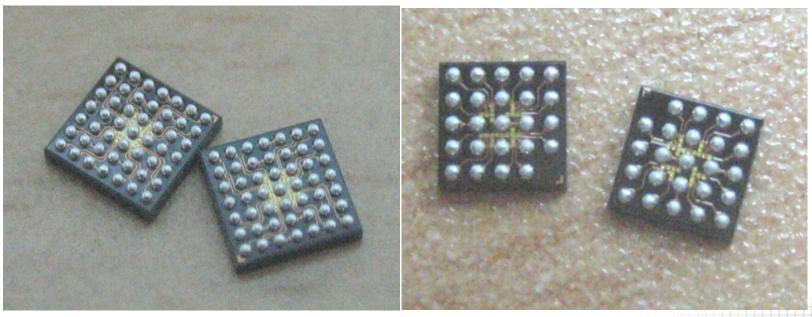

#### **Extreme Small eWLB**

Extreme-small, 3.2x3.2mm eWLB 0.4mm (1x1mm die)

**Extreme-small**, 2.7x2.7mm eWLB 0.5mm (1x1mm die)

Courtesy of STATS ChipPAC - ST – Infineon 3D eWLB Alliance

- eWLB becomes progressively cost effective w/ body size reduction by virtue of economics of wafer-scale manufacturing

- "Extreme small" family competitive with FBGA, QFN of comparable pin counts and WLCSP w/ FR (fan-out ratio) of ~ 1 requiring die shrink

- Land grid versions ("eWLL") under development for ultimate in low cost

STATSChip

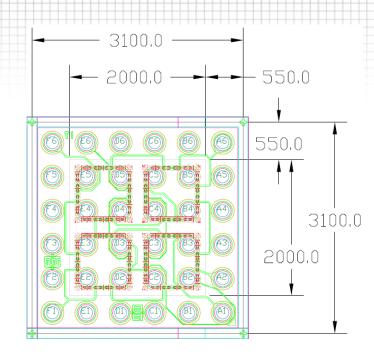

## **Extreme Small eWLB**

Die size – 2mm x 2mm Package size – 3mm x 3mm

3.1 x 3.1 mm eWLB passed MSL1, TC1000X, UHAST, High temperature storage, bend, TCoB, drop reliability tests

### **Extreme Small eWLB**

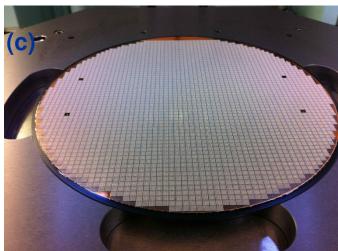

(a) after pick & place(b) after molding(c) after back end

- ~ 3000 eWLB units / 200 mm carrier

- ~ 7000 eWLB units / 300 mm carrier

## Summary

- There is an increasing trend towards Wafer level Packaging approaches over traditional substrate based solutions driven by increasing I/O densities beyond the 10-20 I/O /mm<sup>2</sup> range, associated with the advent of sub-40nm Si nodes; Fan-out packaging (eWLB) provides an appealing solution.

- eWLB technology is a mature, production proven packaging solution that presents a broad platform of offerings ranging from single sided, single layer structure to advanced 2.5D and 3D heterogeneous integration platforms with compelling advantages in performance and thin profile unattainable with traditional packaging

- eWLB adoption is poised to expand from the current application space of Mobile base-band and RF Transceiver products to

- i. 2.5D and 3D heterogeneous integration in mid range computing systems (Computers, Tablets) at the high end, and

- ii. Ultra-small Analog/Power packaging at the low end

This expansion will be further aided by new paradigms in manufacturing technology such as large panel carriers which are currently in development

# **Thanks!**

Questions Welcome