A Quarterly Publication of The Microelectronics Packaging & Test Engineering Council

Volume 16, Number 4

Mala

Straten

# SEMI-THERM® EXECUTIVE BRIEFING: **Thermal Management Market Visions & Strategies**

page 17

In Association with

EFING: G agement Mark Marker iloo & Strateg In Association with MEPTEC & Electronics Cooling Magazine

Like several other Silicon Valley success stories, Altera Corp. emerged from a legendary primordial broth: alumni of Fairchild Semiconductor, a bedroom office, and a profound shift in the electronics industry.

page 20

## **INSIDE THIS ISSUE**

The Internet of Things has the potential to change the world, just as the internet did.

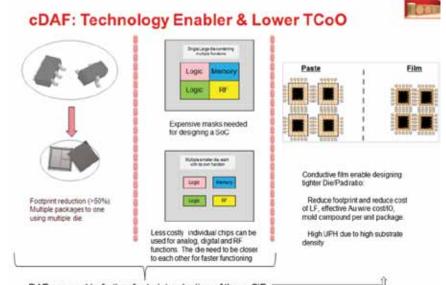

What are the key multi die integration challenges for SATS providers?

The Coming Era of Intelligent Medical Systems (IMS).

**N**

- : Cu wire bond as good as gold

- Low cost opportunity

- Wire diameters as low as 0.7 mils

- **::** Leader in high volume production

- **::** Quality and yield equivalent to gold

- **High reliability, typically 2x JEDEC**

www.aseglobal.com © ASE Group. All rights reserved.

## **BOARD** LETTER

## Linking the Pieces in an Expanding Packaging Universe

Dr. Raj Pendse, Vice President of Advanced Products and Technology Marketing STATS ChipPAC MEPTEC Advisory Board Member

IF YOU ARE A PACKAGING LOVER like me, you have probably enjoyed the ride up to here. Surely, we have come a long way from the days when people would ask "if you are a Packaging Engineer, you must be very busy during Christmas?!?" (ouch) Happily, it is fair to say that today Packaging has evolved into a significant part of the overall electronic solution and perhaps a discipline with enough depth that many universities even offer doctorate programs on Packaging topics.

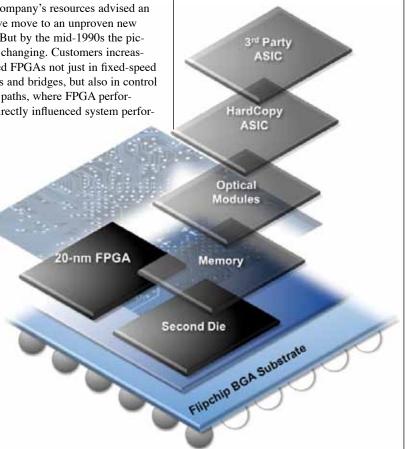

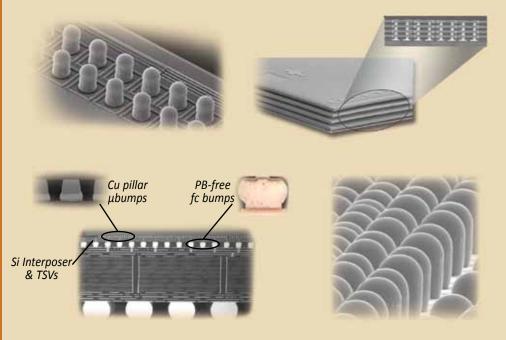

It is worthwhile to take a look at where we have been, where we are going and what the challenges are in getting there. We are in the midst of a rapidly changing Packaging industry landscape. The traditional approach of a substrate-based package comprising a die attached to a lead frame or laminate substrate is giving way to packaging at the wafer and Si level, with interconnection schemes changing from wire bond to flip chip and Through Si Vias (TSV's) and I/O densities increasing rapidly with finer Si nodes. The seemingly independent trajectories of integration at the die level in the form of SoC (System on a Chip) and integration at the package level in the form of SiP (System in a Package) are converging into a superset of 3D packaging which rely on

a judicious blending of Si and Packaging technologies. In order to make this paradigm work it is imperative to link a myriad different elements ranging from Si fabrication, Packaging, Design and Test (to name a few). Enter MEPTEC, an institution that has been with us for many years and provided a forum for seamless discussion and meeting of the minds in semiconductors, packaging, test, and a diversity of products and end-applications. Hence, it did not take much convincing for me to accept MEPTEC's invitation last year to enlist me as one of its Advisory Board Members.

Through its various programs and forums that range from monthly luncheon talks on topics of interest in an informal setting, to sponsored conferences on pertinent subjects like 3D TSV, MEMS and Medical electronics, and the publication of their Newsletter, the MEPTEC Report, that covers many topics of direct interest to professionals in these important disciplines, MEPTEC provides the mechanism to link the pieces in our expanding Packaging universe. MEPTEC's role is all the more important today given the landscape changes we talked about above and what seems to be an increased number of "moving parts" that need to be pulled together in the construction of a working solution.

Even as the specific coverage of MEPTEC's activities is continually evolving as technology progresses, its basic mission to provide an inter disciplinary meeting ground for intellectuals remains the same – I encourage you to join many others in participating in MEPTEC's diverse and dynamic activities so our happy ride may continue into the future.

DR. RAJ PENDSE is Vice President of Advanced Products and Technology Marketing at STATS ChipPAC. Prior to joining STATS ChipPAC, Raj held various positions in package engineering and R&D at National Semiconductor Corp. and Hewlett-Packard Labs. His work has spanned the gamut from packaging of high-end microprocessors, ASIC and graphics products to low-cost packaging solutions for logic and analog devices that find use in mobile phones and consumer products. His most recent focus has been on Flip Chip and 3D Wafer Level Packaging. Raj completed his B.S. in Materials Science from IIT Bombay with Top in Class honors and his Doctorate in Materials Science from UC Berkeley.

FIRST ANNUAL INTELLIGENT MEDICAL SYSTEMS CONFERENCE The Coming Era of Intelligent Medical Systems: Bringing Biomedical Devices to Life Tuesday, April 9, 2013 A University of Texas at Dallas Event in association with MEPTEC

For more information and to Register Today visit www.meptec.org or email bcooper@meptec.org

A Quarterly Publication of The Microelectronics Packaging & Test Engineering Council

Volume 16, Number 4

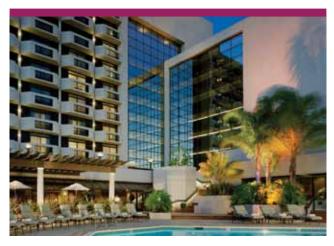

## **ON THE COVER**

SEMI-THERM, in association with MEPTEC and Electronics Cooling Magazine, will present the SEMI-THERM EXECUTIVE BRIEFING in March as part of the 29th Annual SEMI-THERM Conference and Exposition. The Executive Briefing titled "Thermal Management Marketing Visions & Strategies" will be held on Monday, March 18, 2013. SEMI-THERM runs March 17th to the 21st at the DoubleTree Hotel in San Jose, California.

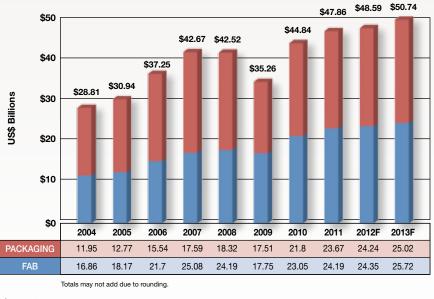

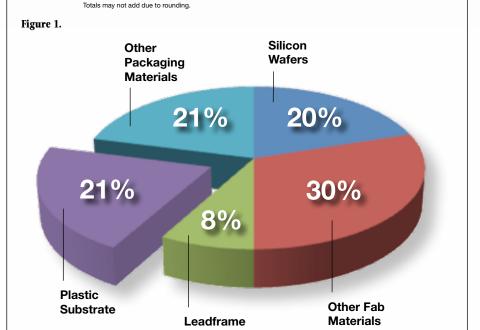

ANALYSIS – Though market challenges exist for suppliers, new material solutions will be needed to deliver increasingly complex and integrated packaging technologies that will benefit the end consumer in an ever more mobile and interconnected world.

BY DAN TRACY SEMI

| ADERA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  | proches supplexes despression<br>and reflection for the supplexest of<br>Hospital devices to use and hospital<br>devices and water to use and hospital<br>fields and the state of the supplexest operation<br>of the devices of the state of the supplexest<br>of the devices of the state of the supplexest of<br>the devices of the state of the supplexest of the<br>supplex of the state of the supplexest of the supplexest of<br>the state of the supplexest of the s |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A feature interview of the set<br>of percent descent of the set<br>of percent descent of the set<br>of the set of the set of the set of the set<br>of the set of the set of the set of the set<br>of the set of the s |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  | An experience of the second se                                     | A statement of the stat | \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A thread to a set of the set of t |  |  | The startight high by the particular of the starting of the st                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

20 PROFILE – Altera continues to push forward on their original promise: bringing system design teams the ability to define just the silicon they need and implement it on-site, without delays or inordinate risks. But the company is carrying this to a new level...

ALTERA CORPORATION MEMBER COMPANY PROFILE

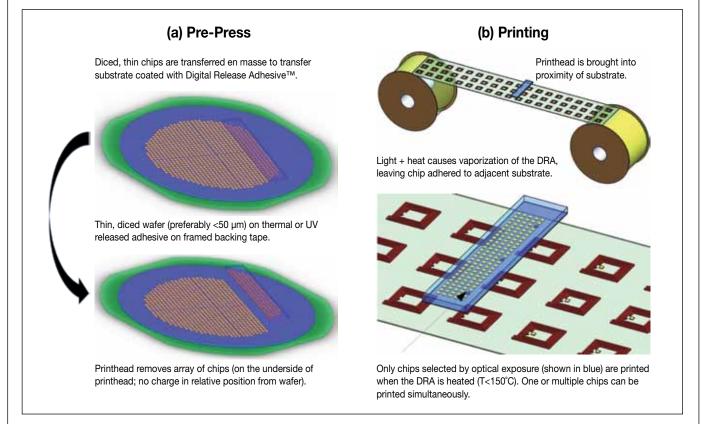

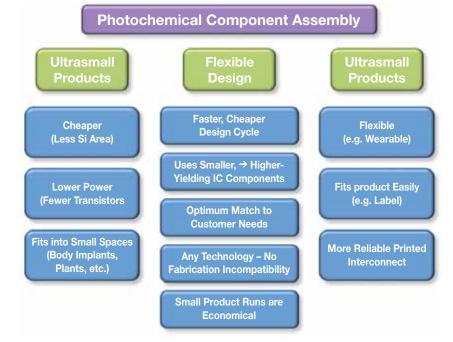

**23** TECHNOLOGY – The phrase "Internet of Things" was coined in 1999 by Kevin Ashton at Proctor & Gamble in a presentation where he drew attention to the value of having "things" be able to report information about themselves besides just their identity.

#### BY JAYNA SHEATS TEREPAC CORPORATION

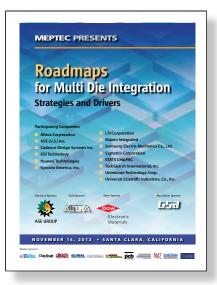

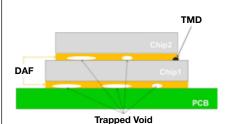

26 PACKAGING – SATS providers face three key challenges when it comes to the assembly of multi chip packaging. Stacking multiple die in a package requires unique assembly technology. Another challenge is backgrinding and handling. Finally, there are challenges for the process flow.

BY Y. S. KIM SIGNETICS CORPORATION

DEPARTMENTS

3 Board Letter I 5 Member News I

- Industry Insights Column

Coupling & Crosstalk Column

Event Follow-Up

- 28 Henkel News30 Dow Electronic Mtls.34 Opinion

The MEPTEC Report is a Publication of the Microelectronics Packaging & Test Engineering Council

P. O. Box 222, Medicine Park, OK 73557 Tel: (650) 714-1570 Email: info@meptec.org

Publisher MEPCOM LLC Editor Bette Cooper Art Director/Designer Gary Brown Sales Manager Gina Edwards

#### MEPTEC Advisory Board

Board Members Ivor Barber Xilinx, Inc. Jeanne Beacham Delphon Industries Joel Camarda Amonix, Inc. Jeff Demmin Tessera Inc. Douglass Dixon Henkel Corporation Nikhil Kelkar mCube Nick Leonardi Premier Semiconductor Services Phil Marcoux PPM Associates Bhavesh Muni Dow Chemical Corp. Kumar Nagarajan Maxim Integrated Raj Pendse STATS ChipPAC Rich Rice ASE (US) Inc. Jim Walker Gartner John Xie Altera Corporation

#### Special Advisors

Bance Hom Consultech International, Inc. Ron Jones N-Able Group International Mary Olsson Gary Smith EDA Mike Pinelis MEMS Journal, Inc.

Honorary Advisors Seth Alavi Sunsil Gary Catlin Plexus Rob Cole Skip Fehr Anna Gualtieri Elle Technology Marc Papageorge Semiconductor Outsourcing

Contributors

**Jianwei Dong** Dow Electronic Materials

Ira Feldman Feldman Engineering Corp.

Shashi Gupta Henkel Electronic Materials, LLC

**Donald Hicks, Ph.D.** The University of Texas at Dallas

Ron Jones N-Able Group International

Y. S. Kim Signetics Corporation

Dr. Raj Pendse

Jayna Sheats Terepac Corporation

Wataru Tachikawa Dow Electronic Materials

> Dan Tracy SEMI

Francoise von Trapp 3D InCites

Howard Yun Henkel Electronic Materials, LLC

MEPTEC Report Vol. 16, No. 4. Published quarterly by MEPCOM LLC, P. O. Box 222, Medicine Park, OK 73557. Copyright 2012 by MEPTEC/MEPCOM LLC. All rights reserved. Materials may not be reproduced in whole or in part without written permission. MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere. For advertising rates and information contact Gina Edwards at 408-858-5493, Fax Toll Free 1-866-424-0130.

## **Plexus Expanding Design and Manufacturing Operations in the UK Meeting Growing Demand** for Product Realization Solutions

PLEXUS CORPORATION. the Product Realization Company, has announced its intention to expand its Livingston Design Centre to larger premises at the Pyramids Business Park, in Bathgate. Having worked closely with Scottish Enterprise on funding support, Plexus will expand its UK manufacturing footprint by opening a new manufacturing facility at the same location.

Welcoming the news, First Minister Alex Salmond said: "Plexus' decision to invest £9 million in expanding their Scottish operations will provide a welcome boost to the local economy, creating 130 new jobs and a new design, prototyping and manufacturing facility in Bathgate. The Scottish Government and our enterprise agencies are focused on securing new jobs, and investment and Plexus expansion plans will receive up to £1m of support through Scottish Enterprise. News that this international design and manufacturing firm is stepping up its Scottish operations is testament to the quality and skills of the West Lothian workforce and reinforces Scotland's reputation for excellence in innovation and manufacturing."

The new manufacturing

facility will be approximately 47,000 sq ft and will include prototyping, manufacturing and warehousing areas. The site will complement Plexus' existing manufacturing facility in Kelso as well as becoming a European centre of excellence for prototyping. The co-location of design, prototyping, and manufacturing in one facility, enhances the value proposition for Plexus customers and reinforces Plexus as the Product Realization Company in the UK.

It is anticipated that both the design centre and manufacturing site will be operational in February 2013.  $\blacklozenge$

## Advantest Develops Mask Defect Review SEM E5610 For Next-Generation Photomasks

## ADVANTEST CORPORATION HAS

announced that it has developed a new mask defect review tool, the Mask DR-SEM E5610, for reviewing and classifying ultra-small defects in photomask blanks. The E5610 inherits the highly stable, fully automatic image capture technology developed by Advantest for its acclaimed multi vision metrology SEM for photomasks, and features a newly developed beam tilt mechanism that enables scanning at oblique angles. With its high-accuracy, high-throughput defect review capability, the E5610 is expected to contribute to next-generation photomask product quality improvement and shorter manufacturing turn-around times.

Photomask manufacturing processes require 100% eradication of fatal defects, which adversely affect yield, in tandem with turnaround time reduction. Advantest's new E5610 promises to be an indispensable solution for mask manufacturers, satisfying both of these requirements with fast, accurate technology that classifies defects and diagnoses appropriate repair solutions with regard to type.

High Spatial Resolution & Oblique Scanning Capability - Advantest's proprietary column architecture delivers spatial resolution down to 2nm, even at the low acceleration voltages appropriate for photomask screening. Moreover, the E5610 features a unique, electrically controlled tilt module that allows its beam to tilt by

up to 15°, enabling users to perform 3D defect reviews.

Highly Stable, Fully Automatic Image Capture - Even when operating at high SEM magnification, the E5610 performs stable, fully automatic defect imaging at a high rate of throughput, thanks to its high-accuracy stage, charge control function, and contamination reduction technology.

Compatible With Mask Inspection Systems -The E5610 is compatible with mainstream mask inspection systems: the tool imports defect location data and automatically images the locations.

Elemental Composition Analysis Option -The E5610 features an optional EDS (energy dispersive X-ray spectrometry) module that performs elemental analysis-an advanced method of mapping mask blank defects.

For more information visit the Advantest website at www.advantest.com.  $\blacklozenge$

## **MEMBER** NEWS

#### ADVANTEST **INTRODUCES T2000 8GBPS DIGITAL MODULE FOR HIGH-**SPEED TESTING

Advantest Corporation has introduced its new T2000 8GDM to address the test requirements of system-on-chip (SoC) devices with high-speed serial, parallel and memory interfaces such as PCI-Express and double data rate (DDR) connections. The T2000 8GDM has the versatility to test a wide range of SoC interfaces while operating at data rates up to 8Gbps. Key capabilities include clock and data recovery (CDR), jitter injection, I/O dead band cancellation and multi-strobe operation. www.advantest.com

#### ENTEGRIS NAMED TO LIST OF 100 MOST **TRUSTWORTHY U.S. COMPANIES**

Entegris, Inc. was named by Forbes Media to the publisher's list of America's 100 Most Trustworthy Companies. To develop the list, Forbes used data generated by an independent financial analytics firm called GMIRATINGS (GMI). GMI evaluated more than 8,000 publicly held companies on a broad range of metrics and company policies, including executive compensation, management turnover, insider trading relative to corporate peers, and short-term executive compensation. While only three companies scored the highest score of 100, Entegris was one of only two mid-cap companies that scored a near perfect 99.

#### AMKOR CEO KEN JOYCE TO RETIRE Amkor Technology, Inc.

has announced that Ken Joyce intends to retire as President and Chief Executive Officer and Director of the Company by the end of 2013, following more than 15 years of service to the Company. The Company's Board of Directors has created a search committee to identify Mr. Joyce's replacement. An executive recruiting firm has been retained to conduct an outside search and also to assist with the assessment of internal candidates. www.amkor.com

#### QUIK-PAK EXPANDS NEW OPEN-MOLDED PLASTIC PACKAGE PRODUCT FAMILY

Quik-Pak. a division of Delphon, has announced its 8-Lead SOIC (Small Outline Integrated Circuit), the newest addition to the Open-molded Plastic Package (OmPP)<sup>™</sup> product line. This 0.150" narrow body package is built to JEDEC standard MS-012 and is RoHS compliant. It is Ni/Au plated which is excellent for wire bonding. Quik-Pak's 8-Lead SOIC has a standard 0.050" lead pitch and a superior sealing surface for air cavity applications. Quik-Pak's OmPP product family includes pre-molded QFN (Quad Flat No-Lead) and SOIC package configurations that are designed to provide a high quality, quick, and cost-effective solution for your IC packaging and assembly needs. www.icproto.com

InvenSense<sup>®</sup> Motion Interface Solutions for Windows 8 and Windows RT Shipping in High-Volume

Offering Two Microsoft Corporation Certified Options to Balance System Partitioning and Cost

INVENSENSE, INC. HAS announced that its HID (Human Interface Device) and User-Mode Driver (UMD) motion sensing solutions for Windows 8 and Windows RT are in highvolume production with multiple Tier-1 Ultrabook™ and tablet manufacturers. In collaboration with Microsoft, InvenSense ported its MotionApps<sup>™</sup> software to the new Windows 8 OS and its solutions are now WHCKcertified for both Intel and ARM architectures. This allows for rapid integration of InvenSense MotionTracking devices along with robust and field-proven MotionApps software, providing OEMs with a one-stop sensor subsystem solution.

InvenSense provides Windows 8 Ultrabook and tablet manufacturers the option of implementing either a sensor hub solution inside a microcontroller using the HID protocol, or the lower-cost option of a hub-less UMD solution. Using InvenSense intelligent MotionTracking devices, both solutions meet Microsoft's requirements for low-power screen orientation and connected standby mode. The UMD solution manages Windows 8 protocols for low-power operation inside the intelligent MotionTracking hardware, without the need for a costly, discrete microcontroller sensor hub. Alternatively, the sensor hub solution supports both HIDover-USB and HID-over-I2C protocols running on popular microcontroller architectures.

InvenSense MotionTracking devices and MotionApps software for Windows 8 and Windows RT are available today. For more information, please contact sales@ invensense.com.

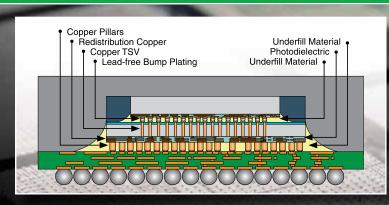

## STATS ChipPAC's Advanced eWLB Provides Versatile Integration Platform for 2.5D and 3D Technology Evolution

eWLB Packaging Options Expanded to Include Interposer Technology, Flip Chip Interconnect and Complex 3D System-in-Package Configurations

STATS CHIPPAC LTD. HAS ANNOUNCED that its expanded packaging options for advanced embedded Wafer Level Ball Grid Array (eWLB) technology provide a versatile platform for the semiconductor industry's technology evolution from single or multi-die 2D package designs to 2.5D interposers and 3D System-in-Package (SiP) configurations.

The advancement of silicon scaling to 14 nanometer (nm) in support of higher performance, higher bandwidth and lower power consumption in portable and mobile devices is pushing the boundaries of emerging packaging technologies to smaller fan-out packaging designs with finer line/spacing as well as improved electrical performance and passive embedded technology capabilities. With its continuous innovation and extensive manufacturing experience in eWLB technology, STATS ChipPAC has established a flexible integration platform for 2.5D and 3D packaging at a lower overall cost with proven solutions that overcome manufacturing challenges pertaining to design, material compatibility and manufacturability.

With the inherent performance and cost advantages of eWLB, STATS ChipPAC is effectively addressing some of the challenges in high end flip chip applications that require much finer bump pitches, higher input/output (I/O) densities and the elimination of stress on extreme low-k or ultra low-k (ELK/ULK) dielectric structures at advanced silicon wafer nodes. eWLB's fanout packaging approach with its inherently lower stress, larger pad pitch, and redistribution layer (RDL) allows higher integration and routing density in less metal layers in an fcBGA substrate. The fine line width and spacing capabilities of eWLB provides more flexibility in the package routing design and offers superior electrical performance, enabling the number of layers in the organic substrate of a standard fcBGA device to be reduced.

STATS ChipPAC's eWLB PoP solutions are available in either a single or double-sided configuration and provide a flexible integration platform for stacking a wide range of memory packages on top with a final stacked package height below 1.0mm. The number of interconnections between memory and processor can be up to 1024. The double-sided eWLB PoP technology features a flexible redistribution layer that can accommodate multiple active or passive devices in complex 3D SiP structures which enable very thin profiles, increased performance and superior warpage control. Further information is available at www.statschippac.com. ◆

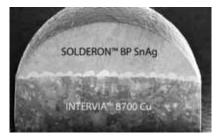

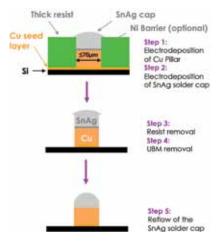

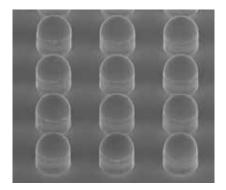

# Global Low-Cost Wafer Bumping Services

## • Europe – USA – Asia •

- Quick-turn and mass-production

- Highly competitive, low-cost bumping technology

- Exceptional quality through high-level expertise

## PAC TECH

Pac Tech GmbH Tel: +49 (0)3321/4495-100 sales@pactech.de www.pactech.de

Pac Tech USA Tel: 408-588-1925, ext. 202 sales@pactech-usa.com www.pactech-usa.com

Pac Tech Asia Sdn. Bhd. Tel: +60 (4) 6430 628 sales@pactech-asia.com www.pactech-asia.com

NAGASE & CO., LTD. Tel: +81-3-5640-2282 takahiro.okumura@nagase.co.jp www.nagase.co.jp

## **Available Processes**

- Electroless Ni/Au under-bump metallization

- Ni/Au bump for ACF or NCP assembly

- Solder paste stencil printing

- Solder ball drop for wafer-level CSP

- Solder jet for micro-ball placement

- BGA and CSP reballing

- Wafer backside thinning and wafer dicing

## **Special Features/Technologies**

- Over 10 years experience

- U.S. Government Certified

- 4- to 12-inch wafer capability

- Wafer pad metallization: Al and Cu

- Solder alloys: eutectic SnPb37, lead-free, low-alpha, and AuSn

- Fluxless and contactless bumping for MEMS and optoelectronics

- Ni/Au interface for wire-bond applications

## The leader in low-cost electroless wafer bumping.

## 450mm, 14nm Scaling Challenges to Highlight SEMICON Korea

Technological and economic challenges to continued scaling and 450mm wafer development will highlight conference programs and exhibitor displays at SEMICON Korea 2013, held from January 30-February 1 in Seoul. Co-located with LED Korea 2013, the largest exhibition in the world for LED manufacturing, the event will bring together global leaders in semiconductor manufacturing to share critical new technological development and business opportunities. The events will feature over 500 exhibiting companies from 20 countries and more than 45,000 attendees. Online pre-registration for visitors and programs is now in process for free entrance to SEMICON and LED Korea 2012. For registration, please visit www.semiconkorea.org.

## MEMBER NEWS

## DIGITALOPTICS NAMES NEW SVP OF SALES & MARKETING

Tessera Technologies, Inc. has announced that its wholly owned subsidiary, DigitalOptics Corporation has appointed James N. "Jim" Chapman as senior vice president, sales and marketing. Chapman will report to Robert A. Young, the Company's president and chief executive officer, and be responsible for DOC's global sales and marketing initiatives. www.doc.com

# HENKEL'S REVOLUTIONARY LOCTITE MAX 2

JEC Europe 2013 is the biggest composites expo in the world. Congregating 250,000 professionals from 100 different countries, JEC Europe 2013 will take place this year from March 12 to 14 at the Porte de Versailles, in Paris, Henkel, the world's leading producer of adhesives, will present composite solutions for the automotive and aerospace industry. The main focuses will be the innovative fast curing composite matrix resin Loctite MAX 2 for automotive and a complete portfolio of Benzoxazine based composite products for aerospace applications. Loctite MAX 2 is a polyurethane based resin system that cures faster than traditional epoxy resins where as the Benzoxazine resin based composite and complementary products changes the paradigm of performance and temperature profile of traditional systems.

www.henkel.com

## MEMBER NEWS

#### LSI NAMED ONE OF THE WORLD'S TOP INNOVATORS LSI Corporation has

announced that it has been named a Thomson Reuters 2012 Top 100 Global Innovator, recognizing its achievements as one of the world's most innovative companies. The program honors corporations and institutions worldwide that are at the heart of innovation as measured by patent-related metrics. The Thomson Reuters 2012 Top 100 Global Innovator methodology is based on four principal criteria: overall patent volume, patent grant success rate, global reach of the portfolio and patent influence as evidenced by citations. The Thomson Reuters 2012 Top 100 Global Innovator award recognizes companies for significant, ongoing innovation, evaluated on patent metrics including the number of successful patent filings, the global reach of the inventions and impact on the industry. www.lsi.com

### DISCO CORP. TO STRENGTHEN ITS SECONDHAND EQUIPMENT BUSINESS

#### **DISCO** Corporation

has announced plans to strengthen and develop its secondhand equipment business, which involves buying back and refurbishing used DISCO equipment. There is growing demand for secondhand equipment in order to reduce the financial burden of capital investment to improve production capabilities and for early

## SonoSimulator Takes the Mystery Out of Stacked Die

Sonoscan, in Collaboration with T.U. Dresden, has Developed a Software Program that Creates a Virtual Model of the Echo Returns of the Die Stack

STACKING DIE PERMITS designers to pack a great deal of capacity and increase processing speed in a much smaller volume. In the process the die stack also creates many internal interfaces where critical defects, such as voids and delaminations, can lurk.

Makers of die stacks are very interested in using nondestructive acoustic microscopy, such as C-SAM<sup>®</sup>, to locate and image these critical defects, but until recently the die stacks have been far more difficult to image clearly than other IC devices.

The problem is that when ultrasound is pulsed into a die stack, the numerous internal interfaces create multiple return echoes in the A-Scan.

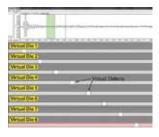

To speed up and simplify the task of assigning each echo to its proper interface within stacked die, Sonoscan<sup>®</sup> has developed over the last several years, in collaboration with T.U. Dresden, a software program called SonoSimulator<sup>™</sup> that creates a virtual model of the echo returns of the die stack. The user of the program enters data about the dimensions and materials of the stack and then the software creates the virtual model for simulation of the A-Scan.

To simulate defects for imaging, the operator uses the SonoSimulator software to insert virtual defects at interfaces of interest. The virtual defects simulate air gaps (example from Sono-Simulator in Figure 1) so that the interface between virtual die 5 and 6, for example, can be identified by its position from left to right, position #5 in this case. The oscilloscope waveform at the top of Figure 1 (known as the A-Scan) is so realistic that the virtual

#### Figure 2

defects act like real gap-type defects, reflecting >99.99% of the ultrasound energy.

The user interacts with the SonoSimulator to perform simulated imaging of the virtual die stack at the levels of interest by adjusting gates (precise depths from which echoes are used to make an image; one gate is green in Figure 1) within the simulated A-Scan. When the user is satisfied with an image of the defect at a specific level, they now know the precise position and width of that gate. The imaging (gating) recipe is then transferred to a Sonoscan Gen6<sup>™</sup> C-SAM (C-Mode Scanning Acoustic Microscope) system to scan and image a real die stack sample. In a production environment, a test die stack will likely have a "known defect" planted between two die to help identify a specific level. When the "known defect", which is an intentional reflective gap, is in focus any other unintended gap-type defects or features at that interface will also be in focus.

The stacked die manufacturing process or materials may evolve over time, which may then require adjusted parameters to properly image the stacked die levels. The SonoSimulator process can be repeated to refine the image(s) by adjusting the gate and recipe parameters on a revised virtual sample, and then moving the improved parameters back to the C-SAM system to analyze the evolved sample.

Figure 2 is the SonoSimulator derived C-SAM image of a test stack sample having 8 die with acoustically reflective numerals and bars etched on each die. In this image, the SonoSimulator provided the scan parameters to isolate and image the "known defect" specific to die 4 on the left and die 8 on the right.

SonoSimulator was originally designed to help obtain C-SAM images for stacked die, but other thin, multi-layer sample analysis can be done, too. In any sample with multiple, closely spaced interfaces the ultrasound echoes may be hard to distinguish or separate for each interface, and/or may interfere with each other. With this integrated software, a model of the sample can be built to simulate the echo patterns with known defects at each layer of interest. Using a reference waveform, a model of the A-Scan is generated, which can be captured and compared for each layer of interest. Transducer frequency, focus level and gate positions can then be established, tested and refined prior to transferring the imaging recipe settings to the Gen6 for all future parts of the same construction.

For more information visit www.sonoscan.com.

## Every Second Car Produced Today Contains Infineon Microcontrollers

## The Company Has Just Delivered its 100 Millionth TriCore<sup>™</sup> Microcontroller

INFINEON TECHNOLOGIES AG has just delivered its one hundred millionth Tri-Core<sup>™</sup>microcontroller. That ranks these microcontrollers among the most successful in automotive electronics. The TriCore-based microcontrollers from Infineon are assembled in over fifty automotive brands. Statistically speaking, this means that almost every second vehicle produced today includes a TriCore-based microcontroller. It is responsible for keeping the fuel consumption and exhaust emissions as low as possible.

TriCore-based microcontrollers are used in the central control units for combustion engines and gearboxes to control the injection, ignition or exhaust gas recirculation: Increasingly, they are also being used in hybrid and electric vehicle drives. Other areas of application include electric steering, braking and chassis control as well as body control. TriCore is also used in other areas not related to the automotive sector, for example in system controls, solar inverters and for steering electric motors.

TriCore is a 32-bit

microcontroller architecture optimized for embedded realtime systems. It unifies realtime capabilities, signal-processing functions and highly efficient application-specific interface functions. The core has a super-scalar processor and is thus able to carry out a number of different commands simultaneously. The command set includes special mathematical functions for the efficient calculation of complex algorithms. TriCore microcontrollers are ideal for automotive applications by virtue of their high data rate and real-time capability, namely in the temperature range from -40 °C - 170 °C.

Besides the management and transmission control systems, Infineon chips are used in airbags, driver assistance systems, in electronic steering support, in ABS, Electronic Stability Programs (ESP), pedestrian protection and in tire pressure control, in electric power windows, lighting control, in heating, ventilating and airconditioning systems, in seat adjustment and keyless door opening.

In 2011, around 75 million vehicles were manufactured, of which 20 million were produced in Europe alone. On average, each vehicle contains chips worth about USD 300. Infineon has a ten percent share of this market - and is thus one of the world's largest chip manufacturers for automotive electronics; what is more, the company is also the largest chip manufacturer in Europe (with 15 percent of the market). In 2011, the total value of the market for automotive chips amounted to approximately USD 23 billion (source: Strategy Analytics, April 2011 – a market research company). For its microcontrollers in engine management and transmission control units. Infineon holds a global market share of over 30 percent.

Further information about Infineon microcontrollers is available at www.infineon. com/tricore.

## Altera Ships Its First SoC Devices

ALTERA CORPORATION HAS ANNOUNCED the first shipments of its 28 nm SoC devices, which combine a

dual-core ARM® Cortex<sup>™</sup> A9 processor system with FPGA logic on a single device. Altera SoCs include several distinctive features that enable developers in the wireless communications, industrial, video surveillance, automotive and medical equipment markets to create custom SoC variants optimized for system power, board space, performance and cost requirements. The first devices Altera is shipping are low-power, lowcost Cyclone<sup>®</sup> V SoCs.

Altera is the only FPGA vendor today shipping SoCs that offer 32-bit error correction code (ECC) support which helps ensure data integrity throughout the embedded system. Other unique features in the device family include a high-bandwidth memory controller with built-in memory protection, flexible boot capability and integrated PCI Express<sup>®</sup> (PCIe<sup>®</sup>) across all SoC devices. ◆

## MEMBER NEWS

start-up of production lines, as well as for machine purchases in emerging countries, small- and medium-sized factories. universities, and R&D laboratories. The secondhand semiconductor manufacturing equipment market is worth an estimated US\$6 billion (according to a 2010 SEMI study) and continues to grow at a constant rate. Sales are especially strong for non-semiconductor manufacturer third-party end-users, however many are reluctant to proceed due to the disadvantages of unsupported maintenance and parts. DISCO aims to achieve a sales target of 500 million yen within the first year and 2 billion yen in three years. www.disco.co.jp

#### MST OPENS SALES OFFICE IN SINGAPORE

The Micro Systems Technologies Group (MST) has just opened a sales office in Singapore in September of this year. With this new branch office, existing customers in the Asia/Pacific region will be better served, and it will also be possible to meet the increasing demand in this region for innovative solutions from the MST Group. www.mst.com

#### SIGNETICS ANNOUNCES PLAN TO DOUBLE THEIR FLIP CHIP PACKAGE ASSEMBLY CAPACITY

Signetics Corporation has announced that it has approved capex plans and has ordered equipment that will double their capacity for Flip Chip

## MEMBER NEWS

Package Assembly at their factory in Paju, South Korea. The new Flip Chip expansion will be qualified by January 2013 and will be ready for volume production in February 2013. The centerpiece of this new equipment is the Quantum 8800 Flip Chip bonder by Datacon. This bonder allows for finer bump pitches below 100µm and is compatible with the 95mm PCB format.

www.signetics.com

#### DIGITALOPTICS TO FOCUS ON CORE MEMS CAMERA MODULE BUSINESS Tessera Technologies.

Inc. has announced that its wholly owned subsidiary, **DigitalOptics** Corporation will focus its efforts on its core MEMS camera module business, which targets the large and growing mobile phone market. DOC plans to reduce its workforce not including those related to manufacturing operations in Zhuhai, China - by up to 40%. These actions could result in annualized operating expense savings of between \$15 million and \$18 million by the second quarter of 2013. As part of this process DOC plans to cease operations at its facility in Tel Aviv, Israel and to pursue a possible sale of, or other strategic alternatives for, its facility in Charlotte, NC. These two facilities are not central to the MEMS camera module opportunity. Given full effect, the planned actions would reduce the non-Zhuhai workforce of 450 by approximately 180 employees. www.doc.com

## STATS ChipPAC Announces Expansion Plans in South Korea

STATS CHIPPAC LTD. HAS ANNOUNCED plans to expand its semiconductor assembly and test operation in South Korea. The Company has signed a non-binding memorandum of understanding to invest in a new integrated facility in the Incheon Free Economic Zone, an international business district located in the Incheon metropolitan area that is adjacent to Seoul, South Korea.

The integrated facility will include approximately 95,000 square meters (1 million square feet) of land with options for future expansion. The integrated facility will be used for manufacturing, research and development, and administration. Construction is scheduled to begin in the third quarter of 2013 and the new facility is expected to be operational in the second half of 2015. STATS ChipPAC intends to integrate its existing facilities in South Korea into the new, larger facility to achieve a more efficient, cost effective manufacturing flow and provide flexibility for future expansion.

"STATS ChipPAC Korea is an important strategic manufacturing operation with an illustrious history of delivering the most advanced packaging and test technologies with proven manufacturing capabilities that extend back over 27 years to when the factory was first established. We are very confident that our expansion in South Korea will increase our overall competitiveness in advanced flip chip, advanced wirebonding and three dimensional (3D) packaging technologies where we have established a strong leadership position in the industry," said Tan Lay Koon, President and CEO, STATS ChipPAC.

STATS ChipPAC Korea's sizeable flip chip technology portfolio ranges from large single die fcBGA packages with passive components used for graphics, CPU and ASIC devices to smaller fcFBGA packages including single die, multi-die and stacked configurations that combine wire bond and flip chip technology within a single package. In terms of 3D technology, STATS ChipPAC Korea provides advanced Package-on-Package (PoP), Package-in-Package (PiP) and System-in-Package (SiP) technologies that integrate one or more integrated circuits or passives into a single solution for mobile, digital consumer and data storage applications.

Further information is available at www. statschippac.com.  $\blacklozenge$

## Altera and ARM Announce Industry's First FPGA-Adaptive Embedded Software Toolkit

ALTERA CORPORATION and ARM have announced that, with a unique agreement, the companies have jointly developed a DS-5 embedded software development toolkit with FPGAadaptive debug capabilities for Altera SoC devices. The ARM® Development Studio 5 (DS-5<sup>™</sup>) Altera Edition toolkit is designed to remove the debugging barrier between the integrated dual-core CPU subsystem and FPGA fabric in Altera SoC devices. By combining the most advanced multi-core debugger for the ARM architecture with the

ability to adapt to the logic contained in the FPGA, the new toolkit provides embedded software developers an unprecedented level of fullchip visibility and control through the standard DS-5 user interface. The new toolkit will be included in the Altera SoC Embedded Design Suite and will begin shipping in early 2013.

Altera SoC devices combine a dual-core ARM Cortex-A9 processor with FPGA logic on a single device, giving users the power and flexibility to create custom fieldprogrammable SoC variants by implementing user-defined peripherals and hardware accelerators in the FPGA fabric. Altera is currently shipping initial samples of its Cyclone® V SoC devices. The ARM Development Studio 5 (DS-5) Altera Edition toolkit dynamically adapts to unique customer configurations of the FPGA

within the SoC to seamlessly extend embedded debugging capabilities across the CPU-FPGA boundary and unify all software debugging information from the CPU and FPGA domains with the standard DS-5 user interface. When combined with the advanced multi-core debugging capability of the DS-5 Debugger, and the link to the Quartus® II software SignalTap logic analyzer forcross-triggering capability, the toolkit delivers an unprecedented level of debugging visibility and control that leads to substantial productivity gains.

More information about the Altera SoC EDS can be found at www.altera.com/ soc-eds. More information about the ARM DS-5 Altera Edition toolkit can be found at www.altera.com/ds-5-ae. The Altera SoC EDS will start shipping in early 2013.◆

## COLUMN

## INDUSTRY INSIGHTS

By Ron Jones

## EMP and Us

▶ IN MY LAST COLUMN I LOOKED at the myriad life changing devices and technologies that the semiconductor industry has enabled through speed increases, size reductions and power efficiencies. It is hard to image a negative side to these accomplishments, however, we will explore one here. The potential negative effects apply not only to our industry, but also to us as inhabitants of this planet.

An Electro-Magnetic Pulse (EMP) is a sudden burst of electromagnetic energy which can be very damaging to almost everything that is electrical. In order to provide a framework for this column, I will separate the EMP sources into manmade and naturally occurring. To further structure in another dimension, I will break the impacts into those to electrical power distribution systems and those to electronic circuits. Though these may seem arbitrary, you'll understand the logic as you read on.

One potential source of an EMP is a man-made device such as nuclear bomb. The impact was known as early as US nuclear testing in 1945, with the first real understanding of the impact from the Starfish Prime high altitude detonation over the Pacific in July 1962. Man-made devices detonated in the atmosphere tend to have line-of-site impact. Scientists predict that a one megaton nuclear device detonated at an elevation of 300 miles over the center of the US, would impact the entire continental US. There are many devices of this size in existence around the world. It would take a much smaller yield device detonated at a lower altitude to disable a US metropolitan area, such as New York, or the State of Israel. People on the ground would not be directly harmed and might not even realize that the detonation took place. With such a short distance to earth, the high energy burst would arrive immediately, delivering millions of volts of energy in a short, high energy burst lasting a nanosecond. There would be no warning other than detection of the warhead delivery vehicle.

The second EMP source that has been around since time immemorial is our own sun. There have been, and will continue

to be, varying size eruptions of very hot electrified gasses from the surface of the sun called solar flares or coronal mass ejections. Currently, the timing and size of these events are unpredictable. Photons (light) from such an event reach earth after roughly 8 minutes and are harmless. A proton storm related to the eruption takes 1 to 3 days to travel to earth. The scope is so massive that there is interaction with the magnetic fields of the earth, thus impacting the entire surface, not just line of sight regions. The US has satellites deployed between the earth and sun that can detect the magnitude of this proton barrage and relay the info to earth almost immediately. This potentially allows some time for planes to be safely grounded, the grid to be shut down in an orderly fashion and other actions to be taken to minimize damage. The largest recorded eruption event occurred in the summer of 1859. Electricity was still in its infancy, yet telegraph wires shorted and created a number of fires and other electrical devices malfunctioned. The Aurora Borealis was seen as far south as Cuba and Hawaii. Similar to earthquakes, these will continue and inevitably a "big one" is somewhere down the road.

One of the major risks from EMP is to electrical distribution systems such as the US Grid. The thousands of miles of high voltage power lines act as huge antennas for EMP radiation. Massive currents are induced into the lines and flow toward both generators and transformers. When the current arrives at the end of the line, it has no place to go and explodes the attached generator or transformer. Some scientists estimate that a large burst from a man-made or natural source could destroy the entire grid. It might take 10 years to build back the distribution network since with no power, it is difficult to manufacture anything, including generators and transformers.

The second major risk is to any device or system that contains microcircuits. Today's high tech microelectronics runs on supply voltages of less than 2 volts and are sensitive to ESD voltages in the range of 50 volts or less. Gamma rays from an EMP pulse can generate millions of volts. A typical IC has dozens to hundreds of antennas protruding from the package (leads) that can deliver energy from the pulse directly to the chip. The device doesn't stand a chance and is immediately fried. Many groups are seeking ways to harden manufacturing, control and communication systems that are based on sensitive chips. There are things that can

be used to protect microelectronics such as faraday cages; however, their weakness is that even cages must have "openings" where power and signals enter and exit, thus providing EMP entry points. Solar EMP does not present as big a risk to IC's as does nuclear EMP.

As bad as the loss of power distribution and electronics sounds, it is only the very beginning of the real human disaster. The average city has about 3 days of food. Without electricity, all the factories that process food will no longer operate. The systems that purify and deliver most of the drinking water will no longer work. The refineries that convert crude oil into gasoline shut down. Most trucks and vehicles will not operate. People in populated areas (possibly around the world) would rapidly run out of water and food and humans would begin to perish from thirst and starvation within a short period of time.

Imagine the 600,000 inhabitants of Las Vegas trying to find water and food in the middle of the desert that surrounds them. Imagine 19 million Metro NY residents, packed into an area of 80x80 miles, trying to obtain food and water with no electricity and no transportation. Rural areas are only slightly better off as they will be impacted by power loss and urban dwellers may come and strain what resources they have.

A small country like Iraq or a wellfunded terrorist group could essentially level the playing field with a strategically placed SINGLE device attack against the US. The effect of 9/11 could be multiplied 10,000 fold.

This is a threat in which the world or a significant part of it could be changed in an instant and not be able to recover before there was massive loss of life. To think that, because it has never happened, it never will is extremely naive. Had the 1859 solar storm occurred in 2012, all indications are that there would have been major impacts to the world's people.

Our success in miniaturizing the world's electronics has potentially provided a way for all the progress we've enabled to be undone. Surely there are ways that our industry can help provide solutions to some of these problems. There are also things we can do to help protect our families.

We need to pitch in and do our part for our families, our country and mankind.

Much of the information for this article came from the National Geographic DVD, Electronic Armageddon, and from various Wikipedia entries. ◆

## COLUMN

## Temperature Data Loggers

**Marathon Products, Inc.** headquartered in San Leandro, CA is a global supplier of investigative temperature recording devices used to validate shipments of epoxies, laminates and other critical materials used in the manufacture of integrated circuits.

**Operating ranges: -80°C to 72°C.** Our devices are programmed in English, Japanese, French, German, Spanish, Mandarin, and Portuguese to support globalization. Make **C\temp** your last OC gate for product validation prior to acceptance of critically-sensitive materials for manufacture.

Don't ship without us<sup>•</sup>

#### SMT, COB, COF, IC ASSEMBLY SAME DAY, 1 - 5 DAYS TURN

**AmTECH** is a leading Silicon Valley provider for SMT, COB, COF and IC Assembly.

Gold ball, aluminum and gold wedge wire bonding, Automated Optical Inspection (AOI) and XRAY.

- SMT ASSEMBLY,

- Lead-Free, 0201, uBGA, CSP – COB, COF, IC ASSEMBLY,

- Cleanroom ISO 7 (Class 10,000), Aluminum and Gold wire – NPI - PROTOTYPE,

- 8, 24 to 72 hours turn – Low to Medium Volume PRODUCTION,

- MRP, IPC-A-610 Class 2 and 3, MIL-STD-883

#### Your NPI Manufacturing Solution!

Phone (408) 227-8885 Email: info@amtechmicro.com

#### www.amtechmicro.com

## COUPLING & CROSSTALK

By Ira Feldman

ELECTRONIC COUPLING IS THE transfer of energy from one circuit or medium to another. Sometimes it is intentional and sometimes not (crosstalk). I hope that this column, by mixing technology and general observations, is thought provoking and "couples" with your thinking. Most of the time I will stick to technology but occasional crosstalk diversions like this one may deliver a message closer to home!

## Quality for the Long Haul?

▶ DOES A MANUFACTURER'S REsponsibility and interest in quality end when the warranty expires?

When is death premature? People have life expectations based upon family and societal statistics as well as their health. Mechanical devices, especially those with moving parts, have estimated lives and known wear out mechanisms. Cars currently have an average age of 11 to 13 years of useful life which allows consumers to set reasonable expectations of service life. What about electronics? What is a reasonable expectation of service life?

I had a few devices at home fail recently which makes me wonder about the reliability of consumer electronics. Have quality standards fallen and have we reached the point of truly disposable electronics?

#### The Weakest Link?

A four-year-old LCD computer monitor intermittently failed to turn on. A quick Internet search found several others with this same monitor who also had the exact issue. (Google is a fantastic diagnostic tool: query the make, model number, and a description of the symptom and you are likely to find others victims of the same issue plus often a solution.) People reported fixing the problem by replacing faulty surface mount chip capacitors on the motherboard. Since the monitor was no longer under warranty, the cost to have someone diagnose let alone repair this problem far exceeded the cost of replacing it.

My father in-law's rarely used sixyear-old DVD player died mid-movie, disappointing everyone. A Google search identified a capacitor (C318 in the power supply subsystem) as the most likely culprit. With new DVD players costing less than \$50, I wasn't too interested in confirming root cause failure. However, I did have to disassemble the player to retrieve the disc stuck inside. Clearly a system design failure since the unit did not fail in a safe or convenient mode. Upon opening the unit, it was clear that C318 was indeed blown.

My very small, and likely statistically insignificant, sample of failed devices appeared to indicate a trend. Do capacitors have a higher failure rate than other more complex electronic parts? Capacitors, if the circuit is designed and manufactured correctly, should have an extremely low failure rate. Some models predict the life of a capacitor increases by the square of the difference of the maximum rated temperature minus operating temperature. By selecting capacitors with a higher temperature rating, this can easily increase the expected life. Regardless of operating a capacitor well below its maximum specification to extend its life, many formulas limit the useful life of an electrolytic capacitor to 15 years due to material aging. If more of our electronics lasted 10 to 15 years, I doubt anyone would say they failed prematurely since their functionality would likely be obsolete by that time.

Why the premature failure of capacitors in these products? Did you know there is a global epidemic of capacitors failures that started in 1999 named the "Capacitor Plague"? (Go ahead, Google it - I'll wait.) This has lead to a rash of class action lawsuits with major electronics manufacturers going on the defensive. Some trace these failures to improperly manufactured capacitors from Taiwanese suppliers that undercut the price of previously dominant Japanese suppliers. As interesting as the claims of industrial espionage and theft of technology with the resulting lawsuits are, I doubt they will be the basis of the next John Grisham novel.

## Quality Failure?

Though these particular failures may have a root cause of improper component design and manufacture, I believe the Capacitor Plague is indicative of **fundamental failures in product quality as a result of the dis-integration of**  the global supply chain. Even worse are some brands whose sole involvement in the product is the receipt of a royalty check. I've had several cordless telephones branded "AT&T" and "RCA" that were designed and manufactured by third parties with little to no involvement from these formerly pioneering electronics companies. In fact, "RCA" is simply a trademark licensed by RCA Trademark Management to others who actually build and sell electronic products.

For some companies, the only quality concern appears to be whether they can get through the ever-shrinking warranty period without a rash of expensive returns. Formerly, most vertically integrated companies did an analysis between engineering, manufacturing, and quality organizations to determine the required quality and reliability levels. The objective in setting these levels was achieving a field failure rate below a given limit that supported the product's financial (warranty) objectives. These levels translated into reliability goals, test and qualification plans, and vendor management plans for each component in the system. With the increased use of outsourced manufacturing, fragmented supply chains, and higher levels of sub-system integration, accurate quality level planning has become exceedingly difficult if not impossible to achieve.

Extended warranty plans have become profit centers for consumer products. Only a few plans are offered by manufacturers themselves, so there is little incentive to improve product quality. Most plans are sold by retailers at a substantial profit and underwritten by insurance companies. Therefore, there is little pressure for retailers to push manufacturers for longer warranties. Doesn't it seem odd that most smartphones come with a hardware warranty (typically one year) less than the length of the wireless carrier contract obligation (typically

two years) required for the promotional price? Most wireless carriers aggressively market an extended warranty plan instead of working to increase the hardware warranty.

Capital equipment companies, including commercial computing and networking companies, do track their field failures since much of their equipment is on a support contract after the initial warranty period. These failures directly impact the equipment company's bottom line, so they keep careful track both to improve new designs and to set support pricing for older equipment. Rather direct feedback on quality is received when a prospective customer calculates total cost of ownership including quoted support costs.

Consumer brands, excluding perhaps products such as cars with long warranties and service plans paid for by the manufacturer, have much smaller direct incentives to manage their post warranty failure rates. Marketing should join the conversation with engineering, manufacturing, and quality to set appropriate quality goals. Yes, the product might survive the warranty period but if it dies prematurely, before the customer is ready to move on, the brand will become synonymous with junk.

Let us continue the discussion on my blog http://hightechbizdev.com. I welcome your comments!  $\blacklozenge$

IRA FELDMAN (ira@feldmanengineering.com) is the Principal Consultant of Feldman Engineering Corp. which guides high technology products and services from concept to commercialization. He follows many "small technologies" from semiconductors to MEMS to nanotechnology engaging on a wide range of projects including product generation, marketing, and business development.

## **UPCOMING 2013 MEPTEC EVENTS**

■ WEDNESDAY, FEBRUARY 13 **MEPTEC** Luncheon Biltmore Hotel & Suites, Santa Clara, CA

#### ■ MONDAY, MARCH 18

SEMI-THERM Executive Briefing: Thermal Management Market Visions & Strategies In Association with MEPTEC and **Electronics Cooling Magazine** DoubleTree Hotel, San Jose, CA

#### TUESDAY, APRIL 9 IMS 2013 Intelligent Medical Systems Conference

The University of Texas at Dallas In Association with MEPTEC

■ WEDNESDAY, MAY 22 11th Annual MEPTEC MEMS Technology Symposium Holiday Inn, San Jose, CA

Advanced

Labs, Inc.

Component

**Flex Packages** - 20µm Lines and Spaces -

## ACL is the only North American company focusing exclusively on the fabrication of **High Density Interconnects.**

**ITAR Registered**

Phone: 408.327.0200 Email: acl1@aclusa.com

www.aclusa.com

## **IC** Assembly **Advanced Packaging**