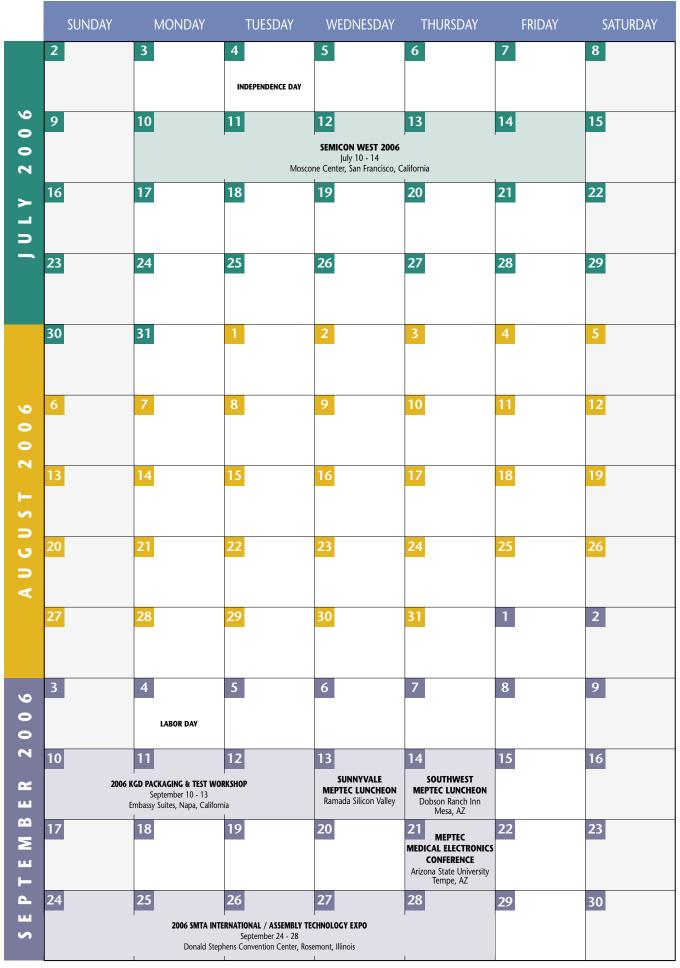

# Volume 10, Number 2 Volume 10, Number 2 Volume 10, Number 2

A Publication of The MicroElectronics Packaging & Test Engineering Council

**INDUSTRY NEWS**

Kulicke & Soffa Industries has relocated its corporate headquarters. *page 16*

**SUSS MicroTec AG** has installed the latest 300 mm technology in wafer probe systems at the nanoelectronics research center IMEC in Leuven, Belgium. *page 16*

**Advanced Interconnect Technologies (AIT)** has announced that it is expanding its world-class assembly and test factory in Batam, Indonesia. *page 16*

**March Plasma Systems** has established direct operations in Shanghai, China, that include an Advanced Applications and Demonstration Laboratory. *page 17*

### PAC TECH

**PacTech GmbH** announced that **Nagase and Co.**, a major trading company in Japan, acquired a 60% share of **PacTech GmbH** in February for an undisclosed amount. *page 17*

**STATS ChipPAC** has expanded its Quad Flat No-lead (QFN) packaging portfolio. *page 18*

According to final results reported by **Gartner**, **Inc.**, worldwide semiconductor revenue totaled \$235 billion in 2005, a 5.7 percent increase from 2004. 2005 revenue surpassed the semiconductor industry's previous record of \$223 billion set in 2000. *page 19*

SEMICON West returns to Moscone Center in San Francisco July 10 though 14. page 21

# **Medical Electronics:** Integrating Technologies

Merging the Microelectronic, Bioscience and Medical industries

One Day Technical Symposium Coming to Tempe, AZ September 21st ... page 5

### **MEMBER COMPANY PROFILE**

ose Street Laboratories, the parent company of FlipChip International, was founded in 2003 with a roadmap of providing leadership in product and service support to the electronics industry. RSL has been very active in the life sciences, renewable energy and homeland security markets.

FlipChip International's acquisition of Kulicke and Soffa's Flip Chip Division (K&S FCD) in Phoenix, Arizona, in February of 2004, enabled FCI with bumping technology services that are well known in the industry. This acquisition included standard flip chip and UltraCSP<sup>®</sup> as bumping offerings and is now FCI's Bumping Division. Since the acquisition, a specialized polymer process named Spheron<sup>®</sup> has been commercialized and is gaining popularity as a high performance solution for high speed applications such as Radio on Chip. page 22

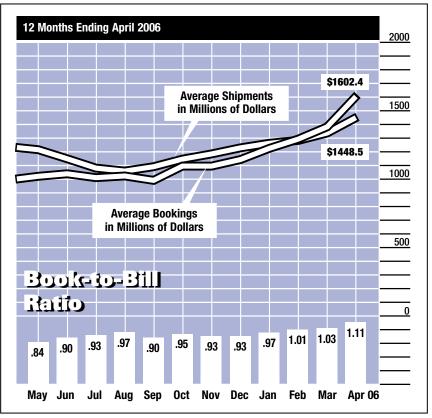

Semiconductor equipment bookings increase 60% over April 2005 level. *page 20*

# unique value

Like no other—our key strengths in chemistry and metallurgy come together to solve the most complex industry challenges. With precisely the right investments in the right places at the right time, we're uniquely positioned to help bring your newest ideas forward. Our ongoing research and development in chemistry, metallurgy, and the processes that bring them together—from our 300mm facility in Spokane, Washington, to our latest technology center in Shanghai,

China—ensure that wherever challenges arise, we'll continue to create solutions that solve them. And as a partner to 90% of the top semiconductor houses worldwide, our technology portfolio is consistently at the forefront of invention, empowering the global leaders of innovation. Honeywell Electronic Materials—delivering unmatched value today and tomorrow.

### Honeywell

Advanced Spin-on Materials • Electronic Chemicals • Precious Metal Thermocouples • PVD Targets & Coil Sets • Optoelectronics • Packaging

Get more information by visiting www.honeywell.com/sm/em Or call 1-408-962-2000

Volume 10, Number 2 A Publication of The MicroElectronics Packaging & Test Engineering Council

P. O. Box 222 Medicine Park, OK 73557 Tel: (650) 714-1570

Email: info@meptec.org

#### Published By MEPCOM

Editor Bette Cooper Design and Production Gary Brown Sales and Marketing Kim Barber Contributing Editor Jody Mahaffey

#### **MEPTEC Advisory Board**

Seth Alavi SunSil Jeffrey Braden Braden & Associates Philippe Briot P. Briot & Associates Joel Camarda Sipex Corporation Gary Catlin Plexus Tom Clifford Lockheed-Martin Rob Cole MiTech USA John Crane J. H. Crane & Associates

Jeffrey C. Demmin Tessera

Bruce Euzent Altera Corporation Skip Fehr

Julia Goldstein Advanced Packaging Magazine

Chip Greely Qualcomm

Anna Gualtieri Elle Technology

Bance Hom Consultech International, Inc.

Ron Jones N-Able Group International

> Pat Kennedy Gel-Pak

Nick Leonardi CMC Interconnect Technologies Abhay Maheshwari

Xilinx Phil Marcoux Corwil Technology Corporation

Bhavesh Muni Henkel Corporation Mary Olsson Gartner Dataquest

Marc Papageorge Semiconductor Outsourcing Solutions

> Jerry Secrest Secrest Research Jim Walker Gartner Dataquest

> Russ Winslow Six Sigma

MEPTEC Report Vol. 10, No. 2. Published quarterly by MEPCOM, P. O. Box 222, Medicine Park, OK 73557. Copyright 2006 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact Kim Barber, Sales & Marketing at (408) 309-3900, Fax (650) 962-8684.

www.meptec.org

### **Council Update**

t's that time again...summertime, and that of course means **Semicon West**, when thousands in the industry converge on Northern California to see the latest and greatest technology in the semiconductor industry. This year is the second since **SEMI** moved the entire show to San Francisco, integrating the *Final Manufacturing* segment of the show into the rest of the event.

We're pleased this year to be a part of Semicon West, as a technical session contributor to their TechXPOT (pronounced "Tech Spot"). According to a press release on the special sessions (see page 19), SEMI is building on the "show-within-a-show" concept, and the Test, Assembly and Packaging portion will focus on innovations in test, assembly and packaging, with exhibits, displays and technical presentations. There will be two **MEPTEC** sessions during TechXPOT: *The* Packaging Roadmaps session will be held on Tuesday, July 11 from 11:00 am to 12:20 pm, and Materials for Packaging session will be held on Wednesday, July 12 from 11:00 am to 12:20 pm, and will be held in the Test, Assembly and Packaging hall, right on the show floor. The SEMI press release mentioned above offers details of speakers and topics. Other organizations contributing are FSA, ITC and iNEMI. We hope you'll stop in to see these information sessions

We're pleased to announce another new MEPTEC Advisory Board member: **Bhavesh Muni** of **Henkel Corporation**. Bhavesh is currently their Director, Global Semiconductor Material Business and is responsible for development and execution of global business strategy for Henkel's semiconductor packaging material business. Welcome Bhavesh!

Our next event will be held on Thursday, September 21 and will be a divergence from our usual Bay Area venue: we've been invited to hold it on the **Tempe campus** of **Arizona State University**, in the beautiful Old Main building. The event, called "Medical Electronics – Integrating Technologies: Merging the Microelectronic, Bioscience and Medical Industries" will be co-sponsored by **ASU** and the **MacroTechnology Works**. The symposium will be co-chaired by MEPTEC member **David Ruben** of **Medtronics** and MEPTEC Advisory Board member **Nick Leonardi** of **CMC Interconnect Technologies**. See page 5 for further information.

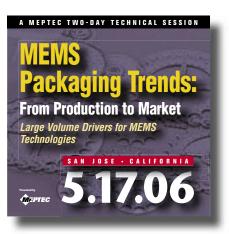

We also offer a follow-up look on a couple of past symposiums. These follow-ups are regular features in each issue. For each event, Jody Mahaffey of JDM Resources writes a pre-symposium article wherein she previews the program, interviews participants, and summarizes in an article which gets distributed to the trade magazines and on-line publications. After the symposium she updates and finalizes the article, and that is what you will see here. In this case the event was our special 2day symposium on May 17-18 called "MEMS Packaging Trends: From Production to Market". This event included a SEMI workshop on MEMS Packaging Standards, as well as an academic session where we heard about some of the leading-edge research in MEMS technology. In addition, Julia Goldstein, editor at Advanced Packaging magazine, follows up with a review of our February event on "2nd Annual The Heat is On: Thermal Management Solutions in Semiconductor Packaging". See page 6 for both of these summaries. CDs of the proceedings for both of these events will soon be available on the MEPTEC website at www.meptec.org, or call Bette Cooper at the MEPTEC office to order today - 650-714-1570.

One of the feature articles this issue is con-

### **Issue Highlights**

| MEPTEC Events Follow-up                                           | 6  |

|-------------------------------------------------------------------|----|

| Industry Analysis                                                 | 10 |

| University News                                                   | 13 |

| Industry News                                                     | 14 |

| Member Company Profile                                            | 22 |

| Feature Articles                                                  |    |

| • Low Cost, High Performance<br>Silicon Packages                  | 24 |

| <ul> <li>Materials Declaration for<br/>Everyone</li> </ul>        | 28 |

| • Stress Free Modeling                                            | 30 |

| <ul> <li>Airflow Optimization for<br/>Enhanced Cooling</li> </ul> | 32 |

| Event Calendar                                                    | 37 |

| Editorial                                                         | 38 |

### MEDIC Council Update

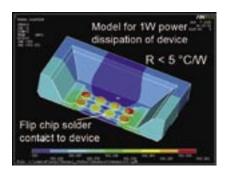

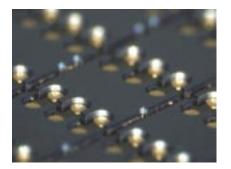

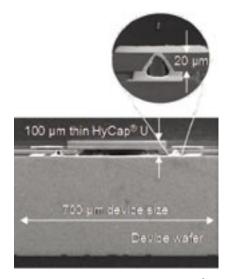

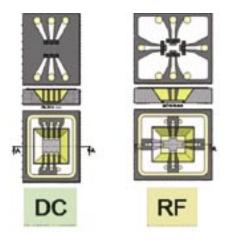

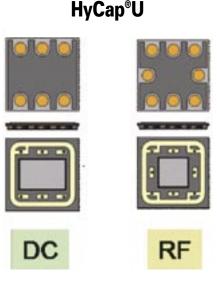

tributed by a new MEPTEC Corporate member company, **Hymite. Dr. Jochen Kuhmann** and **Andreas Hase** write about "*Low Cost, High Performance Silicon Packages*". This is a very interesting look at how silicon as a packaging material offers exceptional thermal and electrical performance. We were pleased to have Hymite as a speaker on the same topic at our 2005 MEMS Packaging event; we'll see if we can get them to come back in 2007 and give us an update. See page 24 for this informative piece.

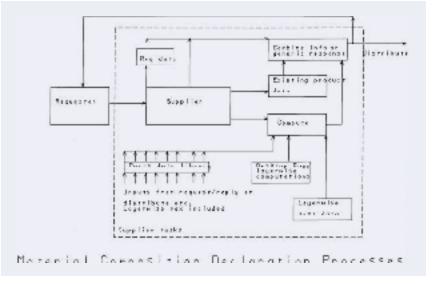

Our other feature article is an informative look at "*Materials Declaration for Everyone*". Dr. N. Nagaraj of Papros, Inc. offers a discussion on exchanging material content data in the form of Material Composition Declarations. Sometimes the practical management issues in our industry are overshadowed by the cutting-edge technology, so we're pleased Dr. Nagaraj has taken the time to explain this important element of data management. It really is a best practice for supply chain management.

Our regular Thermal Management contributor and MEPTEC Corporate member company, Advanced Thermal Solutions (ATS), writes about "Airflow Optimization for Enhanced Cooling", and can be found on page 32. Norman Quesnel discusses why airflow characteristics are so important to device manufacturing. We appreciate their continued contributions on this important topic.

Our Editorial this issue is contributed by new MEPTEC Advisory Board member, and frequent speaker at various MEPTEC symposiums, Tom Clifford of Lockheed Martin. Tom offers himself up as our "Technology Reporter", and takes a very interesting and introspective look at future technology, and what future community will be responsible for coming up with this new technology. He researched trade magazines, newspaper sources, and even high school and junior high school Science Fair programs to find out if our kids are focusing on more than what he calls "fashionable" technology, such as cool music gadgets, video games, etc. I think you'll find his comments and findings fascinating...see page 38. If you've ever met Tom you'll know that he's a very smart, inquisitive and reflective guy; we'll see if we can get him to contribute more "Technology

Reporter" pieces in future issues!

Our Industry Analysis coverage this issue is contributed by Bob Johnson, Klaus Rinnen, Jim Walker and Mary Olsson of Gartner Dataquest (Jim and Mary are also long-time MEPTEC Advisory Board members). This article takes a look at the impact on the semiconductor equipment segment of the industry, and how historically the equipment industry responded to changing technology by succumbing to semiconductor financial pressures. They are suggesting that things are changing; see page 10 for their article titled "The Evolving Changes for the Semiconductor Equipment Industry".

Our Member Company Profile this issue is MEPTEC Corporate member Flip Chip International. Theirs is a really interesting success story: it tells the tale of two visionaries, Bob Forcier, President/CEO and Dr. Joan Vrtis, CTO of Rose Street Laboratories (RSL). They wanted to provide flip chip and wafer level packaging services in packaging, operate globally to support worldwide marketplaces, incorporate new IP into products and services, and form a team to make this happen, and FCI was born. You'll see that every February since 2004 FCI has hit a major milestone, and the question is asked, "Will we have to wait until next February to hear what's next?". Find out by reading their story on page 22.

Our "University News" section this issue is not really about a classic academic institution, but it is about a similar type of research institution that works with academia and industry alike on electronics research. This is also our first coverage of an institution outside the U.S. It is IMEC, and is located in Leuven, Belgium. IMEC is Europe's largest independent research center on nanoelectronics and nanotechnology. They have developed a powerful network of over 500 partners including IC manufacturers, equipment and material suppliers, universities, research institutes, etc. Coincidentally, we received a news release recently from SUSS MicroTec about their collaboration with IMEC by installing their latest 300mm technology in wafer probe systems at the nanoelectronics part of the research center. They will continue their alliance with IMEC in the following years on technology enhancements. See their story on page 13.

We'd like to thank all of our contributors for making this a great issue. If you're reading our publication for the first time at the Semicon West show, or another of the many events where we'll be distributing this issue, we hope you enjoy it.

Thanks for joining us!

•

### MEPTEC Welcomes New Advisory Board Member

#### Bhavesh Muni

#### Director, Global Semiconductor Material Business Henkel Corporation

Bhavesh Muni has more than 18 years of experience in various materials for electronics assembly & semiconductor packaging. His experience ranges from hands on R&D Chemist to technical/application services and leading up to sales & marketing aspects of electronics material business. Bhavesh is currently Director, Global Semiconductor Material Business at Henkel Corporation, responsible for development and execution of global business strategy for Henkel's semiconductor packaging material business. Prior to Henkel Bhavesh held positions at Thermoset, Lord Corporation; Emerson & Cuming/Ablestik; Olin Hunt Conductive Materials; and Pacific Polytech/Namics. Bhavesh holds an MS in Polymer Science from the University of Detroit, Detroit, MI; a BE in Chemical Engineering, REC, Srinagar, India. He has published several technical papers on Interpenetrating Polymer Networks (IPNs).◆

In association with

MacroTechnology Works at Arizona State University

### A SPECIAL ONE-DAY TECHNICAL SYMPOSIUM

September 21, 2006 • Arizona State University Tempe Campus, Tempe, AZ

# **Medical Electronics:**Integrating Technologies

### Merging the Microelectronic, Bioscience and Medical Industries

The Medical Electronics Industry continues to show momentum in growth, with strong demand and expectations coming from the consumer, as well as technology advances expanding the scope of the electronics capability. Can technology advances keep up? Can divergent industries collaborate effectively and work together to meet these expectations?

This First MEPTEC Symposium on Medical Electronics will bring together technical and business professionals from a variety of disciplines and industries dedicated to the advancement and integration of state-of-the-art technology in medical products.

Sessions will include:

- Industry Overviews

- Microelectronic, Bioscience and Medical Perspectives

- Industry Trends and Integration of Technologies Materials, RF Technology, Power Sources and Design

- Industry Growth within the Enabling Technologies Semiconductor, Nanotech, Optoelectronic and MEMS

- Opportunities in Medical Electronic Products Hearing Aids, Pacemakers, Monitors, X-Ray & Others

REGISTER ONLINE TODAY AT WWW.MEPTEC.ORG

### MEDIC Event Follow-up

### MEMS Packaging – The Saga Continues

Jody Mahaffey JDM Resources

ccording to market research company YOLE Développement, the MEMS market reached \$5.1 Billion in 2005 and is expected to reach \$9.7 Billion in 2010, representing a compound annual growth rate of almost 15%. For the fourth year in a row, MEPTEC, the MicroElectronics Packaging and Test Engineering Council, brought together leading experts in the MEMS field to discuss the topic as it relates to packaging in its technical symposium "MEMS Packaging Trends: From Production to Market" held on May 17 & 18th, 2006 in San Jose, CA. Some of the speakers at this conference offered insights into the changing and challenging world of MEMS.

Most analysts agree that MEMS based products are forecasted to grow significantly in the next ten years. We asked our experts what they thought the driving factors are for that growth. Most agree that one of the largest reasons for this growth will be new applications.

Tom Clifford of Lockheed Martin Space Systems was a speaker in the *End User Applications* session of the symposium. He believes that, "MEMS growth depends on the product and the corresponding process. There are scores of current and potential MEMS applications of all sorts. Success depends on the profoundly new capabilities that welldesigned and positioned MEMS products will provide."

Mathieu Potin is a Market Analyst for YOLE Développement out of Lyon, France and presented in the Industry and Market Overview session of the symposium. Potin believes growth of the MEMS market goes beyond just new applications. "The development of the MEMS markets will of course be related to new applications," explained Potin, "but the primary market growth would depend on the ability of MEMS manufacturers to supply from the component to the module." Potin's definition of a module is a MEMS product which can provide a function instead of just a sensor (component) alone. Potin believes that device manufacturers will be pushing a module offer (compared to a component offer) in order to attract added value.

Many MEMS based products such as DLP, accelerometers, pressure sensors and printers, can already be found in the general marketplace. With the introduction of so many new applications we should expect to see many other products in the near future.

"MEMS microphones are a major growth area for applications such as hearing aids and cell phones," according to **John Heck** of **Intel**. "RF MEMS switches are entering the marketplace, starting in test and measurement equipment, and we may expect to see them in handheld wireless devices within the next few years. Also a wide variety of medical devices will be seen in the near future." Heck was the Session Chair for the *Enabling Technologies* session.

Mark Crockett of Applied Materials said that people should expect to see MEMS sensors and actuators in more "user-centric" devices like set top boxes that sense viewer's emotions and adapt accordingly. "We may also begin to see wearable devices to optimize worker productivity and effectiveness," said Crockett, who presented in the SEMI Standards Workshop on the second day of the symposium.

Potin added that, "Micro fuel cells are at a key development stage in Japan with companies like NEC, Fujitsu, and Toshiba, and are likely to enter the cell phone market in 2007-2008. Several service providers including NTT and KDDI have already presented mobile phone models with integrated micro fuel cells. Europe and the US are also engaged in such development through companies such as STM and Infineon."

Alvin Barlian, of Stanford University, believes that as the MEMS field matures, more development of MEMS products will be driven by academic and industrial labs. According to Barlian, relatively newer applications may include biological and chemical sensing for military and homeland security as well as transportation infrastructure systems, structural health, and environmental monitoring. The rebirth of aerospace and telecommunication industries will also increase the demand for more advanced MEMS products. In addition, advances in material science play a major role in the growth of MEMS by

enabling innovative unconventional fabrication processes. Barlian was a speaker in the *Academic Workshop* which was part of the second day of the symposium.

Other than new applications, cost reduction and increased reliability still remain critical drivers for growth in the MEMS industry. Heck feels that significant competition in the foundry business, as well as common availability of MEMS-specific tools such as wafer bonders and deep silicon etchers are key to lowering costs.

"Lower costs and improved reliability will encourage the expansion of MEMS into new markets," added **John Crane**. "As improved assembly processes yield lower costs and better reliability, new markets will proliferate." Crane represents **Boschman Technology** who presented in the *Advanced MEMS Packaging Trends* session.

Ken Yang of Honeywell believes the growth will be driven, not only by lower cost and better performance, but also by ease of manufacturing and government policy requirements. Yang was a speaker in the *Advanced MEMS Packaging Trends* session.

Clifford agreed that cost and reliability aren't the only issues, saying that, "Most MEMS concepts must confront and control particulate and molecular contamination. Furthermore, specific challenges include CTE mismatch and thermal management; passthru of optics/gases/liquids/signals; vacuum packaging; and subtle but crucial materials compatibilities. "

For people who have been watching the MEMS market for many years, it seems that changes have come slowly. However, some significant changes have occurred over the past year according to our experts. Heck explained, "MEMS foundry consolidation has started to occur, and this trend will likely continue. Also, many groups are at the cusp of commercializing in-situ, or self-packaging methods for MEMS, where the mechanical elements are self-sealed during the fabrication process. This enables the MEMS die to be treated much like a standard IC throughout the packaging process, thereby reducing packaging cost significantly."

Clifford believes many things are chang-

### Maine Event Follow-up

ing for MEMS. "Certainly one enabler is maturing design software keyed to multiphysics solutions and to the particular fab process," explained Clifford. "Another is growing materials expertise, riding on nano-lab developments. Another enabler might be turn-key development services structured to ease and accelerate the painful transition from concept to manufacturable prototype. Another bright light is the emergence of 'packaging' in academia, as a respected and pivotal skill-set."

As new MEMS devices are developed, the packaging industry will continue to struggle with the question of whether to use existing technology or develop new technology. This question becomes even more important when getting MEMS products into high volume. Many people are divided on this. Heck believes that current packaging solutions will continue to evolve and drive down cost, but also new packaging methods will begin to arrive in commercially-available products in the near future. "In order to get to high volume production," explained Heck, "ultra-low cost packaging methods are needed, both in the form of cost reduction on existing methods (such as glass frit wafer bonding), and the advent of new self-sealed MEMS devices. which will enable significant cost reduction."

Clifford agreed that both existing and new technology will be needed depending on the product. "Some, including hermitic fluidics, optics, integrated sensors, etc. might currently be package-limited. Others might work fine in tailored conventional or vacuum-finessed packages. In every case, the package is a major challenge."

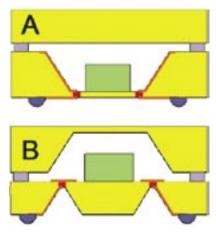

But many people, like **Chris Lee** of **Quantum Leap Packaging**, feel that existing packaging must be made to work in order to keep costs low. To this end, according to Lee, companies like Quantum Leap are combining existing packaging technology with new material sets such as QLP's Quantech<sup>™</sup> high performance polymer material to meet the changing demands. "As MEMS devices become more complex," explained Lee, "devices are much more stress sensitive and prone to lower performance yields. Managing the device stress is a key in packaging in high volume." Quantum Leap Packaging presented in the Enabling Technologies session.

Crane added, "As MEMS products have migrated from ceramic packages to BGA and/ or QFN package types, the ability to move to high volume production has become easier and easier."

One of the biggest questions for packaging MEMS has always been and continues to be, where is the packaging done, in the front-end or the back-end? Both sectors are working on new packaging technology which will enable the proliferation of MEMS.

"In-situ packaging is beginning to pay off," according to Heck. "This technology comes directly from the front-end fabrication side." Yang agreed that wafer level packaging and wafer level vacuum packaging done at the front-end are critical to move MEMS forward.

Crane believes that the ability to successfully mold exposed die MEMS, such as finger print sensors or optical sensors, using transfer molding and film assisted molding, has allowed for significant assembly cost savings and improved capability. Film assisted molded products are free of mold compound flash and bleed. Lower cost and a reliable process at the back-end have enabled such MEMS devices to proliferate.

There are other areas of concern for MEMS beyond packaging. One of these is Intellectual Property. With the increasing trend toward overseas manufacturing in the past few years, IP has become a critical issue in all semiconductor areas and perhaps more so for MEMS products. Clifford believes IP is a bigger problem for MEMS. He explained, "IP resides in and must accommodate the one fact that characterizes all MEMS products: the inseparable linkage of design / process / material / fab tooling / test methodologies / process techniques / etc. Any IP and business arrangement (licensing, scale-up, product proliferation, supply-chain expansion, etc.) must deal with that.

Heck agreed saying, "MEMS devices are so much more process-dependent than IC's – you can easily port a new CMOS design from one foundry to another. But the IP inherent in a MEMS device is in both the design AND the process. Therefore foundries and companies may possess key differentiators based on processes they develop."

Another area of concern for MEMS is standardization. This year's MEPTEC conference was extended to two days to include a half-day workshop, in conjunction with SEMI, to discuss standardization for MEMS. MEMS offers a unique challenge when it comes to standardization because so many of the devices are applications specific. "Applications that are customized, generally require greater up front cost to achieve economies of scale," explained Crockett. "Standardization and level of difficulty will be driven by a variety of market forces. Unique applications will only leverage standardized solutions if the standards exist. Today, such standards for MEMS are not an option. As individual solutions proliferate, advantages in standardized solutions grow. For example, if five products perform the same function to a customer and only one of those products offers features in compatibility and lower cost of ownership through standardization, then the decision of which product to buy is simple. Establishing this differentiation is critical in newly shaped markets."

Heck believes that because MEMS devices are all made for different purposes and in different markets, standardization will only

work at a very basic level. "We already have several relatively standard process modules for MEMS. For example, glass frit wafer bonding is so common these days that it may be considered a standard; this is in part due to the availability of wafer bonding and screen printing tools. I don't think we will ever see full processes that are standard in the sense that many devices with different functions can be made with a single MEMS process."

Though it may be difficult, standardization is still important, even with application specific MEMS products, according to Yang. "At least individual processes should be standardized so that you can use any subset of them to apply to your specific process set. It can then enable the foundry to group similar processes together to make a volume production from various products."

With or without standardization, the MEMS market continues to grow. According to Marlene Bourne of Bourne Research, funding of MEMS start-ups exceeded \$500 million in 2005, with the average funding received per round at approximately \$13 million. Bance Hom of Consultech International and Symposium Co-Chair said, "MEMS start-ups today are more market driven rather than technology driven...more direct application now, rather than pie in the sky fantasy we may have seen in the past." One thing is for certain, even with all the issues and challenges facing MEMS, the technology is here to stay and getting stronger every day.

#### Julia Goldstein Advanced Packaging Magazine

hermal management continues to be a "hot" area, and MEPTEC's second annual "The Heat is On" symposium on February 16 packed the hall despite the plethora of events covering the topic. Keynote speaker **Herman Chu** of **Cisco** divided cooling into two categories – heat transport and heat transfer – and explained that efficient heat transfer is critical

### MELTE Event Follow-up

for data centers. Customers aim to achieve sufficient cooling using traditional technologies, preferring to avoid liquid cooling and other technologies that require infrastructure change. Reliability, availability and serviceability, as well as cost, are all hurdles for new technology. Chu suggested that the push to minimize energy usage could drive future data centers to be rated on efficiency, similar to the "Energy Star" ratings on home appliances.

**Professor Van Carey** from **UC Berkeley** discussed the relationship between the theoretical maximum heat flux removal rate for a vaporization process and heat flux achieved in mini and micro heat pumps. The ratio between the actual and maximum heat flux is one measure of the efficiency, which can be increased by optimizing the coolant pressure and selecting a mixture of coolants, for example water and alcohol.

**Debendra Malik** of **Intel** discussed the 2005 International Technology Roadmap for Semiconductors (ITRS) and stated that the ITRS recognizes that packaging is a limiting factor toward improving cost and performance, and that thermal management is given significant attention in the Assembly and Packaging chapter. The focus is hot spot mitigation using heat spreaders or thermo-electric cooling. Thermal interface materials (TIMs), spreader design and cooling technology are listed as areas for improvement.

While ITRS is just now recognizing the need to focus on thermal management, heat dissipation has been addressed for decades. **Sandra Winkler** of **Electronic Trend Publications** described solutions from the 1950s that used metal screws and thermal grease to conduct heat away from power transistors. Winkler gave an overview of current thermal management materials as well, including TIMs, fans, heat pipes, and cold plates. She described substrates containing metal layers specifically designed to act as heat spreaders.

Devesh Mathur of Honeywell discussed the connection between the surface condition of heat spreaders (flatness, roughness, plating) and TIM performance by showing thermal resistance tests of TIMs using various test blocks. Mathur also described new TIMs, including polymer solder hybrids filled with a high conductivity filler and low melting solder. During processing, the solder melts and surrounds the filler, providing a direct thermal path through the thickness of the TIM. Scott Allen of Henkel described a two-part adhesive TIM applied in separate beads, which then mix when the components (a package and a heat sink, for example) are assembled. Since these TIMs are solid materials they tend to perform better than chemically activated TIMs on ceramic packages, presumably since the solvent in activated materials can absorb into the ceramic, reducing TIM effectiveness. Heatcured TIMs are another solution for ceramic packages.

The thermal performance of heat sink base plates can be improved by using a vapor chamber instead of solid copper or by increasing the thickness of the base plate, as **Kaveh Azar** of **Advanced Thermal Solutions** explained. He discussed the difficulty in achieving sufficient flow rate in micro-pumps and proposed an alternative solution, a BGA with a built-in, water-cooled heat spreader.

Hot spot mitigation was a recurring theme, and **Nanda Gopal** of **Gradient Design Automation** warned package designers to consider the chip as a dynamic device with variable temperature distribution rather than a simple heat source in their models. Gopal described the benefits of 3D thermal design incorporating input from both chip and package designers.

**James Forster** of **Wells-CTI** described a solution that actively controls the temperature and voltage applied to individual socketed packages during burn-in, holding them at the desired burn-in temperature and turning them off individually if they fail, while maintaining the burn-in oven at a lower temperature. This technology works for low power devices, but higher power devices can require passive or active cooling during test. **Jerry Tustaniwskyj** of **Unisys** discussed incorporating both heating and cooling capability into test sockets.

# Fully automatic integrated production line

The most complete range of equipment the industry

Technical information: www.fkdelvotec.com/eng/produkte.html

F&K Delvotec Bondtechnik GmbH Daimlerstr. 5-7, 85521 Ottobrunn, Germany TeL +49 89 62 995-0, Fax +49 89 62 995-100

### DIE PRODUCTS Making Mobile Work

Register online at www.napakgd.com by August 1, 2006 for the best rate.

### 2006 KGD Packaging & Test Workshop September 10-13, 2006 Napa, California http://www.napakgd.com

The KGD Packaging & Test Workshop returns to Napa, California this September for 3 days of presentations on leading technologies, supplier exhibits, and networking opportunities for die products practitioners from across the industry who are *making mobile work*.

The explosion of digital content for portable electronics is only possible through assembly and packaging technology that relies on die products to achieve the needed functionality in the smallest footprint.

Join us at the KGD Workshop for a focused, highly informative interchange of ideas and information on all aspects of the die products industry in a relaxed, informal setting.

For complete details and online registration, visit http://www.napakgd.com

#### **WORKSHOP TOPICS**

- Applications of Die Products

- KGD (Known Good Die) Processes

- SiP & Die Products Test

- 3D Packaging

- Memory & Rf Die Products

- Business Issues & Market Trends

### **EVENT HIGHLIGHTS**

- Free pre-workshop tutorials for all attendees

- Three days of technical presentations

- Special invited presentations

- Supplier exhibits and reception

- Networking events including winery tour & dinner

Hosted annually by the Die Products Consortium (DPC). Online at http://www.dieproducts.org

### MEDIC Industry Analysis

### The Evolving Changes for the Semiconductor Equipment Industry

Bob Johnson, Klaus Rinnen, Jim Walker and Mary Olsson Gartner Dataquest

he steady and relentless advancement of semiconductor manufacturing technology provides the foundation for the long-term growth of the industry. As summarized by Moore's Law in its various forms, the cost to produce a single function, whether it be a bit of memory or a single gate on a logic chip, has decreased by about 50 percent every two years since the dawn of the integrated circuit age in the 1960s, and there is every expectation that this will continue.

This progress in design and manufacturing technology was neither easy nor inexpensive. Over the years, the industry created a methodical approach to new technology development that has served it well. Basic research in advanced semiconductor manufacturing technology is carried out by the leading integrated device manufacturers (IDMs) (Intel, Samsung, TI, Infineon Technologies, Renesas Technology, Toshiba and others) or through industry technology development alliances (for example, the IBM alliance with AMD, Chartered Semiconductor Manufacturing, Samsung, Sony and Infineon). This research is turned into plans for future technology development at the detailed process level. In a parallel effort, the major semiconductor manufacturers from around the world, working through International Sematech, develop and publish the International Technology Roadmap for Semiconductors, which delineates industry consensus regarding the directions and new processes needed for future semiconductor production.

Although the semiconductor manufacturers develop the overall process flows at the fab level – and may even develop specific processes in their labs – it is generally the equipment companies that turn these recommendations into productionworthy equipment when it is needed. This model worked reasonably well as long as the majority of the advances needed for the next technology node required scaling existing technology. In most cases, the technology risks were few, and equipment manufacturers could meet most of the demands of the next process generation with upgrades to existing products.

This model frequently broke down if new technologies or major changes in materials were needed. In such cases, equipment R&D efforts must begin years before production process development at the semiconductor manufacturers. Initial schedules are developed with milestones for evaluation tools but with no guarantee of market adoption. The introduction of new technologies was often delayed for years beyond initial expectations because new life was found for existing methods. Some prime examples of this were in the lithography field. For example, 248-nanometer (nm) deep ultraviolet lithography was initially developed for implementation in the late 1980s, but it didn't make the mainstream until almost 10 years later. X-ray lithography was once touted to be the next technology after 248 nm, but that never happened. Originally, 193-nm lithography was considered a requirement for 0.18-micron production, but the industry waited four more years until 90 nm started production. Once viewed as essential for 65-nm production, 157-nm lithography dropped off the road map entirely. On the materials side, low-k dielectrics, tungsten, high-k gate materials and others have all seen their deployment slip from initial projections by years.

Although each of these developments involved a limited portion of the industry, the move to 300-millimeter (mm) wafers strained the resources of the entire equipment industry. Originally scheduled for initial widespread use in 1997 or 1998, it wasn't until 2003 and 2004 that the first large 300-mm fabs ramped up fully. As a result of this slip and the continued large R&D investment required – with no returns for an extended period – the return on investment (ROI) in 300-mm technology development for equipment companies plummeted.

Looking forward, the need for the development of new processes and new materials increases with each new technology node. Although lithography appears to have settled at the 193-nm technology node for another couple of generations, new materials will be needed for each node as the industry progresses. But there is no definitive list of necessary new processes. Each new development undertaken by the equipment companies faces the risk that its ultimate acceptance by the industry will be either delayed or indefinitely postponed.

These financial risks are becoming significant and are increasing at a time when the industry is facing lower growth rates and tighter margins. Lower profitability breeds risk aversion and creates an environment in which equipment companies will be hesitant to make the necessary investments in process R&D without some reasonable guarantee of a decent ROI on the project.

Thus, the question of whether the industry can keep on the path dictated by Moore's Law for the next decade or so depends not as much on whether we can develop the necessary technology, but on whether it can be done profitably with reasonable and manageable financial risks.

#### **Gartner Dataquest Perspective**

A number of significant market and structural trends facing the industry will lead to a rethinking of traditional business models for developing new technology. Each of these trends leads to a market demonstrating many of the characteristics of a mature industry: slower growth, tighter margins and fewer players. Gartner Dataquest has developed a series of Strategic Planning Assumptions as listed below that can help guide long-range planning efforts of industry participants.

#### 1. The growth rate for the wafer fab equipment (WFE) market will parallel that of the semiconductor market through 2014.

During the past few years, the overall growth of the semiconductor market has slowed as it moved from a highgrowth emerging market segment to a more mature, but still dynamic, industry. Present forecasts show that the long-term growth of the semiconductor industry has

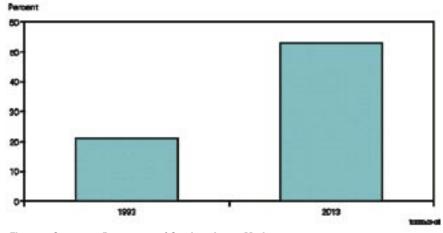

Figure 1. Consumer Percentage of Semiconductor Market

slowed to a per-year projected average of about 9 to 10 percent for the near future. The slowing growth rates will also affect the semiconductor equipment industry, because the demands for additional capacity and capital investment to support that growth will also decrease.

### 2. By 2014, greater than 50 percent of chip sales will be for equipment markets targeted at consumers.

As shown in Figure 1, consumer applications have been gaining an increasing share of the semiconductor market, and they will likely eclipse business and commercial applications in the next decade. The implications of this shift on the industry are profound. The consumer market is extremely price-sensitive, putting downward pressure on profit margins. Product lifetimes are shorter than for commercial products, and the timing of market introduction is more critical. These markets are driven by fashion, features and fad; productivity and function have less intrinsic value than in commercial markets. Much of the value for consumer products lies in the software, which creates brand differentiation and brand loyalty.

#### 3. During the next 10 years, the key differentiation for semiconductor vendors will shift more strongly from silicon manufacturing to IP and design.

With the advent of foundries providing leading-edge capabilities, silicon manufacturing is becoming more of a commodity, and the primary differentiation for devices will shift from manufacturing to chip design, software and other forms of non-manufacturing IP. Although manufacturing technology will always be considered a key core competency for the largest IDMs, many of the leading semiconductor designs will base their market position on product factors other than manufacturability. With manufacturing drifting more and more toward a commodity status for much of the industry, the margins it once commanded will also experience pressure. For materials and equipment suppliers, enabling a commodity and not a key differentiator will lead to continuous price pressures and reduced margins.

### 4. By 2014, fewer than 25 manufacturers will be building new fabs.

As any industry matures, consolidation becomes inevitable. This is happening in the semiconductor industry and will continue as the present industry leaders become the only ones that can afford to build new fabs. Many of the smaller manufacturers that are currently running their own fabs will move out of manufacturing and become fables companies, relying on the major foundries for their manufacturing. This consolidation reduces the number of potential customers for equipment manufacturers and makes establishing successful long-term relations critical.

#### 5. By 2014, fewer than 10 equipment suppliers will satisfy 80 percent or more of semiconductor manufacturing equipment demand.

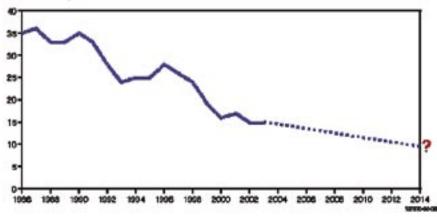

As shown in Figure 2, the equipment industry has already progressed significantly along the path to consolidation and is likely to continue to do so. As industry growth rates slow and margin pressures increase, only larger equipment companies can afford to make the R&D investments necessary to remain competitive. In addition, as critical equipment markets coalesce to two or three key suppliers, equipment companies can have the market presence to resist profitability-destroying pressures from the major semiconductor manufacturers.

The direct result of these trends leads to the following new rules for manufacturing:

• Only the paranoid will survive - Caution prevails in upturns; manage capacity and investment carefully.

• Big manufacturers can ignore business cycles and invest counter-cyclically to strategically prepare for upcycles.

• Focus on core competencies - Outsource when possible but only if it does not affect core competencies.

• Think bigger - Alliances, mergers and acquisitions can provide increased financial leverage.

• Timetables are collapsing, but being there first reaps profits.

• Time to anything" assumes paramount importance.

• Enabling time savings leads to higher profits and ROIs.

Don't slow the pace of innovation.

The industry has been facing increasing pressures on its profitability since

Number of Companies

Figure 2. Equipment Companies Generating 80 Percent of Total WFE Revenue

### Made Industry Analysis

the mid-1990s, when the long-term revenue trend turned downward. Although the initial impact of this was obscured by the wild gyrations of the dot-com boomand-bust cycle, the results have been the same: increased efforts to be more costefficient across the board. This approach is evidenced by the increasing importance of cost of ownership on equipment suppliers in the late 1990s and by the industry dictating increased capital and materials efficiency for 300-mm equipment. Many of the major semiconductor manufacturers have formed technology alliances to alleviate the costs of leading-edge research. The pressure to develop new process and new equipment is still directly on the equipment manufacturers, which are expected to develop new processes on demand, with little or no guarantee of an acceptable return on their R&D investment or even assurances that the newly developed technology will be selected for production. The current practice is to encourage multiple equipment suppliers to solicit competitive parallel developments and then stage a winner-take-all, best-of-breed competition for the production business. Although this approach may lead to slightly superior processes in the short run, the long-term effect is an inefficient use of scarce R&D resources on an industry-wide level.

As the relentless march of new technology continues, these financial pressures will continue to weigh on even the largest equipment companies. This factor leads to the final Strategic Planning Assumption.....

6. By 2014, the existing R&D model will have to change drastically; equipment companies will not be able to afford product development with no guaranteed ROI.

A number of possibilities will provide acceptable ROIs for equipment company R&D in the near term:

• Consider equipment company process development alliances and mergers similar to the technology development alliances in the semiconductor arena.

• Demand a firm purchase commitment before agreeing to develop specialized processes. Don't agree to an open-ended development project that has no guarantee of an acceptable ROI. Consider a nonrecurring engineering model to fund development of unique processes. Make the semiconductor manufacturers share the financial risk.

• Create joint technology development consortia between semiconductor manu-

facturers and semiconductor equipment manufacturers. Shift the focus from competitive best-of-breed tool evaluation to competitive equipment supplier evaluation so that participation in joint development efforts guarantees equipment purchases. Some consortia, such as IMEC in Europe and Albany Nanotech, are already involving major equipment companies.

#### Summary

Historically, the industry has relied on the big semiconductor manufacturers putting pressure on the smaller equipment suppliers to meet their technology and cost objectives, with little or no consideration of the consequences. The equipment industry responded by succumbing to semiconductor financial pressures. The stakes for the entire industry are too great for this modus operandi to continue. More than ever, future industry growth depends on achieving the cost and performance goals of Moore's Law, but it is getting increasingly difficult to do so. The industry's lifeblood is its manufacturing technology, and it must develop new and more-effective ways to maximize returns from an increasingly scarce R&D dollar.

### the **new** world of advanced packaging

### Celebrating 50 years of Innovation

#### Fico AMS-W

- Revolutionary MAP molding system

- Double output: minimum cycle time and

antimized design

- optimized design • Low investment costs

- Up to 40% reduction in cost of ownership

- Up to 25% compound reduction

- Mold open time only 12 sec.

- Dynamic temperature control

- Top edge gating (no gold layer required!)

- 50% floor space reduction

#### Fico BrightLine™

With automatic tray handler Your ultimate flexible high speed Memory Card singulation solution:

- Modular machine concept

- Free programmable curve linear cutting

- No consumable usage

- Integrated ultra sonic product cleaning

- High UPH (up to 2200 for micro SD)

- Inspection & Sort functionality

- Low noise level (<75 dB)</li>

High Flexibility: 1 system for all card types

Fico also offers a full range of modules and tools for a big variety of IC's to cover most processes such as Laser Marking, Singulation, Inspection, Off-loading and Sorting into Tube, Tray or Bulk.

#### Fico Singulation MISS II+

Interposer singulation system for BGA, CSP and QFN

Exciting new features to be introduced this year:

- · Sorter head now allows sorter UPH of more than 18k

- · User interface with new functionality for easy product set up

- Auto Saw Diameter correction that requires zero cycle time

- and measures the blade diameter every single product strip • More features to be announced later this year

member of Besi group -

Fico BV, Ratio 6, 6921 RW Duiven, The Netherlands, Tel.: +31 263196100, Fax: +31 263196200, sales@fico.nl, www.besi.com

### **MEPTEC** University News

## **NIEC** Research Center on Nanoelectronics and Nanotechnology

hree to ten years ahead of industrial need

Katrien Marent Corporate Communication Manager IMEC

s Europe's largest independent research center on nanoelectronics and nanotechnology, IMEC has over 1,450 people from all over the world working together in this institute with headquarters in Leuven, Belgium. They develop design methodologies, IC process and packaging technologies and enabling technologies for the electronic systems of the future. IMEC's research bridges the gap between fundamental research at universities and technology development in industry. Its unique balance of processing and system know-how, intellectual property portfolio, state-of-the-art infrastructure and its strong network of companies, universities and research institutes worldwide position IMEC as a key partner for shaping technologies for future systems.

#### A Broad Range of Research Activities: IMEC's Strategic Research Programs

IMEC's know-how on this broad range of research topics is gathered in several strategic research programs. First, to cope with the ever continuing scaling of transistor dimensions, IMEC has set up a centralized research platform. Here, leading IC-manufacturers, together with renowned equipment and material suppliers collaborate to find innovating solutions for the **sub-45nm technology** nodes. The platform includes technology programs on lithography, substrate modules, gate stack, interconnects, ultra-clean processing, emerging devices, germanium devices and others. Next to these 'core' programs, technologies to add extra functionalities to the chip are being developed. Meanwhile, IMEC looks further into the future. New technologies like carbon nanotubes, semiconducting wires and spintronics shall be needed within ten to fifteen years to explore the possibilities of semiconductor applications. The fundamental knowledge for these innovations is already studied at IMEC.

IMEC's portfolio also contains **polymer-based electronics**, a promising technology for flexible, light and cheap microelectronic systems. While first applications already hit the market – displays based on organic light-emitting diodes (OLED) – future applications include advanced

In IMEC's 300mm cleanroom, solutions for the sub-45nm technology nodes are being investigated.

memories, smart clothing, radio-frequency identification (RFID) tags, chemical sensors, **solar cells** and biosensors. IMEC studies different applications of organic electronics, including transistors, diodes, memories, solar cells and biosensors. In the field of renewable energy sources, IMEC improves the technology for solar cells based on crystalline silicon and organic materials and also high-efficiency photovoltaic stacks for space applications. Moreover, adaptation of the electricity grid architecture and the implementation of energy storage devices are examined.

IEC's ultra modern research facility is continuously

IMEC has also set up a strategic research program 'efficient power' that focuses on developing **high-efficiency**/ **high-power systems**, beyond the silicon limits, enabled by GaN technology. The program addresses three application domains: RF power amplification, switching devices for power conversion and, to a lower extent, optoelectronics.

In the coming years, microsystems will have an increasing impact on our daily lives and wellbeing. Microsystems integrate multiple technology domains into small autonomous sensors with a variety of functions like detection, data processing and wireless communication. These miniaturized systems can create a network that communicates with the environment. Application domains include healthcare, industrial processing, food-quality control and the manufacturing of intelligent clothing. IMEC develops basic technologies for these **autonomous sensor networks** and therefore bundles its expertise in low-

### MEDIC University News

power data processing, wireless communication, interconnection and packaging, alternative energy sources and sensors. This research is conducted in the Holst Centre in Eindhoven, The Netherlands, established in 2005 as an initiative of IMEC and the Dutch research institute TNO. The Holst Centre has to develop into an internationally recognized research institute for the future generation of wireless autonomous transducer solutions and systems-on-foil.

In its M4 program, IMEC develops the necessary building blocks to create the future **multi-mode multimedia terminal**. This terminal will offer ubiquitous broadband multimedia access, served through broadband wireless communication. To realize this, several technological roadblocks have to be overcome, such as increased multimedia encoder/decoder complexity, seamless switching mode across different communication standards, increasing device cost and power consumption due to increased functionality and fast time-to-market.

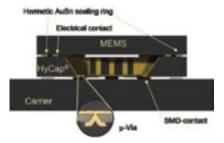

#### IMEC's Advanced Packaging and Interconnect Center (APIC)

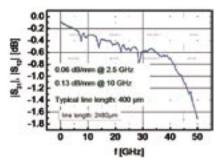

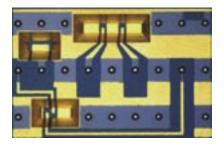

IMEC's strategic program on advanced packaging and interconnection technologies focuses on bridging the so-called 'interconnect gap' between circuit and system, heterogeneous integration of RF components and thermal management in high-density devices. The extreme miniaturization of transistors has a large impact on packaging and interconnection technologies. While the size of the chip is being reduced, the amount of input-output control pads does exactly the opposite. Assembly on for example printed circuit boards therefore becomes increasingly difficult. To solve this problem, IMEC develops a multilayer thin-film technology, which consists of multiple thin layers of metal and dielectric materials. The same technology can be used to protect vulnerable structures like MEMS in the early stages of packaging. When applied on active wafers, the technology is considered a wafer-level packaging (WLP) technology. Thin-film WLP technology can be used to realize on-chip flip-chip redistribution layers, for on-chip digital transmission lines, and for integration of high-quality RF passives. When thin-film technology is applied on an intermediate glass or high-resistivity Si substrate, it is considered a thin-film system-in-a-package (SiP) technology or MCM-D.

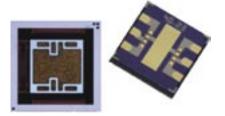

To make even smaller systems with increased functionality, IMEC has several activities on 3D-integration and (ultrathin) chip stacking. First of all, 3D-SiPs are developed which are complete sys-

tems-in-a-package stacked on top of each other. This approach ensures a high vield since each sub-SiP can be tested individually ensuring that only 'good' SiPs are used in the 3D stack. A second approach makes use of WLP techniques where 3D interconnects are created in a post-IC passivation process. A variant of this approach, called ultra-thin chip stacking (UTCS), uses thinned chips, which are embedded in thin-film interconnect layers. A third approach, called 3D-stacked IC (SIC), makes the connections between the different chips during IC processing. Within its strategic program, IMEC additionally focuses on the thermal characterization of packages and the development of advanced cooling systems.

#### Collaboration and Training Opportunities

Collaboration in Flanders, Europe and the rest of the world is of the uppermost importance for the success of the IC industry and the growth of the knowledge economy. This is why IMEC has set up a large network of partners (over

Wafer-to-wafer bonding tool.

3D-stacked chips assembled on a printed circuit test board using leadfree solder joints.

500), including IC manufacturers, equipment and material suppliers, universities, research institutes, etc. Through a unique collaboration model, based upon sharing of knowledge, talent, costs, risk and intellectual property, industrial researchers are integrated in IMEC's research teams. As a result, they gather their forces to tackle technological challenges the IC industry is facing. This strategy has become the only right one to survive in a world of technological challenges, million-dollar investments and fierce competition.

In the field of nano-electronics, managers, engineers and researchers must also be kept abreast of the latest technological developments. IMEC's microelectronics training center (MTC) therefore organizes courses and workshops for a variety of target groups. A broad scope of issues is addressed, ranging from IC process technology, chip- and system design to basic knowledge on IC technology, biology and multimedia. IMEC also supports teachers of Flemish schools and universities. Moreover, IMEC offers an international platform called 'Center for Advanced Learning in Information Technologies (CALIT)' where CEOs, policy makers and scientists can meet and exchange ideas.

IMEC is headquartered in Leuven, Belgium, and has representatives in the US, China and Japan. Its staff of more than 1450 people includes more than 500 industrial residents and guest researchers. In 2005, its revenue was EUR 197 million. For further information on IMEC visit www.imec.be or contact info@imec.be.

### **Common Ground. Common Goals. Uncommon Potential.**

Please join us at the industry's best technical conference on electronic assembly and advanced packaging.

September 24 - 28, 2006 In conjuction with Assembly Technology Expo Donald Stephens Convention Center Rosemont, Illinois

for information, call 952-920-7682 or visit www.smta.org

### Made Industry News

### K&S Relocates Corporate Headquarters

FORT WASHINGTON, PA – Kulicke & Soffa Industries has relocated its corporate headquarters to a new building in Fort Washington, Pennsylvania. The company will maintain its current telephone numbers and email addresses.

Please ensure that all of your business correspondence is directed to their new corporate address at Kulicke and Soffa Industries, Inc., 1005 Virginia Drive, Fort Washington, PA 19034

### SUSS and IMEC to Develop Measurement Tools for Latest Technologies

MUNICH, GERMANY-SUSS MicroTec AG has installed the latest 300 mm technology in wafer probe systems at the nanoelectronics research center IMEC in Leuven, Belgium. Both PA300PS ProbeShield® semiautomatic probe systems with ReAlign<sup>™</sup> and Contact-View<sup>™</sup> technology and PA300 probe systems for RF-noise and S-parameter measurements have been installed. An agreement has been made for further collaboration on enhancing 300 mm probe systems in the following years.

"We are very pleased to sign this agreement with IMEC, Europe's leading independent nanoelectronics research center," said Dr. Claus Dietrich, Managing Director of the Test Systems division at SUSS MicroTec. "This collaboration proves SUSS MicroTec is offering the latest technology for advanced wafer probing, like the unique ReAlign and ContactView solutions. Furthermore, it shows that we continue to set standards in excellent electrical performance, such as noise and leakage levels, with our cutting-edge hardware and software solutions."

In another development, SUSS MicroTec will deliver a second vacuum probe system to IMEC. The manual system will compliment the existing semiautomatic vacuum system, which is currently being used to test the reliability of MEMS devices at wafer level. These unique systems allow the user to place the device under test in ultra-high vacuum environments that simulate actual operating conditions. Therefore the device can be tested before the packaging process, which decreases feedback time for R&D and saves costs.

IMEC's technologies and devices are on the front line of technology development, and therefore new measurement challenges arise continuously. Close collaboration with SUSS MicroTec will ensure early feedback on possible future needs for wafer-level testing, and IMEC will explore solutions and future enhancements together with SUSS.

### Ultrasonic Coating Module Debuts at Semicon West

HAVERHILL, MA – Ultrasonic Systems, Inc. will introduce their new Ultrasonic Coating Module at the Semicon West Show, Booth 8007. This new modular system design is perfect for integration into robotic work cells or semiconductor integrated processing systems.

This Ultrasonic Coating Module features the CAT 35 ILDS (Integrated Liquid Delivery System) Coating Head, micro-valve control, and PLC controller for integration into work cell software. This coating head provides a superior alternative to conventional spin coating, dispensing and other coating technologies.

Ultrasonic Systems, Inc. manufactures the world's most advanced spray coating systems. Headquarters are located at 135 Ward Hill Ave, Haverhill, MA 01835 USA; Tel: (978) 521-0095; Fax: (978) 521-7023; e-mail: sales@ultraspray.com; web: www.ultraspray.com.

### Maxtek Earns ISO 14001:2004 Certification

BEAVERTON, OR – Maxtek Components Corporation, a Tektronix, Inc. company and a custom microelectronics assembly and test service provider, has announced that it has achieved ISO 14001:2004 certification. ISO is the International Organization for Standardization, and ISO 14001 is a globally accepted standard that pertains to creating and managing environmental management systems.

"We view the ISO 14001: 2004 certification as a key element of our company-wide quality initiative, which is designed to enable our customers' most advanced microelectronic technologies while minimizing their development risks," said Tom Buzak, President, Maxtek Components Corporation. "The ISO 14001:2004 certification sets Maxtek apart from many of its competitors and positions the company to better serve its customers striving to comply with environmental programs in their own industries and regions."

Maxtek, a Tektronix company, is a proven custom microelectronics company providing a complete range of design, assembly and test services to equipment manufacturers. With 35 years of experience serving the measurement, military and medical markets, Maxtek works as an extension of their customers' product teams to resolve the most demanding packaging challenges. Headquartered in Beaverton, Oregon, Maxtek can be found on the web at www. maxtek.com.

### AIT Expands Batam Factory

SINGAPORE – Advanced Interconnect Technologies (AIT) has announced that it is expanding its world-class assembly and test factory in Batam, Indonesia, to 400,000 square feet by September of this year – adding more than 30,000 square feet. This expansion will be developed on AIT's existing property in the Batamindo Industrial Park.

With the expansion of the Batam factory, AIT will be able to enlarge its floor space dedicated to final test which will allow them to meet the growing demand in the industry and from its existing customers for full turnkey assembly and test services. Faced with continued pressure to streamline time-tomarket and improve profit-ability, many semiconductor manufacturers are using outsourcing as a key business strategy. While outsourcing wafer production has become commonplace in the industry, now both test and assembly functions are also being outsourced by fabless manufacturers and integrated device manufacturers (IDMs) alike.

For more information about the company, its products and services please visit their website at www.aithome.com..

### Kyocera Creates Department of Continuous Improvement

SAN DIEGO, CA – Kyocera America, Inc. has announced the creation of a Department of Continuous Improvement. This department will consist of Kyocera America's trained and dedicated "Black Belt" Specialists in Lean Six Sigma tools.

"The Department of Continuous Improvement will help support our initiative of better serving our customers by facilitating improvement projects in production, sales and support areas throughout the company" said Bob Whisler, President of Kyocera America, Inc.

Lisa Hamel, formerly Engineering Manager in the Metallized Division, will lead the department as Manager of Continuous Improvement.

### Hymite Awarded ISO 9001 Certification

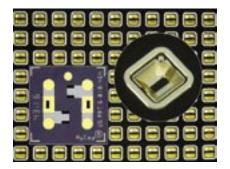

COPENHAGEN and BER-LIN – Hymite announces that it has been awarded the ISO 9001 certificate. Hymite develops, manufactures and markets innovative packaging solutions for semiconductor devices that allow better performance and optimized manufacturing.

"Our packaging technology is based on silicon - this enables us to increase the level of functional integration and to use highly automated manufacturing technologies developed by the semiconductor industry. The ISO 9000 certification is for us another step that demonstrates our dedication to obtain best-inclass quality and give the support to our customers to achieve their cost and performance goals", says Jochen Kuhmann, CTO and founder of Hymite. "Today we are engaged in several customer projects within high growth markets such as mobile phones, consumer applications and communications products. The certification process has helped us to tune our manufacturing and management processes so that we are ready to ramp up to volume production."

### March Plasma Systems Opens Direct Offices in Shanghai, China

CONCORD, CA – Building on over 20 years of continuous plasma technology innovation, March Plasma Systems has announced that it has established direct operations in Shanghai, China. The new March offices are located at 828 Xin Jin Qiao Road, Pudong, Shanghai 201206, China. The office telephone number is +86 -21-5854-2345, and the facsimile number is +86-21-5854-9150.

To manage March's China operations, March has appointed Mr. David Pang as Regional Sales Manager and named Mr. Michael Zhang as Applications Field Service Engineer. Other recent activities include the appointment of new distributors for the semiconductor and PCB markets, and the formation of strategic alliances with key ezquipment partners within the Chinese market.

The China facilities are equipped with an advanced Applications and Demonstration Laboratory containing a variety of March plasma processing systems for local customer training, demonstrations and applications support.

Contact March Plasma Systems directly or see the March web site for more details: www. marchplasma.com.

### Nagase Acquires 60% Share of Pac Tech GmbH

NAUEN, GERMANY – Pac Tech GmbH has announced that Nagase and Co., a major trading company in Japan, has acquired a 60% share of Pac Tech GmbH, for an undisclosed amount. The acquisition was completed on February 10, 2006.

Pac Tech GmbH focuses on bumping and packaging based on advanced electroless metallization. It also provides advanced laser bonding and bumping equipment worldwide. Pac Tech GmbH doubled its sales worldwide in 2005 to roughly 14 million Euros.

Nagase began selling Pac Tech GmbH equipment and technology licenses in Japan in 2000. According to Nagase Director Executive Officer Mr. Kazuo Nagashima, "Through the addition of Pac Tech's technology and its market penetra-

### Excellite EXP Wafer Plating Tool

### FEATURES

- Automatic or Manual Operations

- > 50-300 мм Wafer Capability

- Underbump Metalization Applications

- MEMS

- OEMS

- MOEMS

- CMOS

2221 NIAGARA FALLS BLVD NIAGARA FALLS, NEW YORK 14304

phone 800.707.3433 | fax 716.731.1591 www.precisionprocess.com | www.platingsystems.com

### MELTE Industry News

tion in Japan and China, we intend to double our overall sales of back-end equipment and materials over the next three years from approximately 6 billion JPY in 2005."

Pac Tech GmbH equipment offers semiconductor manufacturers several distinct advantages over other conventional methods. There is virtually no damage to substrates using their patented contactless method of applying solder-balls to fine and thin materials such as those used in hard disk drive head applications. The electroless wafer bumping method has a strong advantage in achieving short lead-time and low-cost compared to existing electroplating methods. As semiconductor geometries become smaller and smaller, the need for very fine-pitch solder-ball placement and wafer level packaging will become even more critical.

Visit the Pac Tech website at www.pactech.de.

### STATS ChipPAC **Expands QFN** Portfolio for Wireless Applications

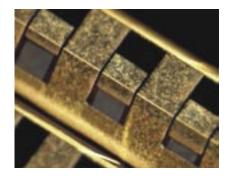

U.S. & SINGAPORE - STATS ChipPAC Ltd. has announced that it has expanded its Quad Flat No-lead (QFN) packaging portfolio with technology advancements in both single mold cavity format and molded array format for applications requiring a higher number of input/output (I/O) terminal pads and lower package profile and weight.

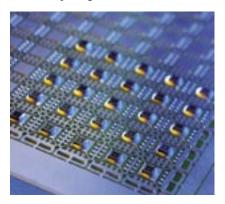

QFN is a leadframe based, plastic encapsulated, chip scale package in either single mold cavity format (punch singulated) or molded array format (saw singulated). An exposed die pad combined with extremely low RLC (resistance, inductance, and capacitance) provides excellent electrical and thermal performance enhancement which

is ideal for high frequency and high power applications, particularly wireless and handheld portable applications such as mobile phones. STATS Chip-PAC offers multiple configurations in each of these package types.

The saw singulated version, or OFNs, is a leadframe based molded package in land grid array format with square or rectangular body sizes. The QFNs is available in 0.40mm, 0.50mm, 0.65mm and 0.80mm lead pitch, with standard package profile heights of nominal 0.75mm or 0.90mm. STATS ChipPAC now offers an extremely thin version of the QFNs, called XQFNs, which features a nominal package height of 0.45mm. Advanced molding technology, wafer thinning technology, and ultra low loop wire bonding are key to achieving the extremely low profile height of the XQFNs.

For customers who require devices with higher I/O terminal pads in a smaller footprint,

the dual row punch singulated (QFNp) package design, called VQFNp-dr, can accommodate greater than 50% more terminals than a single row OFN pad design in the same body size. The VQFNp-dr features two rows of staggered I/O terminal pads in a 0.50mm lead pitch with an exposed die pad for die grounding and improved thermal performance. With its higher number of terminals pads and small profile, VQFNp-dr also enables higher functional integration in a package by means of die stacking. VOFNpdr is available in body sizes up to 12mm x 12mm with up to 156 pins.

QFN packages are available in various body sizes and thicknesses, offered in standard and green/lead-free bill of materials, and can be processed by conventional SMT equipment, benefiting surface mount operations downstream.

Further information is available at www.statschippac.com.

(408) 245-5330

1217 WILDWOOD AVENUE • SUNNYVALE • CA 94089

### Gartner's Final Semiconductor Market Share Results Show Industry Grew 5.7 Percent in 2005

STAMFORD, CT – Worldwide semiconductor revenue totaled \$235 billion in 2005, a 5.7 percent increase from 2004, according to final results by Gartner, Inc. 2005 revenue surpassed the semiconductor industry's previous record of \$223 billion set in 2000.

"Personal computers and cellular telephones remain the largest drivers for semiconductor business," said Richard Gordon, research vice president at Gartner. "The popularity of MP3 players, however, accounted for dramatic growth among flash memory vendors in 2005."

High PC demand helped Intel retain its position as the No. 1 semiconductor supplier in 2005. Intel's revenue grew 12.6 percent, twice the market average. Commodity memory demand bolstered the fortunes of Samsung Electronics, who now dominates most areas of the memory market, and Hynix Semiconductor, who moved into the top 10 for the first time in 2005.

Samsung held the No. 1 position in DRAM, SRAM and the fast-growing NAND flash market in 2005. Hynix's NAND flash revenue reached \$1.5 billion, up from \$212 million in 2004, an increase of more than 600 percent. Over all, this company grew 23 percent – the fastest growth among the top 10 semiconductor suppliers.

The entire NAND flash memory segment grew 71 percent between 2004 and 2005. Other fast growth markets included CMOS image sensors (28 percent), and consumer ASICs (14 percent). The wireless ASIC segment, where Texas Instruments was the market leader, grew 9 percent last year.

The regional trend of sales moving towards Asia/Pacific continued in 2005. The Asia/ Pacific region, which includes China, Taiwan, Korea and Singapore, accounted for 44.5 percent of worldwide semiconductor revenue, and the region experienced the strongest growth in 2005 – 11 percent. The Europe, Middle East and Africa (EMEA) region saw the next strongest revenue growth with 4 percent. The Americas had 1 percent growth in 2005 and Japan was flat with revenue increasing 0.2 percent.

Additional information on specific market segments and devices is available in the Gartner report "Market Share: Semiconductor Revenue, Worldwide, 2005." This report provides rankings among vendors of microprocessors and memory, DSPs, ASICs, Application-Specific Standard Products (ASSPs), analog ICs, discretes and many other semiconductor products. The revenues of top suppliers are identified in specific markets such as automotive. consumer products, wireless and wired communication, computers, com-puter peripherals and industrial controls. Regional market share results are also available for the Americas, EMEA, Asia/Pacific and Japan. The report is available on Gartner's web site at www.gartner. com/DisplayDocument?doc cd=120719.

### Semicon West 2006 TechXPOT Offers Special Focus on Test, Assembly and Packaging Technologies

SAN JOSE, CA – SEMI has announced additional details for its upcoming Test, Assembly and Packaging TechXPOT, located in West Hall Level 2 of the Moscone Center during SEMICON West 2006, July 11-13 in San Francisco. Building on the "show-within-a-show" concept, the Test, Assembly and Packaging TechXPOT is a special area focusing on innovations in test, assembly and packaging, with exhibits, dis-

### Low-Cost Wafer Bumping Services in Silicon Valley

- Quick-turn and mass-production

Highly competitive, low-cost bumping technology

Exceptional quality through

- high-level expertise

#### **Available Processes**