Volume 12, Number 2

F P T

report

MERITAL TUILING ON Services

A Publication of The MicroElectronics Packaging & Test Engineering Council

**INDUSTRY NEWS**

**Amkor Technology, Inc.** has announced that Ken Joyce has been appointed President of the company. Gil Tily has been named Chief Administrative Officer and Executive Vice President, succeeding Mr. Joyce in that role. Eric Larson will join the company as Executive Vice President Product Management Group. *page 12*

**Sonoscan** has introduced a new capability for its line of C - SAM acoustic microscopes that reveals the external surface topography of a device at the same time as its internal features, known as the Acoustic Surface Profile (ASP) module. *page 14*

#### The 3rd Annual MEPTEC **Description Description Description**

One Day Technical Symposium at Arizona State University Coming to Tempe, AZ September 25th ... page 4

#### **MEMBER COMPANY PROFILE**

**CAD Design Software** announces the results of a major LTCC design test conducted by a leading U.S. defense foundry. The result is a dramatic reduction in overall design time. *page 17*

**March Plasma Systems** has announced that it has released the PM-100 plasma system, which is designed to be a low-cost, highly effective plasma treatment solution for treating electronic components, printed circuit boards, and medical & life science devices. *page 19*

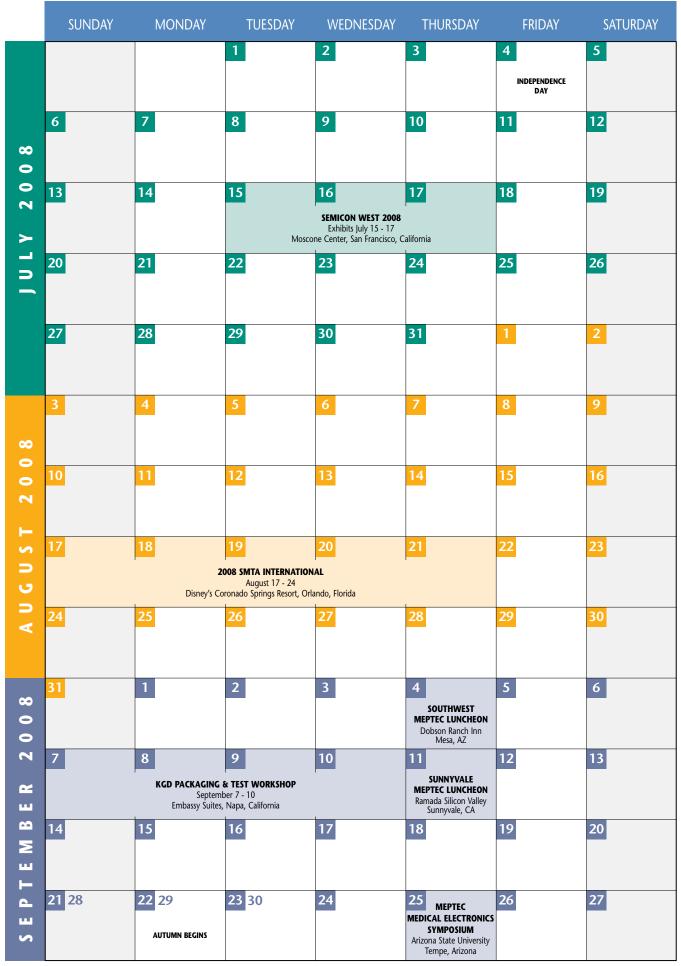

**SEMICON West returns to Moscone Center in San Francisco July 15 through 17.** page 23

www.meptec.org

**Rudolph Technologies** has an established, long-term presence in the wafer processing fab as well as the packaging and test floor. The company maintains a leadership position by investing in aggressive research and product development to meet customer demand for performance and productivity. In addition, Rudolph's involvement in research programs and application initiatives with customers, industry consortia and other equipment suppliers is aimed at addressing critical challenges in microelectronics manufacturing. *page 10*  udolph Technologies has developed a line of fullyautomated systems for thin film process control that are used in major fabs around the world. Opaque films are measured with the patented Picosecond Ultrasonic Laser Sonar (PULSE<sup>®</sup>) technology, simultaneously measuring thickness and other properties.

Semiconductor equipment bookings decrease 5% over April 2008 level. *page 18*

# innovation

Finding new ways to solve problems—whether it's new obstacles that arise or the usual process challenges—we're here to offer a unique combination of strengths.

Recent example: our award-winning printable phase change material. Honeywell's ongoing research and development in chemistry, metallurgy, and the processes that bring them together—from our new packaging

R&D facility in Spokane, Washington, to our technology center in Shanghai, China—ensure that wherever challenges arise, we'll continue to create solutions that solve them. And as a partner to most of the top semiconductor houses worldwide, our technology portfolio is consistently at the forefront of invention, empowering the global leaders of innovation. Honeywell Electronic Materials—helping the manufacturers of today navigate the future.

## Honeywell

Contact Honeywell for solutions to your puzzle... visit www.honeywell.com/sm/em or call 1-408-962-2000.

Dear MEPTEC Members and Supporters,

We're pleased to announce that 2008 marks the 30th year that MEPTEC has served the semiconductor packaging and test engineering industry! Since our inception in 1978 we have continued to be committed exclusively to packaging, assembly and test, and are dedicated to the advancement of our industry. Over the years MEPTEC has provided a forum for semiconductor professionals to learn and exchange ideas that relate to packaging, assembly, test and handling.

We'd like to inform you of several exciting new products and services for 2008:

- A brand new, totally redesigned website now online.

- New affordable advertising and promotion opportunities

- Web banners

- A totally new print publication: the TECH Report

- Member company "spotlights" on the MEPTEC homepage (limited number each month)

- "Education Network Series" seminars and workshops

- MEPTEC Report Newsletter archives online from 2004 to present

- · New Symposium CD pricing and packages

- And coming soon... MEPTEC Creative Services

- Company newsletter design and production

- Website design and maintenance

- Event/meeting planning

Please see our special pull-out section in this issue for a more detailed description of these services. Further information on these items is also now available at www.meptec.org.

We look forward to an exciting new year, and thank you for your continued support!

Regards,

Bette Cooper President, MEPTEC Editor, The MEPTEC Report

MicroElectronics Packaging and Test Engineering Council

### A SPECIAL ONE-DAY TECHNICAL SYMPOSIUM

### September 25, 2008 • Arizona State University • Tempe Campus, Tempe, AZ

## The 3rd Annual MEPTEC

# Medical Electronics Symposium

# **Technology Concepts Enabling Product Reality**

### Sessions will include:

- Revolutionary Concepts in Medical Electronics

- Advanced Materials for Medical Electronics

- Key Enabling Technologies

- Next Generation of Bio-Medical Sensors and Electronics

#### CORPORATE SPONSORS

**CONNECTION ONE**

Fulton School of Engineering

TEXAS Instruments

#### **ASSOCIATION SPONSORS**

Arizona Biolndustry Association®

SINTA Surface Mount Technology Association

### REGISTER ONLINE TODAY AT WWW.MEPTEC.ORG

MEDIA SPONSORS

Advanced Packaging

GY COUNCIL

semiconductor packaging news

Volume 12, Number 2 A Publication of The MicroElectronics Packaging & Test Engineering Council

P. O. Box 222 Medicine Park, OK 73557 Tel: (650) 714-1570 Email: info@meptec.org

#### Published By MEPCOM

Editor Bette Cooper

Design and Production Gary Brown

Sales and Marketing Kim Barber

#### **MEPTEC Advisory Board**

Seth Alavi SunSil

Jeffrey Braden

Philippe Briot P. Briot & Associates

Joel Camarda Exar Corporation

Gary Catlin Plexus

**Tom Clifford**

Rob Cole

John Crane J. H. Crane & Associates

Jeffrey C. Demmin Tessera

> Bruce Euzent Altera Corporation

> > Skip Fehr

Julia Goldstein Advanced Packaging Magazine

> Anna Gualtieri Elle Technology

Bance Hom Consultech International, Inc

Ron Jones N-Able Group International

Nick Leonardi Premier Semiconductor Services

> Phil Marcoux TPL Group

Bhavesh Muni Henkel Corporation

Mary Olsson Gary Smith EDA

Marc Papageorge Semiconductor Outsourcing Solutions

> Rich Rice ASE (US) Inc.

Jim Walker Gartner Dataquest

Russ Winslow Six Sigma

MEPTEC Report Vol. 12, No. 2. Published quarterly by MEPCOM, P. O. Box 222, Medicine Park, OK 73557. Copyright 2008 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico. and \$95US elsewhere.

For advertising rates and information contact John Waller at 215-646-7838, Fax 215-646-0504.

## **Council Update**

t's that time again: summertime, which in our industry means Semicon West. As every year, thousands will descend on San Francisco. This issue is being distributed there, so if you've picked one up and are reading this, thank you!

MEPTEC's next symposium will be on Thursday, September 25, and once again we'll be holding our annual Medical Electronics event on the Tempe campus of Arizona State University in the beautiful Old Main building MEPTEC's 3rd Annual Medical Electronics Symposium: Technology Concepts Enabling Product Reality will be co-sponsored by ASU and Connection One and the Ira A. Fulton School of Engineering. Driven by strong global demand from health conscious consumers in receiving the best medical diagnosis and treatment available, this symposium will focus on advanced technologies in medical electronic products. Industry experts will present on the revolutionary concepts and enabling technologies driving future product trends. Registration is open on the web; please go to www.meptec.org for more details and to register.

In this issue we offer a follow up of our most recent symposium from Julia Goldstein, contributing editor for Advanced Packaging Magazine, on the "6th Annual MEPTEC MEMS Symposium – MEMS Market Evolution: From Technology Push to Market Pull". Julia points out that with MEPTEC's first MEMS symposium in 2003, MEMS was "a technology with potential". Five years later it's obvious the potential has been realized. We'd like to thank Julia for this summary (see page 8).

Our first feature article is contributed by **Giles Humpston** of **Tessera**, one of our long time Corporate members. Titled *"Wafer Level Cavity Package Using Via-through Pad Interconnections"*, this article discusses the solution which is being progressively adopted by the industry, which is to package the semiconductor die using wafer-level technology. He covers wafer-level package interconnects, electrophoretic materials and reliability issues. See page 20 for this interesting and thorough article.

Our second feature article is written by **Kelly McKendrick** of **ASAT**, another long time MEPTEC Corporate member. Written in first person, he talks to us about "*Thin*" *QFN*, *TAPP and fpBGA Packages*". He takes us through his journey starting in 1980 as a "Fab Rat" working on 3" wafers and thinking 4" wafers were huge. He asks, what is the ultimate "thin" package? He also poses an interesting scenario: "Just when you think you have the final "Green" package and process, someone finds yet another substance that makes the green not so green anymore!". Read this insightful and informative piece on page 24.

Our editorial this issue is from Gary Alexander, Executive Director of the Surplus Equipment Consortium/Network, Inc., or SEC/N. His editorial on page 34 is titled "Evolving The Global Secondary Market". Advisory board member John Crane introduced us to this group, and he found they had some interesting things to share. SEC/N was founded based on the efforts and concerns of the SEMATECH Surplus Equipment Council (SSEC). As Gary says (quoting Bob Dylan), "The times they are a-changing" – especially when it comes to the global secondary market.

MEPTEC Advisory Board member Mary Olsson of Gary Smith EDA asks the question: "Is 2008 the Year for Analog Mixed-Signal?" in her Industry Analysis on page 6. She reviews the Analog/Mixed-Signal EDA Landscape, sales revenues, first quarter earnings and sequential quarterly earnings of Analog/Mixed Signal companies, and discusses supply side issues as well. We'd like to thank Mary for her contribution to this issue.

Our Member Company Profile this issue is Corporate MEPTEC Member **Rudolph Technologies**. Rudolph has a long history, starting in 1940 as an importer of microscopes and scientific instruments. In 1996 they expanded into metrology technologies, and was renamed Rudolph Technologies, Inc. During the years of 2002-2007 several acquisitions contributed to their growth, and they have evolved into a process characterization leader in the semiconductor industry. See their profile outlining their interesting history and many services on page 10.

We'd like to thank all of our contributors for making this another great issue. If your reading this publication for the first time at the Semicon West show, or another of the many events where we distribute the MEPTEC Report, we hope you enjoy it.

Thanks for joining us!

#### Special Thanks to Kim Barber

School's out, Summer's here, and people are on the move... including our own Kim Barber. Kim is taking advantage of the Summer Break to relocate her family of three, along with husband Brian, to sunny Southern California

from the San Francisco Bay Area.

We'd like to take this opportunity to thank Kim for her hard work over the last four years as MEPTEC Director of Sales and Marketing. Her efforts have helped MEPTEC experience growth in both our events and the MEPTEC Report.

While Kim is "on the move" feel free to contact Gary Brown at gbrown@meptec.org for any of your sales and marketing needs.

# MEDIC Industry Analysis

# Is 2008 the Year for Analog Mixed-Signal?

Mary A. Olsson Gary Smith EDA

ince the first of this year, Gary Smith EDA has been interviewing and surveying companies in the Analog/ Mixed-Signal EDA landscape to uncover answers to the question "Is 2008 going to be the year where analog design automation moves forward and catches up with digital design automation?"

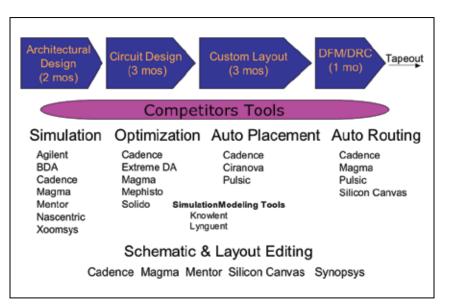

According to the majority of Analog/Mixed-Signal Design Tool startups, the market for custom IC design solutions, which includes analog/mixed signal designs, could reach \$700 million in 2008. The Gary Smith EDA forecast for Custom Analog/Mixed-Signal ICs is \$427 million in 2008. The majority of this growth is being driven by the wireless and consumer market applications. Thus a huge opportunity exists for 100 percent automation in analog/mixed-signal, if the layout tools existed. According to the majority of all interviewed and surveyed, the process is still predominately manual, and most of the older tools are insufficient for designs below 90nm. No one has yet to make an automated custom layout tool acceptable to analog/mixedsignal device designers. The industry is lagging as it deals with "your grandfather's analog design process".

Except for the majority of EDA start-ups, many listed in Figure 1; most of the tools being used in the analog/ mixed-signal design flow today are pre-1998 generation. Analog/Mixed-Signal design flows now range from 9 months to as long as 18 months, especially for high-end design applications. Users like Texas Instruments, STMicroelectronics, Qualcomm and Broad-com are shifting mixed-signal designs (also called ASPs and ASSPs) to 65nm and 45nm processes in 2008 and 2009. If they could automate layout, physical design would be measured in days and

Figure 1. Analog/Mixed-Signal EDA Landscape. Source: Ciranova & GSEDA May 2008

|          |        |                           | _        | Sales    | Sales    | Sales    | Sale    |

|----------|--------|---------------------------|----------|----------|----------|----------|---------|

|          | Stock  | -                         | Revenue  | Revenue  | Revenue  | Revenue  | Revenue |

| Exchange | Symbol |                           |          | Q1/2007  | _        | -        | _       |

| NYSE     | ADI    | Analog Devices            | \$2,521  | \$591    | \$669    | \$637    | \$62    |

| -        | -      | Avago Technologies        | \$1,535  | \$375    | \$386    | \$381    | \$39    |

| NASDAQ   | BRCM   | Broadcom                  | \$3,776  | \$901    | \$898    | \$950    | \$1,02  |

| NASDAQ   | DIOD   | Diodes Inc.               | \$401    | \$92     | \$96     | \$105    | \$10    |

| NASDAQ   | EXAR   | Exar                      | \$69     | \$16     | \$17     | \$15     | \$2     |

| NYSE     | FCS    | Fairchild                 | \$1,670  | \$403    | \$409    | \$427    | \$43    |

| -        | FSL    | Freescale                 | \$5,722  | \$1,361  | \$1,376  | \$1,446  | \$1,53  |

| FSE/NYSE | IFX    | Infineon                  | \$6,478  | \$1,506  | \$1,557  | \$1,736  | \$1,67  |

| NASDAQ   | ISIL   | Intersil                  | \$757    | \$168    | \$178    | \$198    | \$21    |

| NASDAQ   | LLTC   | Linear Technology         | \$1,093  | \$255    | \$268    | \$281    | \$28    |

| NASDAQ   | MRVL   | Marvell                   | \$2,672  | \$622    | \$635    | \$657    | \$75    |

| NASDAQ   | MXIM   | Maxim Integrated Circuits | \$2,070  | \$476    | \$531    | \$523    | \$54    |

| TSE**    | 2454   | MediaTek Inc.             | \$2,626  | \$491    | \$601    | \$871    | \$66    |

| NASDAQ   | MCRL   | Micrel                    | \$258    | \$63     | \$65     | \$65     | \$6     |

| NASDAQ   | мснр   | Microchip                 | \$1,033  | \$258    | \$264    | \$259    | \$25    |

| NASDAQ   | MSCC   | Microsemi Corporation     | \$463    | \$107    | \$114    | \$120    | \$12    |

| NYSE     | NSM    | National Semiconductor    | \$1,857  | \$431    | \$456    | \$472    | \$49    |

| -        | -      | NXP                       | \$7,659  | \$2,249  | \$1,757  | \$1,864  | \$1,78  |

| NASDAQ   | ONNN   | ON Semiconductor          | \$1,493  | \$348    | \$356    | \$381    | \$40    |

| NASDAQ   | PSEM   | Pericom Semiconductor     | \$141    | \$30     | \$32     | \$38     | \$4     |

| NASDAQ   | PMCS   | PMC-Sierra                | \$449    | \$104    | \$105    | \$117    | \$12    |

| NASDAQ   | QCOM   | Qualcomm                  | \$9,292  | \$2,221  | \$2,325  | \$2,306  | \$2,44  |

| NASDAQ   | RFMD   | RF Micro Devices          | \$993    | \$257    | \$212    | \$256    | \$26    |

| NYSE     | STM    | STMicroelectronics        | \$10,001 | \$2,276  | \$2,418  | \$2,565  | \$2,74  |

| NYSE     | TXN    | Texas Instruments         | \$13,834 | \$3,191  | \$3,424  | \$3,663  | \$3,55  |

| NYSE     | VSH    | Vishay/Siliconix          | \$2,833  | \$658    | \$716    | \$730    | \$73    |

|          |        | Total                     | \$81,698 | \$19,449 | \$19,864 | \$21,063 | \$21,32 |

\* Denotes US Dollars from Euros, \*\* Denotes Taiwan Stock Exchange

Table 1. Sales Revenue of Analog/Mixed-Signal Semiconductor Companies, 2007

(Millions of Dollars)

Source: GSEDA May 2008

not weeks or months.

The value to these companies and their designers would include:

- Faster delivery time to market

- Better opportunity for increased revenue from IP re-use and process node migration

- Better quality of result (QoR) at process technology below 65nm

#### **Supply Side Issues**

In 1998 worldwide analog revenue was \$9 billion. Standard analog product revenue was \$7 billion and mixed-signal was \$2 billion. 115 analog device suppliers served the entire 1998 analog market. By year-end 2007 the entire analog market reached almost \$37 billion in revenue for device suppliers, according to WSTS 2008 statistical reports. The standard products arena that includes interface, data converters operational amplifiers and other analog, reached almost \$15 billion in revenue. The application specific products (ASPs) designed into computer, communications, consumer, automotive, industrial and military sectors rose to \$22 billion in revenue.

Table 1 lists the corporate sales revenue performance of companies that provide quarterly data and/or are publicly traded in the United States. These are the largest suppliers to the worldwide analog/mixed-signal merchant market. The top five companies, Texas Instruments, STMicroelectronics, Qualcomm, NXP, and Broadcom, are the largest suppliers to the mixedsignal or application specific analog markets, having captured the greatest share of designs into the wireless communications and consumer sectors.

Table 2 provides detailed information for these same companies for first quarter 2008 over first quarter 2007. Overall revenue growth in first quarter 2008 was up 9.1 percent over first quarter 2007. Net income was up 53.4 percent. This is viewed as a positive factor as many have expressed that unsettling market news, lower customer bookings and a persistent downward pressure on device average selling prices, were signs pointing to a downward slide in revenue in the first half of 2008. In Table 3 the first quarter of 2008 showed a slight decline (0.5) percent in overall growth versus the fourth quarter 2007 sales revenues. However, net income for the stronger competitors on both the standard analog and application specific analog products areas carried net income to an increase of 53.5 percent. It is important to note that although earnings are down considerably for many in the analog segment, some analog companies are making money. Historically, the analog market players are aware of cycles in the industry, and a downward market presents plenty of opportunity to cut back on production, absorb costs and reinvest in R&D.

#### Summary

What has been evident during this research process is that there is a definite shift (vendors and users) away

from single vendor in-house proprietary solutions to design tool integration via partnering, alliances and mergers. Users are seeing this as a tremendous opportunity to build relationships with new EDA tool suppliers, accelerate growth in application specific analog and expand positions with existing and new OEM customers. In the face of increasing circuit complexity and high performance SOC designs, many EDA start-ups and a few steadfast major leaders are ready to announce key automated layout tools to drive the market forward. The DAC 2008 event in June may be a turning point for both vendors and users in the analog/mixed-signal space.

| _        | Stock      |                           | Sales<br>Revenue | Sales<br>Revenue | Change | Net<br>Income | Net<br>Income | Change  |

|----------|------------|---------------------------|------------------|------------------|--------|---------------|---------------|---------|

| Exchange | Symbol     | Company                   | Q1/2007          | Q1/2008          | (%)    | Q1/2007       | Q1/2008       | (%)     |

| NYSE     | ADI        | Analog Devices            | 591.3            |                  |        |               | 370.7         | 141.99  |

| -        | -          | Avago Technologies        | 375.0            |                  |        |               | 4.0           | -33.31  |

| NASDAQ   | BRCM       | Broadcom                  | 901.5            |                  |        |               | 74.3          | 21.81   |

| NASDAQ   | DIOD       | Diodes Inc.               | 92.0             |                  |        |               | 14.2          | 9.29    |

| NASDAQ   | EXAR       | Exar                      | 16.9             |                  |        |               |               |         |

| NYSE     | FCS        | Fairchild                 | 402.6            |                  |        |               | 17.1          | 171.49  |

| -        | <b>FSL</b> | Freescale                 | 1,361.0          |                  |        | (\$39.0)      | (245.0)       |         |

| FSE/NYSE | IFX        | Infineon*                 | 1,506.4          |                  |        |               |               |         |

| NASDAQ   | ISIL       | Intersil                  | 167.7            | 203.7            | 21.5%  | 33.1          | 67.1          | 102.79  |

| NASDAQ   | LLTC       | Linear Technology         | 255.0            |                  | 16.8%  | 98.6          | 99.2          | 0.71    |

| NASDAQ   | MRVL       | Marvell                   | 622.0            | 844.7            | 35.8%  | (140.6)       | 1.3           | -100.95 |

| NASDAQ   | MXIM       | Maxim Integrated Circuits | 475.8            | 487.4            | 2.4%   | 250.7         | 269.3         | 7.45    |

| TSE**    | 2454       | MediaTek Inc.**           | 490.5            | 636.5            | 29.8%  | 257.4         | 132.4         | -48.61  |

| NASDAQ   | MCRL       | Micrel                    | 63.1             | 66.1             | 4.7%   | 17.9          | 8.4           | -53.19  |

| NASDAQ   | MCHP       | Microchip                 | 258.2            | 260.4            | 0.9%   | 127.7         | 76.7          | -40.01  |

| NASDAQ   | MSCC       | Microsemi Corporation     | 106.7            | 126.7            | 18.7%  | (19.6)        | 9.8           | -150.19 |

| NYSE     | NSM        | National Semiconductor    | 431.0            | 453.4            | 5.2%   | 73.7          | 71.2          | -3.49   |

| -        | -          | NXP*                      | 2,249.0          | 2,338.0          | 4.0%   | (535.8)       | (120.1)       | -77.61  |

| NASDAQ   | ONNN       | ON Semiconductor          | 347.8            | 421.9            | 21.3%  | 54.0          | 20.8          | -61.59  |

| NASDAQ   | PSEM       | Pericom Semiconductor     | 30.2             | 41.2             | 36.4%  | 2.6           | 4.1           | 58.41   |

| NASDAQ   | PMCS       | PMC-Sierra                | 103.7            | 125.0            | 20.6%  | (15.8)        | (42.2)        | 166.79  |

| NASDAQ   | QCOM       | Qualcomm                  | 2,221.0          | 2,606.0          | 17.3%  | 726.0         | 766.0         | 5.51    |

| NASDAQ   | RFMD       | RF Nicro Devices          | 257.3            | 221.9            | -13.7% | 30.1          | (16.5)        | -154.65 |

| NYSE     | STM        | STMicroelectronics        | 2,276.0          | 2,478.0          | 8.9%   | 74.0          | (84.0)        | -213.51 |

| NYSE     | TXN        | Texas Instruments         | 3,191.0          | 3,272.0          | 2.5%   | 516.0         | 662.0         | 28.31   |

| NYSE     | VSH        | Vishay/Siliconix          | 658.2            | 733.3            | 11.4%  | \$0.0         | (24.6)        | -149.29 |

|          |            | Total                     | 19,450.7         | 21,212.4         | 9.1%   | 1,277.2       | 1,959.7       | 53.44   |

\* Denotes US Dollars from Euros, \*\* Denotes Taiwan Stock Exchange

Table 2. First Quarter Earnings, Analog/Mixed-Signal Semiconductor Companies,

2007/2008

Source: GSEDA May 2008

|             |        |                           | Sales    | Sales    |        | Net     | Net     |         |

|-------------|--------|---------------------------|----------|----------|--------|---------|---------|---------|

|             | Stock  |                           | Revenue  | Revenue  | Change | Income  | Income  | Change  |

| Exchange    | Symbol | Company                   | Q4/2007  | Q1/2008  | (%)    | Q4/2007 | Q1/2008 | (%)     |

| VYSE        | ADI    | Analog Devices            | 623.5    |          | -1.5%  | 97.9    | 370.7   | 278.7   |

| -           | -      | Avago Technologies        | 391.0    |          | 2.8%   | (2.0)   | 4.0     | -300.0  |

| VASDAQ      | BRCM   | Broadcom                  | 1,027.0  |          | 0.5%   | 90.3    | 74.3    | -17.7   |

| VASDAQ      | DIOD   | Diodes Inc.               | 107.6    |          | -11.2% |         | 14.2    | -22.4   |

| VASDAQ      | EXAR   | Exar                      | 20.7     | 18.4     | -11.3% | (11.7)  | (174.5) | 1394.1  |

| YSE         | FCS    | Fairchild                 | 431.9    | 406.3    | -5.9%  | 34.0    | 17.1    | -49.7   |

| -           | FSL    | Freescale                 | 1,539.0  |          | -8.7%  | (525.0) | (245.0) | -53.3   |

| SE/NYSE     | IFX    | Infineon*                 | 1,678.9  | 1,625.0  | -3.2%  | (609.0) | (2.1)   | -99.7   |

| VASDAQ      | ISIL   | Intersil                  | 212.6    |          | -4.2%  | 40.3    | 67.1    | 66.5    |

| VASDAQ      | LLTC   | Linear Technology         | 288.7    | 297.9    | 3.2%   | 93.8    | 99.2    | 5.8     |

| VASDAQ      | MRVL   | Marvell                   | 758.2    | 844.7    | 11.4%  | (140.6) | 1.3     | -100.9  |

| VASDAQ      | MXIM   | Maxim Integrated Circuits | 540.0    | 487.4    | -9.7%  | 285.3   | 269.3   | -5.6    |

| SE**        | 2454   | MediaTek Inc.**           | 664.1    | 636.5    | -4.2%  | 134.0   | 132.4   | -1.2    |

| VASDAQ      | MCRL   | Micrel                    | 64.6     | 66.1     | 2.3%   | 8.4     | 8.4     | -0.4    |

| VASDAQ      | MCHP   | Microchip                 | 252.6    | 260.4    | 3.1%   | 80.1    | 76.7    | -4.3    |

| VASDAQ      | MSCC   | Microsemi Corporation     | 123.5    | 126.7    | 2.6%   | 8.6     | 9.8     | 14.0    |

| WYSE .      | NSM    | National Semiconductor    | 499.0    | 453.4    | -9.1%  | 90.6    | 71.2    | -21.4   |

| -           | -      | NXP                       | 1,789.0  | 2,338.0  | 30.7%  | 3.1     | (120.0) | -3971.0 |

| VASDAQ      | ONNN   | ON Semiconductor          | 407.9    | 421.9    | 3.4%   | 61.1    | 20.8    | -66.0   |

| VASDAQ      | PSEM   | Pericom Semiconductor     | 40.7     | 41.2     | 1.1%   | 4.4     | 4.1     | -5.8    |

| VASDAQ      | PMCS   | PMC-Sierra                | 123.6    | 125.0    | 1.2%   | (5.1)   | (22.7)  | 345.9   |

| VASDAQ      | QCOM   | Qualcomm                  | 2,440.0  | 2,606.0  | 6.8%   | 767.0   | 766.0   | -0.1    |

| VASDAQ      | RFMD   | RF Micro Devices          | 268.2    | 221.9    | -17.2% | (15.1)  | (16.5)  | 9.1     |

| VYSE        | STM    | STMicroelectronics        | 2,742.0  | 2,478.0  | -9.6%  | 20.0    | (84.0)  | -520.0  |

| VYSE        | TXN    | Texas Instruments         | 3,556.0  | 3,272.0  | -8.0%  | 756.0   | 662.0   | -12.4   |

| <b>VYSE</b> | VSH    | Vishay/Siliconix          | 729.6    | 733.3    | 0.5%   | 4.9     | (24.6)  | -603.6  |

|             |        | Total                     | 21,320.0 | 21,212,4 | -0.5%  | 1,289.6 | 1,979.3 | 53.5    |

\* Denotes US Dollars from Euros, \*\* Denotes Taiwan Stock Exchange

Table 3. Sequential Quarterly Earnings, Analog/Mixed-Signal Semiconductor Companies, 04/2007 and 01/2008 *Source: GSEDA May 2008*

# Maine Event Follow-up

### 6th Annual MEPTEC MEMS Symposium MEMS Market Evolution – From Technology Push to Market Pull

Julia Goldstein MEPTEC Advisory Board Member Contributing Editor, Advanced Packaging Magazine

hen Advanced Packaging Magazine covered MEPTEC's first MEMS Symposium in May 2003, MEMS was a technology "with potential" that needed to move from a technology-driven to a market-driven approach to succeed commercially. This year's Symposium on May 22 was subtitled "MEMS Market Evolution – From Technology Push to Market Pull," suggesting that the potential has been realized. Sessions were focused on market segments (consumer, automotive and biomedicine) rather than technologies.

Yole Developpment's MEMS market forecast, presented by Jeff Perkins, showed consumer applications as the fastest growth area over the next five years. Consumer applications are projected to be over 40 percent of the MEMS market by 2012. According to Yole's just-released world MEMS market report, RF MEMS will grow fastest, followed by microfluidic chips for drug delivery and silicon microphones.

Players in the MEMS industry, from start-ups to Fortune 500 companies, have been working together as part of the **MEMS Industry Group** (MIG) to develop strategies for addressing industry challenges. Their focus during the past year has been on packaging, and MIG Managing Director **Karen Lightman** presented findings from their annual technical meeting last month. The MIG reports that use of wafer level packaging and through silicon vias (TSVs) is continuing to increase and that many device manufacturers are already bonding a capping wafer to the device prior to die singulation. Wafer Level Chip Scale Packaging is also emerging, especially for applications in RF IC's and MEMS filters, and is under development for optical MEMS device applications.

Emphasizing the shift from automotive to consumer markets, **Dr. Ken Yang**, manager of Advanced MEMS Development at **Analog Devices**, **Inc.**, presented 3-axis accelerometers used for cell phone and gaming applications. Yang discussed the advantages of laser dicing from the front side of the wafer to streamline the dicing process and reduce street size. He also described using TSVs to enable using an ASIC as the cap for a MEMS accelerometer, as well as in-situ capping to reduce cap thickness.

While the automotive market is growing slowly, there are opportunities in this sector, particularly for combustion control. **Dr. Venkat Chandrasekaran** of **Sensata Technologies** explained how microscale pressure sensors can control exhaust gas recirculation (EGR) in diesel engines. A MEMS pressure sensor is integrated into an existing glow rod inside the combustion engine, allowing tighter, closed-loop control over the combustion process. Researchers at **UC Berkeley** are developing a micro solid-state oxygen sensor based on yttria-stabilized zirconia to better control EGR and reduce smog emis-

sions. As presenter **Jonathan Rheaume** noted, additional process development is needed to make these sensors viable for high volume manufacturing.

After an overview of BioMEMS packaging by **Dr. Leslie Field**, founder of **Small-Tech Consulting**, **Zachary Ota Lee** discussed research at **UC Berkeley** aimed at solving the real-life problem of vaccine delivery in third world countries. Lee, a Ph.D. student of **Dr. Dorian Liepmann**, described a patch that uses microneedles for transdermal drug delivery. An array of 400 microneedles over a one cm<sup>2</sup> patch effectively vaccinates using one-tenth the dose required for traditional shots and eliminates much of the human error that occurs in storage and dilution when traditional vaccines are used in developing countries.

Dr. Luke Lee, Professor of Bioengineering at UC Berkeley, mentioned a number of biomedical applications in his keynote talk on "BioPOETIC" (Biologically-inspired Photonics-Optofluidics-Electronics Technology-based IC) packaging. As Dr. Lee explained, biologic chips are starting to surface in the medical market. Cells, like transistors, can be manipulated via biophotonic processes to eventually create high speed "biologic microprocessors." A wide variety of these chips are being developed to enable applications from microfluidic cell culture to artificial livers and compound eyes.

Technical Conference | August 17-21, 2008

The industry's best program on electronics assembly and advanced packaging

### Electronics Exhibition | August 19-20, 2008

A technology showcase featuring leading industry companies showing products and services

# Come. Focus.

### AUGUST 17-21, 2008 • ORLANDO, FL

Disney's Coronado Springs Resort and Convention Center

952.920.7682 • www.smta.org/smtai

# Rudolph Technologies

Process characterization solutions for microelectronics manufacturers: inspection, measurement, data analysis and test

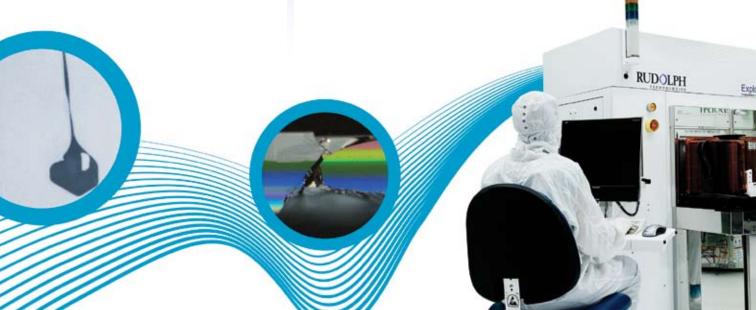

udolph Technologies has an established, long-term presence in the wafer processing fab as well as the packaging and test floor. The company maintains a leadership position by investing in aggressive research and product development to meet customer demand for performance and productivity. In addition, Rudolph's involvement in research programs and application initiatives with customers, industry consortia and other equipment suppliers is aimed at addressing critical challenges in microelectronics manufacturing.

#### **Process Control Metrology**

Rudolph has developed a line of production-worthy, fullyautomated systems for thin film process control that are used in major fabs around the world. Opaque films are measured with the patented Picosecond Ultrasonic Laser Sonar (PULSE®) technology, simultaneously measuring thickness and other properties of five or more metal film layers in a non-contact manner. To measure transparent films, Rudolph's S3000A Systems offer laser ellipsometers using patented Focused Beam Ellipsometry (FBE) technology.

#### **Automated Macro Defect Inspection**

Chip manufacturers deploy macro defect inspection throughout the fab to monitor key process steps and gather process-enhancing information. The all-surface Explorer<sup>™</sup> Inspection Cluster allows for a modular, flexible approach to meet specific process needs, and features a completely redesigned software interface focused on reducing cost of ownership. Rudolph maintains a leadership position in the back-end with a comprehensive solution for automated macro inspection with unique wafer handling capability.

#### **Probe Card Test and Analysis**

Added to the Rudolph portfolio in late 2007, this technology helps users to access the probing process, identify and analyze issues within the process and define solution options. Rudolph probe systems include high-resolution 2D and 3D probe mark and probe tip inspection as well as test and analysis for probe cards.

#### **Data Analysis and Review**

A complete suite of fast and effective software solutions has been developed and is supported by a dedicated Rudolph team. These products deliver fabwide and toolspecific yield and productivity management solutions to help process engineers turn raw data into useful information. Yield Optimizer<sup>™</sup>, for instance, is a powerful tool that analyzes the

relationships between in-process metrology measurements and end-of-line yield and electrical test results. It then will recommend changes to the in-process metrology targets to optimize the average end-of-line yield. Despite its highly complex algorithms, this product requires minimal training and setup time.

#### Supporting a Global Customer Base

The world's leading device manufacturers want to partner with suppliers who maintain regional operations centers for process support. Rudolph facilities, staffed with trained applications and service personnel, are strategically located in every semiconductor manufacturing region of the world.

#### **Rudolph History**

**1940** Otto Rudolph forms O.C. Rudolph & Sons, an importer of microscopes and scientific instruments that eventually becomes Rudolph Research Corporation.

The company continued to evolve, making breakthroughs such as the industry's first production-oriented ellipsometer for thin-transparent film measurements.

**1996** Investors contributed millions to bring Rudolph into the 21st century by expanding into additional metrology technologies. Its customer base was growing; the new organization was named Rudolph Technologies, Inc.

**1999** The company went public in 1999 (RTEC: NASDAQ); virtually all of the leading semiconductor firms were now placing orders for Rudolph systems. Investment in R&D programs continued, a new facility opened, and a new copper film measurement tool, the MetaPULSE<sup>®</sup>, was introduced.

**2002-2007** Several acquisitions contributed to Rudolph's growth following the turn of the century. ISOA, Inc., a Texas-based defect control company was acquired in 2002. This deal brought macro defect inspection into the company's growing portfolio. A merger with Minnesota-based August Technology Corporation added more inspection and analysis products to the company's product offering. The company remained based in Flanders NJ, now headquarters for its Metrology Business Unit. The Minnesota operation became home to the Inspection Business Unit, and a third Business Unit was established in Lowell, Massachusetts, to house the Data Analysis & Review group. Additional acquisitions in 2007 and 2008 of probe card test/analysis systems and 2D/3D inspection capability complemented the company's established presence in final manufacturing and test.

From its origins as an importer of microscopes and scientific instruments over 65 years ago, Rudolph has evolved into a process characterization leader within the semiconductor industry.

# Made Industry News

### STATS ChipPAC Appoints Hal Lasky Chief Sales Officer

UNITED STATES and SINGA-PORE – STATS ChipPAC Ltd., has announced the appointment of Hal Lasky as Executive Vice President and Chief Sales Officer for the Company.

Lasky will report directly to Tan Lay Koon, STATS ChipPAC's President and Chief Executive Officer, and will have overall responsibility for the Company's worldwide sales and product line management organization. He will provide the leadership on the Company's business, customer and product strategy. Lasky will be based in the United States.

"Hal is a world class executive with proven leadership and achievements in managing large scale global sales and product line organizations in the semiconductor industry. I am delighted that a person of Hal's caliber has agreed to join our senior management team to help take STATS ChipPAC to the next level of success," said Tan Lay Koon, President and Chief Executive Officer, STATS ChipPAC.

Prior to joining STATS ChipPAC, Lasky spent 24 years at IBM Corporation where he held a number of key leadership positions, most recently as Vice President of Worldwide Semiconductor Sales for IBM's Global Engineering Solutions group with responsibility for IBM's worldwide semiconductor revenue, sales strategy and strategic relationships with clients in the consumer, communications and IT markets. Prior to that, he held various senior management positions in IBM's Systems and Technology Group, Microelectronics Business Line and Interconnect Products Business Line.

Lasky holds a Bachelor of Science degree in Ceramic Engineering from Rutgers University and a Master's degree in Materials Science and Engineering from Columbia University. He is also a graduate of the IBM Client Executive Program at Harvard Business School.

### Amkor Technology Names Eric Larson Executive VP of Product Management Group

CHANDLER, AZ - Amkor Technology, Inc. has announced that Eric Larson will join the company as Executive Vice President Product Management Group. Larson, 52, will report to Ken Joyce, Amkor's President and Chief Operating Officer, and will have overall management responsibility for Amkor's Pro-duct Business Units, including Wirebond Products, Wafer-Level Processing and Flip-Chip Products, Test Services, R&D, Emerging Technologies and Corporate Development.

Larson brings more than 24 years of semiconductor and technology sector leadership experience to his new role. Larson started his career at Hewlett Packard where he worked for 17 years in a number of senior management positions including General Manager of the Integrated Circuits Business Division and General Manager of the Mobile Business Operation. He also served 7 years in senior management positions at Amkor from 1996 to 2003, including as President of our Wafer Fabrication business and Executive Vice President of Corporate Development. Larson is re-joining Amkor after having served in executive management positions with several start-up ventures.

For more information about Amkor visit www.amkor.com.

### Ken Joyce Named President of Amkor Technology

CHANDLER, AZ – Amkor Technology, Inc. has announced that Ken Joyce has been appointed President of the company. Joyce, 61, will al-so continue as Chief Operating Officer and will report to James Kim, Chairman and Chief Executive Officer. Joyce joined Amkor in 1997 and was CFO for more than 8 years before becoming Chief Administrative Officer in November 2007 and Chief Operating Officer in February 2008.

"Ken Joyce is exceptionally well qualified for this position. Ken has been a respected, proven leader for us and has the skills and experience to continue building our business and executing on our strategy," said James Kim, Chairman and Chief Executive Officer of Amkor.

Gil Tily has been named Chief Administrative Officer and Executive Vice President, succeeding Mr. Joyce in that role. Tily, 54, will remain as General Counsel and Corporate Secretary, reporting to James Kim, and will have responsibility for Finance, Legal and Human Resources.

For more information about Amkor visit www.amkor.com.

### AmTECH Strengthens Their Commitment to Quality

SAN JOSE, CA – AmTECH Microelectronics, Inc. is a leading Silicon Valley provider for SMT, COB, COF and IC Assembly since 1993. They have reinforced their focus on quality, service and FQA product yield by adding key process

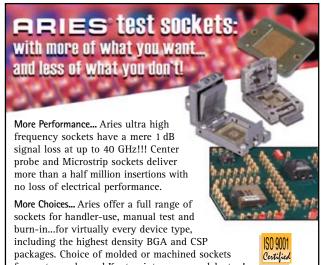

for center probe and Kapton interposer models, too! Less Cost... in addition to extremely competitive initial cost, Aries replacement parts and repair costs beat the competition, assuring you of lowest total cost of ownership.

Less Wait... Aries can deliver the exact sockets you need within 6 weeks.

So why settle? Aries makes it easy to get the world's best test sockets. Call or visit our web site to find out how!

Visit Aries Booth 7251 at Semicon West, July 15-17 San Francisco, CA

Bristol, PA 19007-6810 (215) 781-9956 fax: (215) 781-9845 e-mail: info@arieselec.com

www.arieselec.com

Sensible Solutions... Fast!

equipment such as YESTech Automated Optical Inspection (AOI) and XYLON/FeinFocus XRAY equipment. Their new YESTech AOI equipment has advanced 3-megapixel Thin Camera, RGB Fusion Lighting and telecentric lenses which enable exceptional defect coverage and extremely low false call rate which is necessary in order to improve quality and increase throughput of today's manufacturing process.

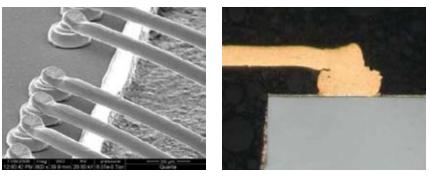

AmTECH has built a reputation to be a premier supplier for Chip-On-Board and Chip-On-Flex technology and has now added additional K&S Automatic Gold ball bonder capabilities to support IC Assembly and other fine-pitch wire bonding applications in their Cleanroom ISO 7 (Class 10,000).

Call 408-227-8885, email info@amtechmicro.com or go to www.amtechmicro.com for more information.

### SUSS MicroTec Signs License Agreement with Philips Research to Develop a New NanoImprinting Technology

MUNICH - SUSS MicroTec. supplier of innovative solutions for the 3D, MEMS, Advanced Packaging and Nanotechnology markets, has entered a license agreement with Philips Research, Eindhoven, The Netherlands, for a new enabling technology called Substrate Conformal Imprint Lithography (SCIL). The aim of this cooperation is to bring an existing equipment platform with this additional Nanoimprinting (NIL) feature to the market, enabling new approaches to large-area imprint applications along with excellent printing resolution and repeatability.

This new imprint technology for sub-50nm patterning is bridging the gap between small rigid stamp application for best resolution and large-area soft stamp usage with the usual limited printing resolution below 200nm. SCIL is an enabling technology offering the best of two worlds – large-area soft stamps with repeatable sub-50nm printing capability, avoiding stamp deformation as no contact force is applied, non-UV based curing at room temperature and allowing high aspect ratios even up to 1:5 and more.

The lab aligner platform from SUSS MicroTec, handling the 150 and 200 mm UV-lithography like MA6 and MA8, will be available and upgradeable with this feature. Immediate availability for sampling is given with the current test setup. Market introduction with fully implemented SCIL functionality into SUSS' lab aligners is scheduled for later this year.

### OLOVO Announces Agreement for Supplying Advanced Packaging Wafer Bumping Plating Anodes

OLOVO, LLC, a leading lowalpha and interconnect materials supplier, has reached an agreement with Semitool, Inc. whereby OLOVO has become licensed to supply anodes for use in Semitool's electrochemical deposition systems. OLO-VO's qualification as an authorized vendor allows OLOVO to expand the reach of its lowalpha products to Semitool's customer base and to provide them with an additional source of specialty low-alpha and interconnect materials.

According to Peter Emanuel, VP of Sales at OLOVO, "We are extremely happy with this arrangement with Semitool, and we look forward to supplying Semitool's customer base with high quality plating anodes, which are a key component in the wafer bumping process. We believe this offers tremendous mutual benefit to our respective companies and clients." Surface mounted device with delamination (red) along the entire length of several leads. This part would fail per J-STD-020 criteria.

# SonoLab" is Your Lab

SonoLab, a division of Sonoscan<sup>®</sup>, is the world's largest inspection service specializing in Acoustic Micro Imaging (AMI). Through SonoLab, you'll have access to the superior image quality and reliable data accuracy of Sonoscan C-SAM<sup>®</sup> acoustic microscopes, plus the capabilities and careful analysis of the world's leading AMI experts.

With worldwide locations, unmatched capabilities, extensive experience and the best equipment available, SonoLab gives you the ability, flexibility and capacity you need to meet all your AMI requirements.

#### SonoLab<sup>™</sup> Services

- Component Qualification to Industry Standards

- Materials Characterization and Evaluation

- High-Capacity Screening and Lot Reclamation

- Failure Analysis and Constructional Analysis

- Inspection and Audit Services

- Custom Training

To learn more visit www.sonoscan.com/sonolab

800-950-2638 • 847-437-6400 • www.sonoscan.com Santa Clara, CA • Scottsdale, AZ • Elk Grove Village, IL • Burlington, MA North America • Europe • Asia

# Made Industry News

OLOVO, LLC is a supplier of low-alpha products which help reduce 'soft errors' in sensitive flip-chip applications. Soft errors are mistakes in logical calculations caused by collisions between alpha particles and logic components in embedded memory and highspeed integrated circuits. Traditional solder materials used in flip-chip interconnect are naturally high in alpha particle emission, causing unacceptable soft error rates in circuit devices. OLOVO is a privately held company with headquarters in Menlo Park, California, USA.

For more information visit www.olovo.com.

### Sonoscan Introduces Acoustic Profiling Module

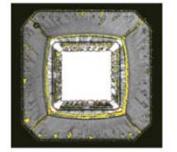

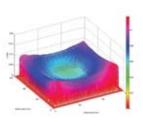

ELK GROVE VILLAGE, IL – Sonoscan has introduced a new capability for its line of C - SAM acoustic microscopes that reveals the external surface topography of a device at the same time as its internal features. Known as the Acoustic Surface Profile (ASP) module, this important mode can be used to measure warpage of plastic integrated circuits, flip chips, substrates, circuit boards, etc., without any sample preparation.

ASP is available as a cost effective option on new C-SAM acoustic microscope systems as well as a retrofit to many systems acquired over the last few years. ASP works by collecting acoustic surface data and displaying it as a color-coded image in which each color corresponds to a topographical distance measurement. The sensitivity of the ASP is in the micron range and is not dependant upon the surface smoothness, color or optical characteristics.

Warpage at the surface of a part is often associated with internal problems such as cracks and delaminations that

Planar acoustic image of BGA (left) reveals multiple anomalies (yellow, dark gray) between molding compound and substrate around the periphery of the component. Acoustic Surface Profile (right) shows that the vertical warpage from the center of the part to the corners is 125 microns.

can cause electrical failures. For example, the surface profile of a plastic-encapsulated IC may show warpage in one quadrant. Internally, the same quadrant may reveal leadframe delaminations. Having both images makes it easier to identify the processes that are causing the problem.

The value of ASP is that it displays both the surface profile and the internal features on a single instrument, eliminates the need to buy a second instrument, and requires no additional scanning time, as the profile data is taken at the same time as the acoustic image data. If a part is tilted, ASP corrects for tilt before profiling the surface.

For more information contact Steve Martell, manager of technical support services, Sonoscan, Inc., 2149 E. Pratt Blvd., Elk Grove Village, IL USA 60007. Phone: 847 437-6400 x 240. Email Info@ sonoscan.com.

1217 WILDWOOD AVENUE • SUNNYVALE, CA 94089

### Precission Process Introduces the Excellite FSP

Process Partners International, the partner effort between Precision Process Equipment and PAT, has expanded their team to include Sidney Qiu, Sales & Service Engineer now located in Shenzhen City Mainland China. Contact Sidney at +86 13510083568 or email sqiu@ processpartnersinternational. com.

Precision Process has also introduced the Excellite FSP: A New Dimension for Flexible Substrate Plating Technology. Ever increasing demands for HDI production processes call for innovative, future-oriented solutions. The Excellite FSP is a roll-to-roll, continuous strip, electroplating and wet processing system designed principally for flex circuits, RFID, and solar cells while having a variety of other electronics and metal finishing applications. View the full brochure at http://www. processpartnersinternational. com/pdfs/PPE\_FlexibleSubstrate\_RFIDBrochure.pdf

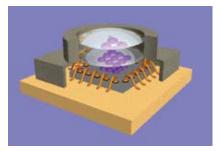

### New Centipede Systems Optical Socket Is Ideal for Testing Wafer-Level Camera Chips

SAN JOSE, CA – Centipede Systems has developed a new optical socket suitable for testing the current and next-generation wave of chips used in wafer-level camera modules.

The initial optical socket entry, part of Centipede's Centurion<sup>TM</sup> product line, is offered in a clamshell configuration for an individual integrated circuit. Currently, Centipede's optical sockets with a grid pitch as small as 0.4mm are available.

Testing camera chips requires that the surface of the device be held accurately in the optical plane without deviation or deflection caused by contactor forces. To ensure accuracy, Centipede's optical sockets align a datum plane on the chip's surface to the lens or optical system with minimal stress on the chip.

"Most existing test socket technology is about a half century old and incapable of testing complex optical chips," noted Dr. Thomas H. Di Stefano, president of Centipede Systems. "Although our initial optical sockets are for testing single camera chips, we are developing sockets for testing arrays of camera chips".

One of the leading providers of optical technologies, based in San Jose, California, is an early adapter of Centipede's optical sockets for wafer-level camera chips, Dr. Di Stefano noted.

Centipede Systems is a technology leader in connectors and sockets in applications where performance, power and density are critical.

### ASM Pacific Launches MCM12 Automatic Multi-Chip Bonder

HONG KONG – ASM Pacific Technology has announced its latest generation large area chip bonder to address the growing market for MCM, SIP, and hybrid applications. The MCM12 is a fully automatic multiple die, SMD, and flip chip bonding system with up to 12 inch wafer handling capability. A variety of processes can be integrated on this single platform solution including: direct die, flip chip, stack die, and SMD bonding.

It is highly flexible and can handle a wide range of die sizes and presentation modes. The MCM12 is equipped with a fully programmable dispensing system and automatic pick up and ejector tool changing systems. The bondhead can achieve 800 gram force and is

10987 Via Frontera • San Diego, CA 92127 • 858-674-4676 • Fax 858-674-4681 a division of Delphon

### 15th Annual International

September 7-10, 2008 Embassy Suites Napa, California

featuring in-depth presentations of technical developments and market trends, and opportunities to network with suppliers and industry experts

www.napakgd.com

# The Power of Known Good Die

**Embedded Component Trends**

SiP Architecture & 3D Packaging

**KGD Engineering**

**Test methods for KGD**

**Applications of Die Products**

**Future Trends**

Hosted annually by the Die Products Consortium www.dieproducts.org

# MEDIC Industry News

programmable to automatically change up to 14 different pick up tools. High accuracy and throughput are achieved with this linear motor driven, gantry style platform. In flip chip operation, the machine is capable of +/- 10 micron accuracy.

The MCM12 material handling system addresses leadframe and substrate sizes up to 200mm x 300mm in stand alone and SMEMA configurations. Workholder conversion is simplified by using motorized tracks with dedicated vacuum anvil blocks.

For die presentation, the MCM12 can accommodate sawn wafers up to 300mm diameter on film frames, sawn wafers on rings, and waffle packs. In addition, up to 5 types of passive components in tape and reel format can be accommodated on the optional front loading SMD handling module.

The three in one operation linear motor driven process head contains the bondhead, writing dispense system, and down looking inspection and alignment camera. Full vision capability includes alignment and inspection of epoxy dispense pattern, die, and post placement inspection.

For more information email inquire@asmpt.com, or visit www.asmpacific.com.

### Major Breakthrough in Ceramic Design Software

SAN JOSE, CA - CAD Design Software announces the results of a major LTCC design test conducted by a leading U.S. defense foundry. After substantial development followed by implementation at a key government prime contractor site, the result is a dramatic reduction in overall design time. The prime defense contractor reported, "The special LTCC design and Gerber package that CDS has designed for LTCC has essentially allowed us to reduce our tooling generation time for complex cer-amic designs from 40-80 hrs to 2-8 hrs. This is a significant savings in cost, production flow and quality of our LTCC products."

"Through working closely with numerous military and commercial LTCC customers and material suppliers, we have been able to incorporate new automation functionality and materials handling capabilities in our Hybrid/MCM Design Suite that allow our customers to dramatically reduce their design time. We are very pleased that our customers are experiencing substantially reduced time to market, a benefit now available to all of our customers", said Gordon Jensen, CAD Design Software's vice president of sales and marketing.

Call 408.436.1340, e-mail info@cad-design.com, or go to www.caddesign.com for more information.

## Global Low-Cost Wafer Bumping Services

- Quick-turn and mass-production

- Highly competitive, low-cost bumping technology

- Exceptional quality through high-level expertise

### PAC TECH

Pac Tech GmbH Tel: +49 (0)3321/4495-100 sales@pactech.de www.pactech.de

#### Pac Tech USA Tel: 408-588-1925, ext. 202 sales@pactech-usa.com www.pactech-usa.com

Pac Tech Asia Sdn. Bhd. Tel: +60 (4) 6430 628 sales@pactech-asia.com www.pactech-asia.com

### NAGASE & CO., LTD.

Tel: +81-3-5640-2282 takahiro.okumura@nagase.co.jp www.nagase.co.jp

#### **Available Processes**

- Electroless Ni/Au under-bump metallization

- Ni/Au bump for ACF or NCP assembly

- Solder paste stencil printing

- Solder ball drop for wafer-level CSP

- Solder jet for micro-ball placement

- BGA and CSP reballing

- Wafer backside thinning and wafer dicing

#### **Special Features/Technologies**

- Over 10 years experience

- U.S. Government Certified

- 4- to 12-inch wafer capability

- Wafer pad metallization: Al and Cu

- Solder alloys: eutectic SnPb37, lead-free, low-alpha, and AuSn

- Fluxless and contactless bumping for MEMS and optoelectronics

- Ni/Au interface for wire-bond applications

The leader in low-cost electroless wafer bumping.

# Main C Industry News

### STATS ChipPAC Introduces Tool to **Reduce Cycle Time & Increase Flexibility of RF** Designs

UNITED STATES and SIN-GAPORE - STATS ChipPAC Ltd. has announced a new IPD Products Databook which contains a library of silicon-based Integrated Passive Device (IPD) designs to assist semiconductor companies in reducing design cycle time and increasing integration options in Radio Frequency (RF) applications.

With the growing industry trend for increased integration in a smaller form factor, passive devices such as filters, diplexers, baluns and matching networks are being placed in packages alongside active semiconductor integrated circuits (ICs). As wireless systems have become smaller, there has been an increasing need to shrink passive devices, especially in terms of height. Design specifications, however, often compromise performance to achieve the desired level of miniaturization.

By integrating and fabricating passive devices at the silicon wafer level, STATS ChipPAC is

able to produce IPDs in both wire bond and flip chip format which are significantly smaller, thinner and higher performing than standard dis-crete passive devices that are commercially available. Silicon-based IPDs enable semiconductor companies to effectively reduce device footprint and reduce interconnect complexity, while improving component tolerance, yield and reliability in RF applications such as GSM/DCS and CDMA cellular phones, Wireless LAN 802.11 a/b/g and WiMax systems.

The complexity of designing RF circuits typically translates into multiple design iterations and longer evaluation cycles. This is a factor that affects the speed at which semiconductor companies are able to bring their products to market. STATS ChipPAC has taken the next step in complex RF integration designs by offering semiconductor companies a tool to reduce cycle time and increase the flexibility of their RF module designs. The new IPD Products Databook contains technical information such as size, layout, component values and basic tolerances for complete IPD structures in a wide range of products.

For more information go to www.statschippac.com.

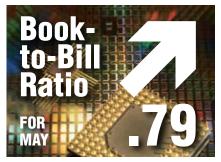

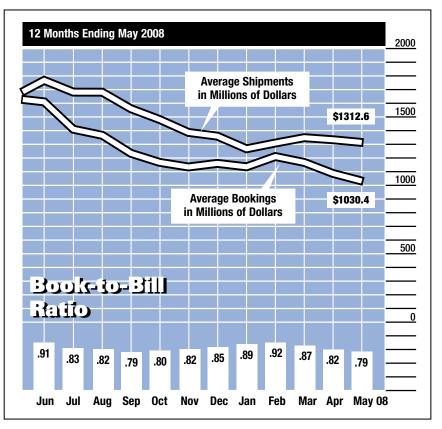

# North American Semiconductor Equipment Industry Posts May 2008 Book-To-Bill Ratio of .79

SAN JOSE, CA - North America-based manufacturers of semiconductor equipment posted \$1.03 billion in orders in May 2008 (three-month average basis) and a book-to-bill ratio of 0.79 according to the May 2008 Book-to-Bill Report published by SEMI. A book-to-bill of 0.79 means that \$79 worth of orders were received for every \$100 of product billed for the month.

The three-month average of worldwide bookings in May 2008 was \$1.03 billion. The bookings figure is about five percent less than the final April 2008 level of \$1.09 billion, and about 37 percent less than the \$1.64 billion in orders posted in May 2007.

The three-month average of worldwide billings in May 2008 was \$1.31 billion. The billings figure is about two percent less than the final April 2008 level of \$1.34 billion, and about 21 percent less than the May 2007 billings level of \$1.67 billion.

"Booking are approaching levels observed in 2005, which was the last time the semiconductor industry reported a year-over-year decline," said Stanley T. Myers, president and CEO of SEMI. "The data does not indicate a change in this trend over the next quarter."

three-month moving average bookings to millions of U.S. dollars. three-month moving average shipments.

The SEMI book-to-bill is a ratio of Shipments and bookings figures are in

# MEDIC Industry News

(continued from page 18)

### March Plasma Systems Announces Low-Cost PM-100 Plasma System

CONCORD, CA - March Plasma Systems, the global leader in advanced plasma treatment systems, has announced that it has released the PM-100 plasma system, which is designed to be a low-cost, highly effective plasma treatment solution for treating electronic components, printed circuit boards, and medical & life science devices. The PM-100 plasma system is ideally suited for laboratories, universities and research and development (R&D) facilities that are highly sensitive to the cost of capital equipment.

"The PM-100 plasma system opens up a new world of economical plasma processing for small-budget operations," said Frank Huysmans, vice president of sales at March Plasma Systems. "These facilities typically know and understand the value of plasma treatments, but have been locked-out from acquiring equipment due to high system costs. The PM-100 plasma system instantly solves this dilemma, and provides the plasma capabilities that laboratories, universities and R&D facilities require at an extremely attractive price point."

The PM-100 plasma system comes with a 12-month limited warranty on parts and labor, and is available for shipment to customers world-wide. Contact March Plasma Systems for further information.

### Attendance Numbers Confirm IPC Show in Vegas All About Getting Down to Business

BANNOCKBURN, IL – IPC – Association Connecting Electronics Industries<sup>®</sup> has released the audited attendance figures for IPC Printed Circuits Expo®, APEX® and the Designers Summit held April 1-3, 2008, at Mandalay Bay Resort & Convention Center, Las Vegas. Participation in the educational offerings including the Technical Conference, Tutorials/Workshops, Management Meetings and Designers Day put the event in the IPC record books with 2,773 educational program attendees, a 45 percent increase over 2007 and a 26 percent increase over 2006 in Anaheim.

As many trade publications have reported, the increased participation was evident throughout the show. Many committee meetings were packed, luncheons were filled to capacity, and special events like the Women in Electronics networking meeting and firsttimers breakfast were standing room only.

To punctuate the fact that IPC APEX EXPO<sup>™</sup> is global, international attendance grew

from 12 percent in 2007 to 16 percent in 2008, with representatives from 47 countries. Total verified attendance was 5,102.

The exhibitor base was as strong as ever before with 442 exhibiting companies. Exhibitor attendance for 2008 was 4,174, bringing total verified visitors for the event to 9,276. These numbers only tell part of the story. As an exhibitor, Christopher Perry, EMC Global Technologies, Doylestown, Pa., said, "The show was really good. We are very pleased with the traffic and the leads."

IPC President Denny McGuirk said the responses from exhibitors and attendees validated the choice to move the event to Las Vegas. "Judging from the preliminary results of surveys from both attendees and exhibitors, Las Vegas was an unqualified hit. When we asked, 'How was Las Vegas as a destination for an IPC show?' 45 percent of attendees gave the event the highest rating - they loved it," McGuirk said.

# MEDIEC WLP Technology

# Wafer Level Cavity Package Using Via-through Pad Interconnects

#### Giles Humpston Tessera, Inc.

olid state images are manufactured in vast numbers. Typically each year more than one billion are made for the cell phone. automotive and computer industries. However, the continued drive toward solid state imagers having ever greater pixel numbers and smaller pixels adversely affects yields. The mechanism for loss is contamination of the delicate optical sensor during assembly of the camera module. The solution being progressively adopted by industry is to package the semiconductor die, preferably using wafer-level technology owing to the favorable economics of the process.

One of the more challenging aspects of wafer-level packaging is the interconnect scheme. Of the choice between top, side or bottom contacts, bottom contacts are attractive since they permit the imager die to be face-upward, which is the orientation necessary for use in a camera module. While through silicon vias (TSVs) are technically attractive for this application, the technology can not yet deliver on price and reliability.

Described is a cavity package for solid state image sensors that is fabricated at the wafer level. This package uses a novel TSV interconnect that makes direct contact to the die bond pads through the thickness of the silicon. The small size and location of the interconnect leaves the rear face of the package available to support a ball grid array interface, making the package compatible with surface mount assembly processes. Unusually, the materials of the package construction are sourced from the automotive industry where they are used in huge volume and are therefore very cheap. This is done to keep costs as low as possible. Packaged imagers are able to surpass by a wide margin, the exacting reliability requirements of the automotive industry, both at the package and board level.

#### Introduction

Typically each year more than 1 billion image sensors are manufactured. These primarily find application in portable electronics products such as camera phones, digital still cameras and increasingly in webcams, laptop computers, toys and cars. Predictions are this market will continue growing for some years as cell phones with multiple cameras become the norm and automotive driver aids enter the video age. This usage could entail 10 or more cameras being installed on each vehicle and grow to be a market equal in volume to camera phones. Optical mice are also based on image sensing technology, but are usually counted separately from camera modules because, by comparison, their resolution is very low and there are considerable differences in the optics design.

Figure 1. Camera module assembled using chip-on-board processes. The lens turret housing forms a seal over the exposed die. Drawing not to scale. *Source: Tessera*

In common with most other semiconductor devices, solid state image sensors require some form of enclosure in order to ensure longevity. Traditionally for imagers this was achieved using chip-on-board (COB) assembly processes. In this scheme the imager is attached to a substrate, using a conventional die attach adhesive and wire bonds form connections between bond pads on the die and lands on the substrate. The substrate forms the base of the enclosure. Over the die is then placed a lens turret, which houses the optical train of the camera. The lens turret is sealed to the substrate so the lower optical surface in the lens train, in combination with the sidewalls of the turret, forms the enclosure for the die. This is illustrated in Figure 1. Typically the optical train will comprise between two and four lenses, a stop, two apertures and an infra-red filter. The infra-red filter is necessary because silicon image sensors are sensitive to radiation longer than the human eye can perceive.

COB assembly has two principal draw-

backs. The first is that the cost of assembly is incremental for each camera module manufactured because the process involves integrating parts in a singular manner. A second limitation is that the imager die is totally unprotected until the final assembly operation when the lens turret is attached. Current leading-edge CMOS imagers have pixels that measure  $1.75\mu m$  on a side and road maps of the semiconductor companies show this reducing to  $1.4\mu m$  in 2009. This in itself is not a problem except the optically active area of the image sensor is covered with tiny polymeric lenses to help boost the signal-to-noise ratio. If a particle larger than about 20% of the pixel dimension lands on an imager it results in a black spot in the image. The polymeric lenses are mechanically extremely fragile and incompatible with most solvents, so are virtually impossible to clean. Many back-end semiconductor assembly processes, like wafer sawing, die thinning, die attach and wire bonding were never designed to be ultra-clean. It is therefore not surprising that more than 90% of defects in camera modules, identified on first test, are related to contamination by particles<sup>1</sup>. The short-term solution is to invest in clean rooms and operator training. However, many solid state camera module manufacturers are already operating Class 10 environments, or better, so there is not a great deal of scope for further improvement at affordable cost.

#### Wafer Level Packaging

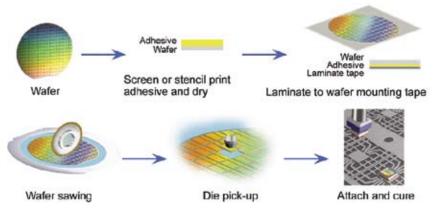

Wafer-level packaging (WLP) is an alternative approach to providing a protective enclosure for solid state imagers. The basis of the process is to package the die while they are still in wafer form before the start of the back end assembly processes. The wafer is then singulated to free individually packaged die.

Wafer-level packaging provides three benefits that have great value for image sensors. Firstly, the costs of packaging are shared among the good die on the wafer. With typically several thousand die on a 200mm diameter image sensor wafer this greatly reduces packaging costs per die compared with discrete packages. Secondly, the dies are protected from the very first step of the process so that yield loss from

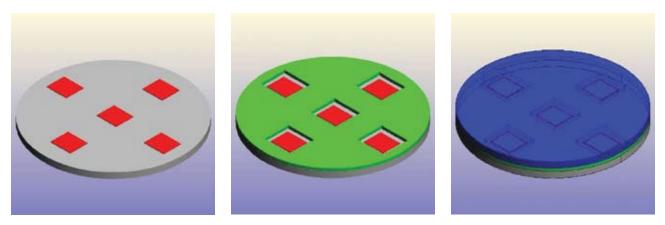

Figure 2. Formation of a wafer-level cavity package. Left - the device wafer containing five die. Middle - application of the seal material to form a picture frame around the perimeter of each die. Right - attachment of a lid material to seal the cavity over each die. Singulation frees the packaged die from the wafer, an example of which is shown in Figure 3. Source: Tessera

contamination by particles is effectively eliminated; not only can the glass surface be cleaned easily, but any remaining contamination is away from the focal plane and hence must be proportionately larger to appear as a defect in the image. The final benefit is that it is possible to provide the packaged die with a ball grid array (BGA) interface on its underside. This permits the camera module to be soldered to the main printed circuit board of the product at the same time as all the other semiconductor and passive components. Without this feature the camera module has to be assembled separately and connected to the main board by a flexible circuit and connector. Unreliability of these connectors is the major cause of field returns of camera phones with reportedly defective imagers. Owing to these benefits it is forecast that by 2012 more than 65% of all imagers will be enclosed in a wafer-level package with a BGA interface<sup>2</sup>.

A wafer-level cavity package for an image sensor is achieved by forming a picture frame of adhesive around each die on the wafer, attaching a glass wafer and then sawing the assembly to yield individual die, each with a cover over the delicate image sensor area. This process is illustrated schematically in Figure 2. The requirement for the cavity owes to the lenses on the surface of the imager; an air space being necessary to achieve maximum refractive index change at the lens/air interface. Typically, the cavity height is around  $40\mu$ m.

#### Wafer Level Package Interconnects

One of the major challenges of wafer level packaging is making contact to the bond pads. Bond pads in their traditional location on the front face of the die are rendered inaccessible by the glass cover that protects the optically sensitive area of the die. An obvious solution is through silicon via (TSV) technology. There are many variations of TSVs, a common implementation being a hollow pipe, with near-vertical sidewalls, machined through the thickness of the silicon. Onto the sidewalls of the pipe is applied a dielectric film overlaid with conductive metal. The through via is machined by deep reactive ion etching using the Bosch process<sup>3</sup>.

Despite being technically possible for many years, TSVs have never been adopted in high volume manufacture. There are several reasons for this notable amongst which is the high capital cost of the equipment required, the slow etch rate of silicon, which curtails throughput, and the complexity of the additional process steps to fabricate conductive vias that are simultaneously insulated from the silicon through which they pass. There are also issues of reliability that have not yet been satisfactorily solved without additional cost. Points of weaknesses in the design include dielectric and conductive coating of the side walls of a high aspect ratio pipe; the 90 degree bends at the top and base of the pipe that the redistribution layer (RDL) must traverse and maintain connectivity during thermal cycling; and the difficulty of cleaning the back of the bond pad so the RDL can make an Ohmic contact, when it is the bottom of a long narrow pipe.

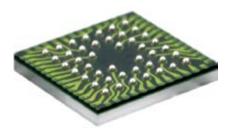

A modern wafer level package for image sensors is typified by the SHELLCASE<sup>®</sup> MVP solution, an example of which is shown in Figure 3. In this design connection between the bond pads and the ball grid array on the rear face of the package is by a via-through-pad technology. This solution means there are few restrictions on the bond pad size, pitch or location, making it directly compatible with the majority of

Figure 3. Image sensor packaged at the wafer level and provided with a ball grid array interface to simplify and cheapen attachment to a printed circuit board. *Source: Tessera*

existing CMOS imagers. The dicing lanes can be as narrow as the silicon design rules allow, which helps to maximize the number of die per wafer and decrease unit cost. The packaged imager thickness is approximately  $500\mu$ m, making it imminently suitable for electronics products where the current fashion is for extreme thinness.

The via-through-pad interconnect superficially resembles a TSV but the differences are important and have profound implications for the product cost and reliability. In this contact the RDL penetrates through the thickness of the bond pad to form a circumferential edge contact. Because the act of penetrating the bond pad exposes fresh metal at the circumference this solution obviates the difficulty of making Ohmic contact between the RDL and the bond pad. The via-through-pad contact is structurally identical to the well established edge contact<sup>4</sup> and hence has the same inherent reliability. Indeed, edge contacts have an in-service record exceeding a decade, based on a sample size of nearly 50 billion interconnects.

Via-through-pad interconnects require passageway through the silicon wafer. However, unlike TSVs, the opening is purely mechanical and needs only to expose sufficient area of the bond pad to permit formation of the via-through-pad edge contact. Consequently the alignment accuracy and limits on pitch are modest since several interconnects can share a single passageway. Because the passageways through the silicon do not have to be individual, the profile of the openings can be relaxed to a trapezoid with rounded corners. This eliminates two of the major sources of unreliability of TSVs. Finally, because via-through-pad interconnect is based on polymer technology with a single RDL it is very cost-effective compared with other TSV solutions.

#### **Electrophoretic Materials**