Volume 12, Number 3

report

#### **QUARTER THREE 2008**

A Publication of The MicroElectronics Packaging & Test Engineering Council

**INDUSTRY NEWS**

**STATS ChipPAC Ltd.** has announced an innovative USB module for NAND flash memory applications. *page 15*

**Pac Tech Packaging Technologies** held a grand opening celebration on September 18 at its new 55,000 square foot facility in Penang, Malaysia. The new facility provides state-ofthe-art wafer bumping and backend processing for semiconductor companies within the Pacific Rim. *page 16*

## RUDDLPH

**Rudolph Technologies, Inc.** has announced the receipt of orders from a major European semiconductor manufacturer for two WaferWoRx<sup>®</sup> 300 Probing Process Analysis Systems. *page 19*

**SEMI** projects an over 20 percent increase in world semiconductor fab equipment spending in 2009, driven by over seventy fab projects, according to their World Fab Forecast report. *page 21*

The 5th Annual International Wafer-Level Packaging Conference returns to San Jose October 13 through 16. *page 13*

**Celebrating MEPTEC's 30th Anniversary**

# Packaging Developments and Innovations

From System Design to Integrated Delivery

One Day Technical Symposium and Exhibits Coming to San Jose, CA November 13th ... page 4

#### MEMBER COMPANY PROFILE

**Promex Industries Inc.** has been a Silicon Valley microelectronics manufacturing services provider for over thirty years. Originally focused upon providing engineering build prototyping services to the local Silicon Valley community, Promex has outgrown those humble beginnings to become a full service IC Assembly & Custom Chip Packaging Foundry. What makes Promex unique is its ability to enable their customers to take new products to market faster than by any other route. *page 10*

romex's customer base includes the major multinational semiconductor companies, fab-less semi-

conductor houses, high tech startups and emerging high tech companies. End-use markets include both commercial and military electronics as well as, RF, bio-tech, bio-metric, PV solar and optoelectronics products.

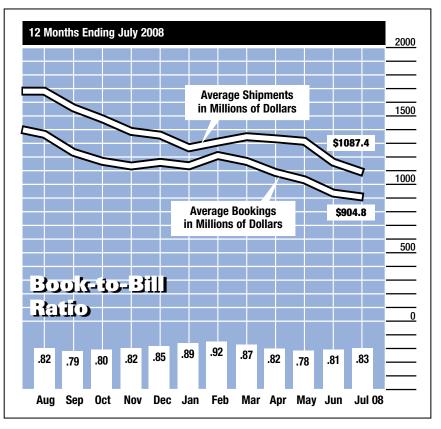

Semiconductor equipment bookings decrease 3% over June 2008 level. *page 20*

# consistent quality

Six Sigma, metrics, unified operating systems...we leverage the appropriate tools and processes to ensure that our products meet or exceed your quality requirements.

Honeywell's ongoing research and development in chemistry, metallurgy, and the processes that bring them together—from our new packaging R&D facility in Spokane, Washington, to our

technology center in Shanghai, China—ensure that wherever challenges arise, we'll continue to create solutions that solve them. And as a partner to most of the top semiconductor houses worldwide, our technology portfolio is consistently at the forefront of invention, empowering the global leaders of innovation. Honeywell Electronic Materials—because the quality of your products depends upon ours.

## Honeywell

Contact Honeywell for solutions to your puzzle... visit www.honeywell.com/sm/em or call 1-408-962-2000.

Volume 12, Number 3 A Publication of The MicroElectronics Packaging & Test Engineering Council

P. O. Box 222 Medicine Park, OK 73557 Tel: (650) 714-1570 Email: info@meptec.org

#### Published By MEPCOM

Editor Bette Cooper

Design and Production Gary Brown

#### **MEPTEC Advisory Board**

Seth Alavi SunSil

Jeffrey Braden LV Sensors, Inc.

Philippe Briot P. Briot & Associates

Joel Camarda

Exar Corporation Gary Catlin Plexus

Plexus Tom Clifford

Rob Cole

John Crane J. H. Crane & Associates

Jeffrey C. Demmin Tessera

> Bruce Euzent Altera Corporation

> > Skip Fehr

Julia Goldstein Advanced Packaging Magazine

> Anna Gualtieri Elle Technology

Bance Hom Consultech International, Inc

Ron Jones N-Able Group International

Nick Leonardi Premier Semiconductor Services

> Phil Marcoux TPL Group

Bhavesh Muni Henkel Corporation

Mary Olsson Gary Smith EDA

Marc Papageorge Semiconductor Outsourcing Solutions

> Rich Rice ASE (US) Inc.

Jim Walker Gartner Dataquest

Russ Winslow Six Sigma

MEPTEC Report Vol. 12, No. 3. Published quarterly by MEPCOM, P. O. Box 222, Medicine Park, OK 73557. Copyright 2008 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact John Waller at 215-646-7838, Fax 215-646-0504.

## Council Update

ummer always seems to go by so quickly, and as this issue is being distributed it is officially the beginning of autumn. After taking a couple of months off, September marks our luncheon series kick-off with **Gartner-Dataquest**'s traditional state-of-the-industry report. In both Sunnyvale and Phoenix, **Mark Stromberg** spoke on 2009: *Return to Industry Growth or a Repeat of 2008?* For a copy of this presentation please contact bcooper@meptec.org.

Our first post-summer event was our *3rd Annual Medical Electronics Symposium*, with emphasis on technology concepts that enable product reality. **Arizona State University** and **Connection One** (**Ira A. Fulton School of Engineering**) hosted the event at the historic Old Main building on the Tempe campus. We'd like to thank **ASU** for their great support in putting this event together. If you missed it, CDs of the presentations will be available — contact MEPTEC for information on ordering.

We're also pleased to be offering a new series of *MEMS Workshops*, in conjunction with **MEMS Investor Journal**. On October 22 the first workshop will be held at the **Ramada Inn** in Sunnyvale called *MEMS Testing and Reliability: Lessons Learned from the MEMS and Semiconductor Industries*. See below for more information on this event.

This issue will be distributed at our Q4 one-day technical symposium being held on November 13, 2008 at the **Wyndham Hotel** in San Jose, California. The symposium is entitled "*Packaging Developments and Innovations: From System Design to Integrated Delivery*". We are celebrating our 30th anniversary with this event by teaming up with **Advanced Packaging Magazine** as co-sponsors. See page 4 for information.

One of our feature articles this issue is from MEPTEC member company **Bayside Design, Inc.** In *"Fundamental Challenges in High-Performance Package Design"*, **Daniel Lambalot**, Director of Engineering at Bayside, discusses the challenges engineers face when designing a first-pass working package. Read this informative, thorough report on page 22.

The other feature article is again from a MEPTEC member company, **SemiProbe**. **Don Feuerstein** discusses "Why 3D Interconnect and New SiP Packaging Schemes are Demanding KGD for MEMS *Devices*" (see page 26). Don starts out by mentioning that the creator of Moore's Law, **Gordon Moore**, admits that the physical limits of his law are rapidly approaching. Don then goes into the reasons that make supplying MEMS KGD important. We'd like to thank both authors for their feature article contributions.

Our University profile this issue is the **University of Colorado** – *i***Mint** (Integrated Micro/Nano-Electromechanical Transducers) Center. The Center includes collaboration with many different entities, including universities, government agencies, and industry businesses. Several revolutionary discoveries and inventions have resulted from the Center. One of the most interesting is Graphene – a material so strong that "it would take the weight of a two-ton car to puncture a sheet as thick as ordinary food wrap". Read about "the stuff of science fiction" on page 8.

Our Industry Analysis this issue is from **Yole Développement** on "3-D TSV Interconnects – The Next Revolution for Semiconductor Packaging and Circuit Assembly Industries" (page 5). They present their latest market forecast evaluating the impact of 3-D TSV technologies on several different segments of the semiconductor industry.

**Phil Marcoux**, MEPTEC Advisory Board member and Director of Business Development at **TPL Group** contributed the editorial to this issue. In "*Is it Time to Leave Solder*?", Phil offers his opinion on how the elimination of solder may solve many problems, one of which is a means to avoid the risks faced by the use of no-lead solder. Read his interesting and provocative piece on page 34.

Our Member Company Profile this issue is from Corporate MEPTEC member **Promex Industries Inc.** Founded over 30 years ago, Promex began by providing engineering built prototyping services that serviced mostly the local Silicon Valley community. Over the years they have evolved into a full service IC assembly and custom chip packaging foundry serving customers worldwide. See page 10 for the profile of "Silicon Valley's Packaging Foundry".

Thanks to all of our contributors for making this a great issue. If you're reading our publication for the first time at one of the many events where we distribute, or if you're a new member, we hope you enjoy it. Thanks for joining us!

#### **MEMS Testing and Reliability Workshop**

On October 22 a workshop will be held at the Ramada Inn in Sunnyvale titled *MEMS Testing and Reliability: Lessons Learned from the MEMS and Semiconductor Industries.*

MEMS testing and reliability assurance are some of the most critical processes to ensure high yields and profitability. According to recent studies, the total world MEMS test equipment market generated revenues of \$50-\$60 million in 2007, at a growth rate of approximately 10 percent. While MEMS testing is similar to chip testing in the semiconductors industry, MEMS devices present further challenges because mechanical, chemical and optical parameters must be tested in addition to electrical properties. MEMS foundries and even fabless MEMS companies need to ensure that they have in-house expertise in MEMS testing and reliability. This workshop will ensure that your organization stays current with the latest MEMS testing and reliability trends and therefore decrease waste while increasing yields and profitability.

The workshop will include a luncheon presentation by **Dr. Leslie Field**, Founder and Managing Member of **SmallTech Consulting** on *Packaging of BioMEMS*.

Go to www.meptec.org for complete program details and pricing.

## MEPTEC & Advanced Packaging Magazine Present

TECHNICAL SYMPOSIUM & ONE-DAY EXHIBITS

**Celebrating MEPTEC's 30th Anniversary**

# **Packaging Developments** and Innovations

From System Design to Integrated Delivery

November 13, 2008 Wyndham Hotel • San Jose, California

DIAMOND SPONSOR

PAC TECH USA

PLATINUM SPONSOR

Henkel

**GOLD SPONSOR**

### Sessions will include:

Advanced Packages and Processes

- Packaging to Board Assembly Trends

- **Design Tools and Co-Design Solutions**

**Microelectronics Substrate Fabrication** and Assembly Innovations

SILVER SPONSORS Gel-Pak

#### REGISTER ONLINE TODAY ΑT WWW.MEPTEC.ORG

MEDIA SPONSORS

TEME

NVESTOR

## Made Industry Analysis

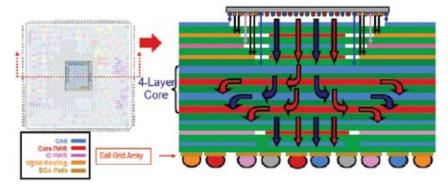

## **3-DTSV Interconnects**

The Next Revolution for Semiconductor Packaging & Circuit Assembly Industries

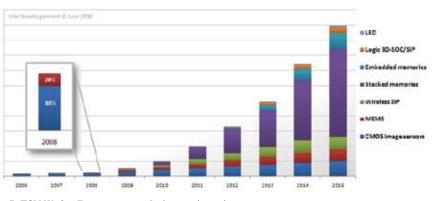

Market Research Company Yole Développement has unveiled its latest market forecasts evaluating the impact of 3D-TSV technologies on Semiconductor business both at the Device, Equipment and Material levels

he Semiconductor manufacturing industry is today facing more than ever the challenge to explore the so-called "More-than-Moore" 3-D integration route in order to pursue the continued aggressive scaling of the historical Moore's Law. The whole Semiconductor industry supply chain is concerned, from IDMs to Fabless and CMOS foundries, from OSATs to Substrate and Circuit Assembly players as well. We believe 3D integration with TSVs could accelerate even more current consolidation happening in CMOS wafer fabs and the shift toward a fabless foundry model. As the whole industry supply chain is being affected, all players are at the moment positioning on the technology and evaluating about which 3-D technology platforms need to be invested in and developed for their own business.

Times are bright for packagers from all across the world. A whole new infrastructure needs to be developed in the "Midend" of the semiconductor industry supply chain. New Technologies, Equipments and Advanced Materials coming both from the Front-end and the Back-end worlds are being developed and will give rise to a new revival of the semiconductor packaging and circuit assembly industries. Our latest market forecasts show that 3D-TSV wafers will be shipped in millions and have the potential to impact as much as 25% of the memory business by 2015. If we exclude memories, our analysis show that 3D-TSV wafers could account for more than 6% of the total semiconductor industry by 2015.

This new study aims at giving a better understanding about the right timeline for the successful adoption of the Through Silicon Via (3-D TSV interconnect) technology across the wide range of its driving end-applications. The two reports further quantify the potential impact of 3-D technologies on the semiconductor manufacturing market (at the Device / Equipment / Material levels) and evaluating how the industry supply chain is likely to evolve in the 2009-2015 time frames. Examples of major finding from this new market research study are:

3D-TSV Wafer Forecasts per Industry (wspy).

• Motivations for going to 3-D are pretty clear and have not changed much since the technology was successfully introduced into production for MEMS and CMOS image sensors: it is all about achieving smaller form factor with increased package densities to meet bandwidth, RF, power consumption performance improvements and further cost reduction. Cost is definitively set to be the strongest motivation to develop 3D technologies in the long run. Additionally, we do see several players being driven by reliability motivations: higher reliability systems can be manufactured through the vertical integration of several layers using 3-D TSVs instead of wire-bonds or flip-chip interconnects, using 3D stacked wafer level optics instead of plastic injection molded lens modules. From many points of view, 3-D appears to be a strong enabling driver for the successful introduction of ever more integrated new systems into harsh and space constraint application environments such as in the Automotive, Bio, Telecom and Consumer markets among others.

• Roadmap per application: WL-CSP CMOS image sensors are on the point to leave their traditional edge interconnects configuration for going to "real" 3D-TSV architectures as soon as this year. Vias will be partially or completely filled, depending on via filling approach being developed (Copper for partial filling, Poly-Silicon or Tungsten for completely filled vias). Addi-

tionally, we clearly see the number of I/Os expanding to several hundreds of interconnects per chip with a trend to stack the DSP chips under the image sensor chip itself. MEMS will also benefit from 3-D in order to combine the MEMS with its ASIC while Wireless SiPs will combine heterogeneous layers all together (built on different lithography nodes, different material substrates such as Si, GaAs, SiGe...). The market for 3-D stacked memories is imminent: it is primarily driven by RAM based memories first; meanwhile, more and more flash memory is set to be combined in the future within MCP, PoP/SiP packages, cell-phone card-slots and SSDs. The question is now more about who will succeed first in developing the lowest cost process and who will take the risk of the huge initial infrastructure investment required. Going further, logic based 3D-SOCs are to set to take off in 2-3 years for different applications. Indeed, this "true" type of 3D-IC integration will be achieved through the progressive segregation of several layers: 3D partitioning of embedded memories, RF, analog and I/Os layers from the logic base chip will be achieved in the most cost effective manner by reducing overall chip size areas. We are confident that 3D-ICs will soon prove to be more cost effective compared to traditional SOC approaches, as it will enable to partition in a cost effective manner the different functions that today are all integrated into large area SOC dies. Beyond cost, these 3-D chips will additionally ben-

## Maine Industry Analysis

Yole Developpement © June 2008

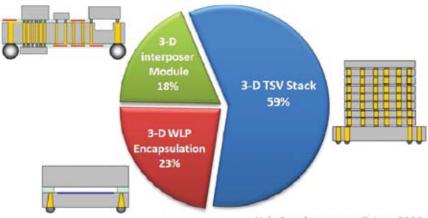

#### 2013 Forecast – Breakdown per 3D-TSV Technology Platform.

efit from performance improvements as interconnect length will be shortened and repeaters will be removed. This will allow the CMOS industry to "virtually" go beyond the 32nm node in terms of chip size, cost and performance.

• We believe that different 3-D technology platforms need to be developed as they will serve different application needs and will correspond to different players in the supply chain:

- 3-D WLP encapsulation platform is already in production today in CMOS image sensors with via through the backside of the wafer. It will expand to power amplifier modules as well. MEMS packages are more complex as most of these applications will need a full-hermetic cavity through the use of getters and more specialized bonding technologies.

-3-D TSV stack platform is being primarily developed for stacked memories and logic 3D-SOCs later on. If via-last will account for a large portion of the market, we see a clear trend towards via-first configura-

tions and smaller vias size approaching  $1-5\mu$ m diameters with 500-2000 interconnects per chip typically.

- 3-D interposer module platform is already in very small production for several MEMS applications in order to combine the ASIC & MEMS chips together in a true WLP approach (the silicon interposer acts here in direct replacement of the organic substrate). This technology platform is likely to expand rapidly into many SiP application spaces. In most cases, the silicon 3D interposer is used as a "companion chip" module for the 3D integrated system. Benefits of such 3-D silicon interposers include outstanding intrinsic thermal properties (CTE) of the silicon package/substrate/board and the potential to scale to unlimited interconnect pitches. Furthermore, they leverage the possibility to be more and more "engineered" among time with the capability to integrate passive devices, to form cavities or even to build micro-cooling channels for cost efficient thermal management modules. More generally, 3-D silicon interposers must be low cost and may be handled or manufactured by the IDM's subcon-

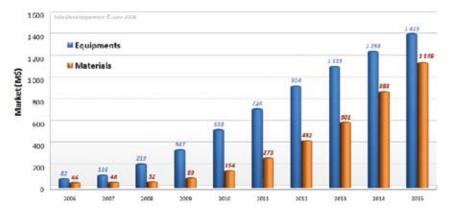

3D-TSV Equipment & Materials Forecasts (M\$).

6 MEPTEC Report / Q3 2008

tractors if the confidentiality value chain can be ensured. We do see totally different players emerging in this business, from MEMS, CMOS silicon foundries, substrate to circuit assembly players.

#### • There are several barriers to entry for full scale 3D IC integration. It includes test, 3D EDA design tools, thermal management and 300mm equipment availability.

Regarding test, issues are close to being solved as many solutions are currently being developed and evaluated (double-side probe stations, BIST with JTAG, interconnect redundancies...) However, as contact probe test technologies will tend to be more and more limited with via pads density increasing, they may not scale to future pad dimensions pitch shrinks. Moreover, as one portion of the industry is going towards W2W configurations with thin wafers, new requirements are emerging for testing without damage at the wafer level to ensure the electrical functionality of the TSV, RDL and bump pad structures prior to the stacking of each layer. As a consequence of this, many companies are requesting contact-less testing technologies (based on optical or wireless methods). Technology and equipment are being developed for wafer surface inspection, open/shorts electrical testing and 3-D system level functionality validation. The landscape is completely different regarding the availability of 3D EDA design and thermal management software tools. We are seeing a lot of effort being done in this area at the moment. However, we believe it is a real challenge for the industry to get the tools ready by 2011.

The availability for 300mm 3D-TSV equipment is just a question of time. First 300mm tools clusters have been shipped this year for production pilot-lines. Our latest analysis shows that the equipment market for 3D-TSV manufacturing tools will rapidly expand above 1B\$ by 2013. 3D-TSV equipment forecasts have been realized over the 2006-2015 time period both in units and in M\$. They include shipments and sales forecasts for Wafer Bonders / Chip Bonders / Etching-Drilling / Plating / Lithography / Deposition-Coating / Temporary Bonding / Grinding-Thinning / Inspection & Metrology / Test tools. Meanwhile, the 3D-TSV Market for advanced materials is forecasted to break the 1B\$ volume by 2015. Our analysis includes sales in volume and in M\$ for Advanced Photo-resists / Adhesives / Gas / Advanced Substrates and Specific Chemistries.

For more information on this new market study, please contact David Jourdan, Yole Développement at jourdan@yole.

### October 2, 2008 | Santa Clara Convention Center

The GSA Suppliers Expo & Conference is the semiconductor industry's must-attend event. The 2008 program is highlighting "Global: Markets, Perspectives, Technology," and will feature more than 100 exhibiting companies and a full day of educational programming. Join 2,000 attendees at this conference which provides you with the opportunity to meet with potential partners and hear from industry experts regarding the topics most relevant to today's semiconductor industry.

The 2008 program will feature the following:

#### PLATINUM SPONSORS

|                                         | 9 a.m 6 p.m.      | 2008 GSA Suppliers Expo - Show Floor Open                                                                                                                                                                                                                                                                                   |

|-----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \infty Chartered                        | 9 a.m 10 a.m.     | GSA Annual Briefing                                                                                                                                                                                                                                                                                                         |

| t                                       | 10 a.m 11 a.m.    | Keynote Address<br>Joep van Beurden,<br>Chief Executive Officer, CSR                                                                                                                                                                                                                                                        |

|                                         | 11 a.m 11:15 a.m. | Networking & Refreshment Break on Show Floor                                                                                                                                                                                                                                                                                |

| UMC                                     | 11:15 a.m 12 p.m. | Panel Discussion: Challenges in, and Solutions for, Design and Verification of Low Power Devices                                                                                                                                                                                                                            |

|                                         |                   | Moderator: Herb Reiter, President, eda 2 asic Consulting                                                                                                                                                                                                                                                                    |

| GOLD SPONSORS                           |                   | Panelists: <b>Albert Chen</b> , Field Application and Marketing Manager,<br>Faraday Technology Corporation; <b>Joseph Greco</b> , Vice President,<br>VLSI Engineering, NVIDIA; <b>Don Kurelich</b> , Technical Director<br>Americas Sales, Mentor Graphics; <b>Richard Owen</b> , Group Director,<br>Cadence Design Systems |

|                                         | 12 p.m 2 p.m.     | Lunch Served on Show Floor                                                                                                                                                                                                                                                                                                  |

| SAP                                     | 2 p.m 3 p.m.      | Keynote Address: 'Diversity and Dynamics' – Global Semiconductor<br>Eco-system From a Design Services Perspective                                                                                                                                                                                                           |

| <b>()</b>                               |                   | <b>Sudip Nandy</b> , President of the Technology,<br>Media and Telecom (TMT) Strategic Business Unit,<br>Wipro Technologies                                                                                                                                                                                                 |

|                                         | 3 p.m 4:15 p.m.   | Networking & Refreshment Break on Show Floor                                                                                                                                                                                                                                                                                |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 4:15 p.m 5 p.m.   | Panel Discussion: IP: How to Successfully Use and Integrate IP                                                                                                                                                                                                                                                              |

| MEDIA SPONSORS                          |                   | Moderator: <b>Bill Martin</b> , General Manager- Verification IP Division,<br>Mentor Graphics                                                                                                                                                                                                                               |

|                                         |                   | Panelists: <b>Dermot Barry</b> , Vice President Consumer Silicon, Silicon<br>& Software Systems Ltd.; <b>Ron Burns</b> , General Manager,<br>Semiconductor and Systems Solutions, Wipro Technologies; <b>Jeff</b><br><b>Lewis</b> , Vice President, Marketing and Product Operations,                                       |

| PennWell®                               |                   | Innovative Silicon Inc.                                                                                                                                                                                                                                                                                                     |

|                                         | 5 p.m 6 p.m.      | Cocktail Networking Reception                                                                                                                                                                                                                                                                                               |

|                                         |                   |                                                                                                                                                                                                                                                                                                                             |

### Booth space available at gsaglobal.org/expoO8

## **MEDIC:** University News University of Colorado – *i* MINT Center

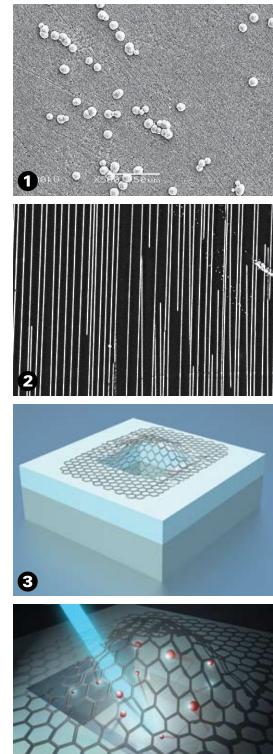

he research accomplishments of the DARPA Center on Nanoscale Science and Technology for Integrated Micro/Nano-Electromechanical Transducers (iMINT), in its short history of less than two years, are impressive. Under the guidance of Center Director, Dr. Y. C. Lee, and DARPA Program Manager, Dr. Dennis Polla, the *i*MINT Center draws on resources from a number of contributing entities: the University of Colorado-Boulder, Columbia University, the University of Texas-Austin, and Northwestern University; industry sponsors General Electric Global Research, Ibiden USA, Lockheed Martin, Ricoh Innovation, and wiSpry; and the National Institute for Standards and Technologies (NIST). Researchers at this research center, based at the University of Colorado at Boulder, have established nanowire (NW) spectroscopy as a vital tool to design defect-free/strain-free Galium Nitride NW laser components, light emitting diodes, and detectors. iMINT researchers are the only ones in the US who can grow defect-free GaN nanowires on silicon substrates. They have demonstrated the feasibility of a mass sensor with an atto-gram resolution operating at room temperature by using a defect-free GaN nanowire-based resonator with a quality factor Q greater than 35,000 at 2MHz. And they have demonstrated five times enhancement of the mechanical robustness of atomic layer deposition-based barrier coatings.

The potential outcomes based on these findings are even more impressive – the stuff of science fiction. Material so strong that it would take the weight of a two-ton car to puncture a sheet merely as thick as ordinary plastic food wrap. A card, as thin as a credit card, with the thermal conductivity 100 times better than copper. Skeptics of these futuristic claims sarcastically say, "Right, and I'd like to sell you an interest in a perpetual motion machine."

The first description above is of a sheet of graphene, tested by Jim Hone's DARPA iMINT group at Columbia University. Results of their study have recently been published in Science. Graphene proves to be the strongest material ever measured. Hone's research required the development of atomic force microscope (AFM) tips that were durable enough to apply force capable of breaking graphene sheets. The second description is of the flexible thermal ground plane, subject of a research project headed by *i*MINT Center director Y.C. Lee at CU-Boulder. This single project under the guise of Program Manager Dr. Tom Kenny is generously funded by DARPA (the Defense Advanced Research Projects Agency). "Flexible thermal ground planes have 100 times better thermal conductivity than copper and will enable a new generation of high-performance, integrated microelectronic, photonic, or microwave systems operating at high power density without constraints resulting from complex thermal management solutions," according to Lee.

These groundbreaking discoveries and initiatives are the results of fundamental research performed by researchers at the *i*MINT Center, headquartered at CU-Boulder. One of eleven DARPA Nano- & Micro ElectroMechanical Systems Science & Technology Fundamentals Centers, the *i*MINT Center is on the cutting edge of fundamental and advanced research in nano- and microsystems, nanotubes, nanowires, and graphene. Fundamental research in engineering and applied science is the mechanism by which investigating, finding out, discovering, and knowing can change the possibilities of what can be created. And advanced research turns the possibilities into reality, no longer the stuff of science fiction.

Military and commercial applications will increasingly benefit from the use of microelectromechanical systems (MEMS), especially when anticipated significant improvements in performance are realized via the integration of microelectromechanical systems with novel nanoelectromechanical systems (NEMS). Dr. Lee relates these potential advancements to his role as director of the center and as a professor of Mechanical Engineering: "Nanotechnology is the technology driver in the 21st century. Students must know more about how to integrate nano devices with micro devices. At the *i*MINT Center, students engage in such integration issues with hands-on, cutting-edge research experiences."

The Center draws researchers from a range of backgrounds in order to perform research that integrates micro and nano technologies. Graduate Research Assistant and National Science Foundation Graduate Research Fellow, Joe Brown, came to the CU *i*MINT Center from private industry. The company he worked for in New Hampshire manufactures carbon nanotubes for use in macroscale materials, using bulk quantities of nanotubes in actual electrical and mechanical applications. For example, they are developing macroscale nanotube wires that are at least as strong and conductive as copper, but at greatly reduced mass. Brown says, "Here at the University of Colorado, I'm designing microscale tools that enable nanotechnology research and development." Research into nanotechnologies is not only aimed at making things small. "In order to access the behaviors in nanoscale devices, attention has to be paid at every level to scale from the nano to the micro and from the micro to the macro. Nanoscale engineering requires designing at a range of size scales, not just the smallest scales." Brown's research aims to help other researchers to integrate nanomaterials into active devices. It's no longer a world of the single inventor. In the current active research environment, the new knowledge discovered and reported by one researcher is applied to new designs and new inventions by others. Collaborators within the *i*MINT Center plan to use Brown's microdevices for optomechanical and electromechanical characterization of nanofibers, with the intent of using this knowledge in development of new sensors and other devices.

Brown says, "I'm working with individual materials – one tube or one wire." What he sees himself doing is "expanding the toolkit of what you can design with at the sub-micron scale and how things can be made at that scale." Why is this kind of research important? "If something is small that means it's cheap, and if it's cheap it can be everywhere. Whether it's a tool to build nanoscale devices

or a smaller microchip for a smoke detector, smaller things consume fewer resources, by reducing material consumption and energy consumption, leading to more efficient use of resources to meet the needs of real people."

Graduate Research Assistant Yadong Zhang's research also contributes to building an effective toolkit. Zhang, who worked in the semiconductor industry in China before coming to CU-Boulder, is developing defect visualization techniques to be applied to nanoscale barrier coatings. He has developed techniques using electroplating decoration and fluorescent tagging to quickly test the quality and reliability of barrier coatings. His approaches to inspecting surfaces test defect size and defect density and lead to higher quality, nearly defect-free coatings. "This is the nanoscale characterization technique to help researchers know the quality of their nanoscale coatings." As an example of useful nanoscale coating techniques, atomic layer deposition (ALD) is known for growing densely-packed, virtually pinhole-free conformal coatings. Now, ALD's contribution to the study of nanotechnologies and barrier coatings is obvious. Y.C. Lee has pointed out that the knowledge derived from using Zhang's approach to evaluating the quality of ALD barrier coatings on the Thermal Ground Plane project has led the ALD researchers to a 6000 times improvement in the quality of the hermetic sealing capabilities of their coatings. Zhang's tests show researchers, he says, "There is a crack; there is a defect. Good area - bad area. It's obvious." By virtue of this knowledge, they know which ALD coating techniques are better and which substrates provide better platforms for instance. Before using Zhang's defect visualization technique, it had been hit and miss. Speaking of the quality of ALD coatings, Zhang says, "If you want to improve it, you have to know what the quality is - what's the defect source? Where is the defect? How was it generated?" Knowing this, researchers can work towards improving the quality and reliability of their coatings. Something that makes his research important is that it saves time and increases the reliability and repeatability of the research findings.

"It's important to have a variety of defect visualization techniques," Zhang says. His fluorescent tagging approach is applicable to ALD coatings of polymer substrates. In applying this aspect of Zhang's techniques, iMINT researchers from Mechanical Engineering and from CU's Department of Chemistry have teamed up with industry researchers from Invitrogen. Invitrogen contributes to the collaboration their fluorescent tag, having already been in general use in biotechnology, in hopes of finding new applications of their product. Zhang's electroplating decoration technique applies to ALD nanoscale coatings of conductive substrates, such as those necessary for several research projects going on at the *i*MINT Center. On this project, University of Colorado researchers from the departments of Chemistry and Mechanical Engineering are teaming up with long-time industrial partner Lockheed Martin.

Prospects for more research breakthroughs are plentiful. Unprecedentedly, four members of the CU Department of Mechanical Engineering won DARPA MTO Young Faculty Awards in 2008 – Wei Tan for her Highly Selective, Stable and Manufacturable Nano-Bio-Sensor research, Harold Park for his research into Novel Multiscale CAE Tools for Surface-Dominated NEMS, Ronggui Yang for Surface-Plasmon Enabled High Efficiency Thermoelectric Devices, and in-coming CU faculty member Scott Bunch for his Graphene Membrane research.

Dr. Bunch is the newest member of CU's Mechanical Engineering faculty, fresh from his doctoral studies in physics and short post-doctoral assignment at Cornell University where his research focused on graphene. "Basically, we made the world's thinnest balloon." Lots of graphene research has focused on the material's electrical properties, but, like Jim Hone at Columbia, Bunch's efforts have focused on graphene's mechanical properties. The carbon-carbon bonds like those of diamonds make graphene, single layers of graphite, incredibly stiff and absolutely fascinating to researchers. Making a balloon from graphene tells us that it is impermeable and opens up the study of its mechanical properties, such as its elastic modulus and its breaking strength. "You can push on graphene membranes with an AFM tip or you can inflate these membranes to make graphene balloons. In both cases, you apply controlled forces that allow you to learn about the mechanical properties of this remarkable material. The two techniques complement each other.'

"Now, we're going to poke holes in it, basically pop the balloons, see what goes through them." Bunch asserts that with graphene having the best thermal and electrical conductivity and the best mechanical properties of any substance ever tested, there have to be some important applications. Directions for future research include finding methods of fabrication for these yet undiscovered applications.

The foundations for further advanced research are firmly in place. The potential for turning more science fiction into science fact grows with each *i*MINT Center project. Researchers at the Center have also earned a DARPA MTO seed grant for a study to demonstrate the feasibility of a novel GaN NW-based light emitting diode with extremely high efficiency and low thermal resistance. Based on the findings from the first two years of research at the Center and the possibilities that will grow from those findings, we can say that the future burns brightly. For more information visit http://imintcenter.org/. ◆

Defect morphology of ALD alumina on a copper substrate demonstrated using electroplating decoration.

"Mechanical channel cracks" on ALD alumina on a polymer substrate visualized using fluorescent tags.

Graphene membrane schematic.

4 - Zoom in of graphene membrane schematic.

**FRONICS ASSEMBLY TECHNOLOGIES**

**PROMEX** INDUSTRIES INC.

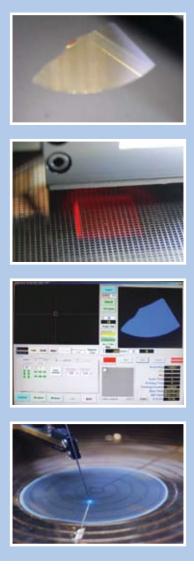

romex Industries has been a Silicon Valley microelectronics manufacturing services provider for over thirty years. Originally focused upon providing engineering build prototyping services to the local Silicon Valley community, Promex has outgrown those humble beginnings to become a full service IC Assembly & Custom Chip Packaging Foundry serving a world-wide customer base.

What makes Promex unique is its ability to enable their customers to take new products to market faster than by any other route. Promex has an impressive skill set of technical capabilities that gives their customers "one-stop shopping" for traditional chip assembly or custom IC packaging design, development and assembly.

For those customers that Promex is able to serve, Promex will "go the extra mile" and leave "no stone unturned" to help these customers take products to market quickly.

#### IC Assembly Services, Custom Package Development & Assembly

Promex's customer base includes the major multi-national semiconductor companies, fab-less semiconductor houses, high tech start-ups and emerging high tech companies. This growing customer base is attracted by their ability to leverage Promex's resources for a rapid, cost effective new product launch coupled with agile, scalable production. End-use markets include both commercial and military electronics as well as, RF, bio-tech, bio-metric, PV solar and optoelectronics products.

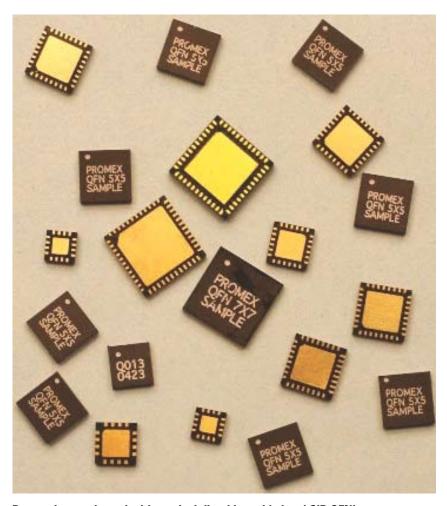

Promex is seeing rapidly growing demand for MEMS & MOEMS packaging and has pioneered stacked die and thin molded modules, especially over molded QFN configurations.

The company provides IC assembly in open cavity plastic or ceramic packages, sealed ceramic packages and over-molded plastic with less than 24 hour quick turns or stepped premium deliveries of one, two or three days. No-premium standard lead time is 4 to 5 working days. On-shore pre-Asia volume production of various lead frame based packages as well as custom package and module assembly are readily available.

#### Much More Than Quick Turns

"Several U.S. based companies provide quick turn IC assembly services which are certainly a key area of our business." states Richard Otte, CEO and President of Promex Industries since 1995, "However... we consider our materials expertise a distinctive core competency. Promex extends itself further to the many customers seeking materials-centric custom package development coupled with follow-on production. We offer these customers a reliable partner with the depth to develop and process engineer custom packages for high first pass yield

#### Promex is located in the heart of Silicon Valley.

**PROMEX** INDUSTRIES INC.

in production. We have capacity to scale from initial prototypes through medium production volume. This applies to traditional IC assembly as well as the more complex custom packages utilizing mixed process and material sets such as are found in SiPs and MEMs products."

#### **Responsive On Shore Assembly**

Otte further remarks "We have noticed two recent trends in the IC Assembly and Packaging market. First, some Asian assemblers appear to have imposed higher minimum order volumes over the past few years.

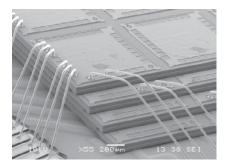

Promex is experienced with stacked die, thin-molded and SiP QFN's.

### State of the art wire bonding for QFN lead frame based packages.

As a result, some companies, especially small firms and startups that do not have high volume needs, are having difficulties finding a reliable production partner in Asia to meet their needs. Secondly, the true total cost of doing business with Asia is being recognized by non-Asian companies. The hidden costs such as freight, increased inventory carrying cost, engineering support, communications difficulties etc, have CFO's concerned. For stable commercial high volume, it usually makes sense to produce offshore, but there exists a volume range, we've coined the term "pre-Asia volume" that many companies need fulfilled, but cannot find an offshore assembly partner willing to provide the needed service. That's where Promex comes in. We act as a bridge

2,200 sq ft of Class 1000 engineered clean room.

to help our customers cross the volume chasm."

#### **Broad Technical Capabilities**

After touring the Santa Clara, California facility, it is easy to understand how Promex's broad capabilities are attractive to their growing customer base.

A 2,200 square feet, Class 1000 engineered clean room supports wafer sawing, die attach, wire bonding (Au ball, Au wedge, Al wedge, controlled loop Au ribbon for RF applications, copper wire), wafer handling, flip chip and custom package assembly. All wire bonders are fully automatic and several are dedicated for high reliability wire bonding on various lead frames. Wire bond pitches to 35 microns are possible.

A plastic molding operation provides precision over-molding of the many lead frame based plastic packages as well as Promex's rapidly expanding line of QFN and DFN packages. X-ray and laser marking capabilities both reside in-house.

Two SMT (pcba) lines, including a hands-free line optimized for RoHS compliant lead free assembly, offers precision SMT assembly of highly panelized boards as well as SiP (system-in-package) and COB (Chipon-Board) assembly support. Components as small as 01005 are automatically and reliably placed on FR-4, Rogers material, flex or custom substrates.

#### **IC Assembly in Plastic Packages**

Promex provides leaded plastic over molded packages as well as the increasingly in demand line of QFN/ DFN's. Eutectic solder or epoxy die attach are standard. Assembly options include Commercial and MIL-STD-883. All plastic packages are either ink stamp marked or in-house laser marked if package serialization is requested. A listing of available leaded packages is shown in Table 1.

| Promex Open Tooled QFN & DFN<br>Over Molded Packages |              |              |               |                        |  |  |

|------------------------------------------------------|--------------|--------------|---------------|------------------------|--|--|

| Size<br>(mm)                                         | DFN<br>Leads | QFN<br>Leads | Lead<br>Pitch | Thickness<br>(nom. mm) |  |  |

| 2 x 2                                                | 6, 8         |              | 0.50          | 0.9                    |  |  |

| 3 x 3                                                |              | 8            | 0.65          | 0.9                    |  |  |

| 3 x 3                                                | 8, 10        | 12, 16       | 0.50          | 0.9                    |  |  |

| 3 x 3                                                |              | 20           | 0.40          | 0.9                    |  |  |

| 4 x 3                                                | 12           |              | 0.50          | 0.9                    |  |  |

| 4 x 4                                                |              | 16           | 0.65          | 0.9                    |  |  |

| 4 x 4                                                |              | 20, 24       | 0.50          | 0.9                    |  |  |

| 5 x 5                                                |              | 20           | 0.65          | 0.9                    |  |  |

| 5 x 5                                                |              | 28, 32       | 0.50          | 0.9                    |  |  |

| 6 x 6                                                |              | 40           | 0.50          | 0.9                    |  |  |

| 7 x 7                                                |              | 48           | 0.50          | 0.9                    |  |  |

| 7 x 7                                                |              | 56           | 0.40          | 0.9                    |  |  |

| 8 x 8                                                |              | 52, 56       | 0.50          | 0.9                    |  |  |

| 9 x 9                                                |              | 64           | 0.50          | 0.9                    |  |  |

| 12x12                                                |              | 100          | 0.40          | 0.9                    |  |  |

#### Table 1.

#### JEDEC Standard, Custom and SiP QFN's

The number of new QFN package sizes supplied by Promex increases monthly. All QFN and DFN over molded plastic packages conform to either JEDEC MO-220 or MO-229. Nickel palladium gold lead frame finish is standard. Promex's QFN and DFN packages are certified RoHS compliant. All QFN and DFN packages are saw singulated. Table 2 shows current open tooled plastic over molded QFN/ DFN package offerings. Check with Promex for new QFN package introductions.

| Promex Open Tooled Plastic Over Molded Packages |                          |           |        |  |  |  |  |

|-------------------------------------------------|--------------------------|-----------|--------|--|--|--|--|

| Package                                         | Lead Count               | Body Size | Solder |  |  |  |  |

| SOIC                                            | 8, 16 (heat sink option) | 0.150″    | Plate  |  |  |  |  |

|                                                 | 14                       | 0.150″    | Plate  |  |  |  |  |

|                                                 | 16, 20, 24, 28           | 0.300″    | Coat   |  |  |  |  |

| QSOP                                            | 16 (heat sink option)    | 0.150″    | Plate  |  |  |  |  |

| SSOP                                            | 30                       | .3 mm     | Plate  |  |  |  |  |

| MSOP                                            | 8, 10                    | 3.0 mm    | Plate  |  |  |  |  |

| TSSOP                                           | <b>TSSOP</b> 8, 20, 28   |           | Plate  |  |  |  |  |

| PDIP                                            | 14, 16, 18, 20, 24, 28   | 0.300″    | Coat   |  |  |  |  |

|                                                 | 24, 28, 40               |           | Coat   |  |  |  |  |

## Made Member Company Profile

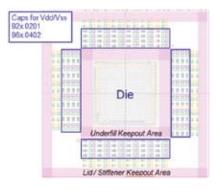

While the demand for quick turn evaluation and characterization assembly builds using JEDEC QFN standard packages is strong, Promex is seeing an increasing market demand for custom OFN packages with irregular dimensions, non-standard footprints or deviations from the 0.9 mm +/- 0.1mm JEDEC standard height. Many emerging MEMS and RF applications must duplicate an existing footprint on a circuit board. The QFN concept is a flexible and cost effective method of designing and developing a custom plastic over molded package. A single or multiple package configuration is designed on a standard lead frame template, which fits a common mold. After die attach, wire bonding and over molding, the individual packages are saw singulated. This method eliminates expensive new molding tools for each unique package configuration. New JEDEC standard or custom QFN/ DFN packages may be quickly adapted by Promex with assembled first articles shipped within a maximum of 4 to 5 weeks.

The company has been assembling stacked die MEMS devices in custom QFN's for the past 18 months and builds thin molded custom QFN packages with an overall height as low as 0.454 mm.

In addition to MEMS packaging, Promex is experiencing a strong market demand for system-in-package (SiP) QFN assembly utilizing single, side-by-side and stacked die. Many customers see a need to place more than just the traditional single IC on the die attach pad and are searching for ways to save cost and space by integrating resistors, capacitors and often other semiconductor chips within an over-molded lead frame based QFN package.

"There is particularly strong demand for QFN SiP's in RF applications" comments Dr. Edward Binkley, the Chief Technology Officer of Promex. "The QFN packaging concept can offer better parasitics and thermal management than traditional leaded packages while also providing added design flexibility to save space and ultimately cost. Our in-house, integrated SMT capability allows us to provide a continuous process flow for over molded QFN and other custom SiP's. Promex does not need to out source the SMT portion of SiP assembly to this week's low cost bidder. Continuous process control is particularly important with Military customers, not to mention any customer concerned about limiting the exposure of their IP to third parties. We believe we have a distinct advantage with continuous process flow for SiP assembly".

#### Materials Centric Custom Package Development and Assembly

In addition to lead frame based QFN SiP's, Promex designs, develops and pro-

IC assembly using ceramic packages.

### Fully automated lead free SMT optimized for SiP's and COB.

cess engineers a wide variety of custom packages and modules including 2-D, 3-D, Flip Chip and SMT SiP's on various substrates including flex.

Land Grid Arrays (LGA), Multi-chip modules (MCM) and custom Flip Chip packages are developed utilizing Promex's core competencies and materials expertise focused upon providing high first pass production yield. The materials-centric custom packaging approach can dramatically enhance new product introduction by optimizing first article approval as well as the follow on development cycle.

"Materials-centric packaging combines material and volume process knowledge." says Binkley. "The complexity of electronic modules and custom packages are increasing dramatically while their size is shrinking. The drivers of RoHS compliance and miniaturization result in a need for higher processing temperatures, more complex assembly steps as well as a higher attention to thermal issues for the finished package. Reliable high yield production assembly processes are in-separately linked to packaging materials synergies."

#### **Quality Through Process Control**

Promex is ISO 9001:2000 certified by the British Standards Institute and utilizes Statistical Process Control (SPC) in all facets of assembly operations. Operator certification, detailed ISO and assembly documentation are coupled with the adopted "5S" philosophy to provide customers with the highest level of reliable, repeatable quality.

Quality control charts are readily visible in the Operations area and monitor key assembly and machine settings. Process metrics, statistical trends and CpK values are integral components that drive process control and Quality Assurance within Promex's Total Quality culture.

A 3-D solder paste measurement system and on line x-ray are routinely used to verify first article set-up and ongoing process control during product assembly.

Clean room particle counts and relative humidity are monitored as well as wire bond pull strengths and molding parameters for each and every job.

#### Silicon Valley's Packaging Foundry

Silicon Valley based innovations have changed the way we live our daily lives, the way we work, communicate and do business.

Several decades later, and for the foreseeable future, Silicon Valley remains the center of global technology innovation. Promex Industries' location in the heart of Silicon Valley means the company is exposed to, and must support, much of the emerging IC assembly and custom packaging requirements that emanate from this innovative part of the world.

It's those same Silicon Valley based business and communication innovations that allow customers from various parts of the country and the world to easily connect with Promex for their IC assembly and custom packaging needs. Reliable new product introductions, engineering and developmental prototypes, materials-centric packaging and "pre-Asia" on shore volume production are equally attractive to high tech companies world wide, not just innovative Silicon Valley companies. Promex is a vital part of the packaging infrastructure that enables customers to take new products to market faster than by any other route.

The future looks bright for the IC assembly and materials-centric packaging world of Promex Industries... Silicon Valley's Packaging Foundry.

For more information about Promex Industries, Silicon Valley's Packaging Foundry, visit www.promex-ind.com or email Chris Pugh, VP Sales & Marketing at pughc@promex-ind.com. Calls are welcome at 408-496-0222. ◆ The event of the year for buyers, specifiers and producers of chip-scale and wafer-level packaging equipment, materials and services will be presented in San Jose from Oct. 13-16, 2008.

# RESERVE THOSE DATES FOR THE FIFTH ANNUAL INTERNATIONAL WAFER-LEVEL PACKAGING CONFERENCE

If your business involves using or producing chip-scale packages, wafer-level packages or any form of advanced semiconductor packaging, you should attend the International Wafer-Level Packaging Conference in October. Sign-up today to attend!

THE GOLD STANDARD WORLDWIDE IN SEMICONDUCTOR PACKAGING EVENTS!

SCHEDULED EVENTS Co-presented by

Oct. 13-14Professional WorkshopsOct. 15Keynote Dinner with<br/>Dr. Thomas H. Di Stefano,<br/>Centipede SystemsOct. 15-16Tabletop Exhibits, Technical<br/>Presentations (two tracks),<br/>Special Panels and Poster Sessions

### **IWLPC TOPICS**

WLP Materials • 3D and Stacked Die Manufacturing Processes • MEMS Flip-Chip Bumping • Photoresists Polymers for WLP • Electroplating CSP/MoP/PoP/PiP/SiP/SoP Screen Printing • Wire Bonding Thermal Management • UBM • Testing

Visit www.iwlpc.org or e-mail melissa@smta.org for more information.

If your business involves developing, marketing or selling any equipment, materials or services used by the people who use advanced semiconductor packaging, you should be exhibiting at the International Wafer-Level Packaging Conference. Sign-up today to exhibit on Oct. 15-16!

### Wafer-level packaging and much, much more!

| Platinum Sponsor | Platinum Sponsor                | Gold Sponsor | Gold Sponsor                                         | Gold Sponsor | Gold Sponsor | Silver Sponsor                                                                 | Book Sponsor | Coffee Sponsors              |

|------------------|---------------------------------|--------------|------------------------------------------------------|--------------|--------------|--------------------------------------------------------------------------------|--------------|------------------------------|

| Technology®      | Umicore<br>Electronic Materials | CORPORATION: | MINITZ LEVIN<br>Mezi Lon-Gare Paus Garea con Pres PC | PAG TECH USA | TESSERA'     | phoenix  x-ray<br>Part of the t leading is<br>Reporting Technologies Isochemis | DUMMIES      | PACIFIC GATE<br>TECHNOLOGIES |

## Maine Industry News

### Indium Announces Promotions

CLINTON, NY – Indium Corporation recently announced the promotion of three individuals - all based at Indium's headquarters in Clinton, NY.

**Eric Bastow** has been promoted to Senior Technical Support Engineer. In his new role, Eric is responsible for supporting customer inquiries and traveling to customer sites to provide a higher level of product support in customer related projects. Eric joined Indium Corporation in 2001, where he started as a Lab Technician in Research and Development.

Mario Scalzo has been promoted to Senior Technical Support Engineer. Mario is responsible for supporting Indium's product lines and for advanced SMT problem solving, as well as special assignments involving key customerrelated projects, product education, and process training of new employees. Mario joined Indium Corporation in 2000. He served, most recently, as a Technical Support Engineer supporting the North America and Asia regions.

Tom Pearson has been promoted to the position of Inside Sales Manager for Indium's Solder Products, Global Processes. Tom is responsible for managing the inside sales process across the Americas, Europe, and Asia. His focus is on small business, resource management, quality improvement, and sales of all solder products. Tom has worked at Indium Corporation for 24 years, serving most recently as Market Manager for Small Accounts.

For more information about Indium visit www.indium.com.

### APM Reaches Alliance Agreement with UMC

HSINCHU - APM has announced that it has reached an alliance agreement with leading global semiconductor foundry UMC for 8-inch MEMS wafer fab capacity. As part of this agreement, UMC and APM will collaborate to support current and future customers for the 8inch MEMS process. UMC will provide the fab manufacturing, logistic management and any required capacity expansion. APM will bring its MEMS process technologies based on its development and manufacturing expertise dating back to 2001.

The joint APM-UMC MEMS team has been working together during the last 18 months for this development. An 8-inch MEMS prototype line has been set up in one of UMC's fabs and will soon begin process qualification on one product. Dr. Kurt Petersen, an industry pioneer and a member of APM's Technical Advisory Board, says: "The 8-inch migration path is key to the MEMS industry as it brings MEMS into the main stream CMOS lines, which offer many benefits from engineering innovation to cost. This is the tipping point for MEMS products to reach the consumer electronics marketplace at affordable prices".

APM is one of the world's leading independent MEMS foundry service providers. It is currently running 6-inch MEMS wafer processes in its twenty seven thousand square feet facility at Hsinchu Science Park of Taiwan. APM serves many global customers who are designing state-of-art MEMS sensors and actuators, such as pressure sensors, inkjet heads, inertia sensors, microphones, RF relay and optical mirror actuators.

Kurt Petersen is one of the founders of SiTime. Prior to SiTime, he was co-founder, President, and CTO at Cepheid. Prior to Cepheid, he was a cofounder and VP of Technology at NovaSensor for over 10 years. Kurt was listed by Red Herring Magazine as a Top 10 Innovators of the Year. He is a member of the National Academy of Engineering and a recipient of the 2001 IEEE Simon Ramo medal.

### STMicroelectronics, STATS ChipPAC and Infineon to Set New Milestone in Establishing Wafer-Level-Packaging Industry Standard

GENEVA, SWITZERLAND, SINGAPORE and NEUBIB-ERG, GERMANY – STMicroelectronics, STATS ChipPAC, and Infineon Technologies AG have announced that they have signed an agreement to jointly develop the next-generation of embedded Wafer-Level Ball Grid Array (eWLB) technology, based on Infineon's firstgeneration technology, for use in manufacturing future-generation semiconductor packages.

ST and Infineon, two of the world's leading semiconductor makers, have joined forces with STATS ChipPAC, a leader in advanced three dimensional (3D) packaging solutions, to fully exploit the potential of Infineon's existing eWLB packaging technology, which has been licensed by Infineon to ST and STATS ChipPAC. The new R&D effort, for which the resulting IP will be owned by the three companies, will focus on using both sides of a reconstituted wafer to provide solutions for semiconductor devices with a higher integration level and a greater number of contact elements. The eWLB technology uses a combination of traditional 'front-end' and 'back-end' semiconductor manufacturing techniques with parallel processing of all the chips on the wafer, leading to reduced manufacturing costs. This together with the increased level of integration of the silicon's overall protective package, in addition to a dramatically higher number of external contacts, means the technology can provide significant cost and size benefits for makers of cutting-edge wireless and consumer products.

ST's decision to work with Infineon to jointly develop and use this innovative technology, with its greater integration level of package size, marks an important milestone for eWLB on its way to becoming an industry standard for cost-efficient and highly integrated wafer-level packages. ST plans to use the technology in several products of its ST-NXP Wireless joint venture and in other application markets, with first samples expected by the end of 2008 and production by early 2010.

### Hesse & Knipps to Introduce Wire Bonder for Solar Market

SAN JOSE, CA – Hesse & Knipps has announced that it

will soon introduce a new wire bonder dedicated to the needs of the solar market in producing CPV (concentrated photovoltaic) cells.

The new BondJet 820 CPV will offer all of the advanced features of the company's Bondjet BJ 820 wedge bonder, in addition to an extended table travel of 900mm x 350mm and expanded X axis travel via the use of intelligent automation.

The BONDJET BJ820 platform is an industry benchmark for wire bonding, offering the fastest wiring speed, largest work area and greatest axis accuracy available.

"The bonding speed and flexibility of the 820 platform, coupled with the extended bonding area, will lend itself very well to the CPV marketplace as well as other markets requiring such extended travels," states Joseph S. Bubel, president of Hesse & Knipps, Inc.

For more information call +1-408-436-9300, email info@ hesse-knipps.us, or visit www. hesse-knipps.com.

### SUSS MicroTec Announces CB Wafer Bonders Series for Advanced MEMS

WATERBURY, CT – SUSS MicroTec has announced the CB Series, semi- and fullyautomated wafer bonders, for Advanced MEMS devices for the automotive and consumer markets.

There are a variety of wafer level bonding methods for MEMS fabrication processes like anodic and glass frit, with the most commonly used in Advanced MEMS being eutectic, fusion, and metal diffusion bonding.

The most challenging wafer level encapsulation and integration needs for MEMS are met by the newly released CB series wafer bonders designed for metal bonding applications that require high temperature and high force. CB technology features bond force to 90kN and temperatures to 600°C along with precision temperature and pressure control for unrivaled process uniformity. These features enable significant die size and cost reduction for MEMS devices.

To meet the demanding alignment needs of advanced MEMS manufacturing SUSS MicroTec is releasing the BA200 Gen2, a high-precision alignment system, to complement the CB series.

For a smooth transition from the lab or low-volume production to full production recipes developed on the CB8, semi-automated wafer bonder, can easily be transferred to the CBC200, multi-chamber cluster tools.

### STATS ChipPAC Offers Innovative USB Module for NAND Flash Memory Applications

SINGAPORE & UNITED STATES – STATS ChipPAC Ltd. has announced an innovative USB (Universal Serial Bus) module for NAND flash memory applications.

STATS ChipPAC's new USB flash drive design utilizes System-in-Package (SiP) and three dimensional (3D) die stacking technology to integrate NAND flash memory die, controller and passives onto a single packaging substrate for a cost-effective module solution. The USB module has the flexibility to accommodate multiple die configurations and can be customized for each customer or end application. Integrating all of the key components of a USB flash drive into a single package saves considerable space and allows for more effective signal routing at a lower overall cost.

In a typical design for a USB drive, the NAND flash memory die and controller are packaged in Thin Small Outline Package (TSOP), Quad Flat Pack (QFP) or Ball Grid Array (BGA) packages. These packages may contain stacked dies, depending on the memoSurface mounted device with delamination (red) along the entire length of several leads. This part would fail per J-STD-020 criteria.

## SonoLab" is Your Lab

SonoLab, a division of Sonoscan<sup>®</sup>, is the world's largest inspection service specializing in Acoustic Micro Imaging (AMI). Through SonoLab, you'll have access to the superior image quality and reliable data accuracy of Sonoscan C-SAM<sup>®</sup> acoustic microscopes, plus the capabilities and careful analysis of the world's leading AMI experts.

With worldwide locations, unmatched capabilities, extensive experience and the best equipment available, SonoLab gives you the ability, flexibility and capacity you need to meet all your AMI requirements.

#### SonoLab<sup>™</sup> Services

- Component Qualification to Industry Standards

- Materials Characterization and Evaluation

- High-Capacity Screening and Lot Reclamation

- Failure Analysis and Constructional Analysis

- Inspection and Audit Services

- Custom Training

To learn more visit www.sonoscan.com/sonolab

800-950-2638 • 847-437-6400 • www.sonoscan.com Santa Clara, CA • Scottsdale, AZ • Elk Grove Village, IL • Burlington, MA North America • Europe • Asia

## MELLE Industry News

ry density requirements of the end application. The discrete NAND flash memory and controller along with passives are then mounted onto a printed circuit board (PCB) using surface mount technology. This normally consumes most of the usable area allowed by the form factor of the USB flash drive.

The innovative USB module design is the latest addition to the Company's portfolio of solutions for removable solid-state storage applications. STATS ChipPAC offers a variety of memory card formats which utilize the most up-todate technologies and processes unique to memory cards, including integrated curve-cutting, labeling, mechanical card assembly and card packaging. In addition to assembly, STATS ChipPAC offers memory card test services with dedicated resources to support test development.

With global headquarters in Singapore, STATS Chip-PAC has design, research and development, manufacturing or customer support offices in 10 different countries. STATS ChipPAC is listed on the SGX-ST.

Further information is available at www.statschippac.com.

### Pac Tech USA **Announces Grand Opening Celebration** for New Asian **Facility**

SANTA CLARA, CA - Pac Tech Packaging Technologies held a grand opening celebration on September 18 at its new 55,000 square foot facility in Penang, Malaysia. In conjunction with the opening celebrations, Pac Tech held a technical symposium on September 19 at the Equatorial Hotel in Penang. The facility is located at 11900 Bayan Lepas, Byan Lepas Industrial Zone, Penang, Malaysia. Government offi-

cials, dignitaries and industry leaders were in attendance.

The new facility provides state-of-the-art wafer bumping and backend processing for semiconductor companies within the Pacific Rim. The building has 40,000 square feet of remodeled production floor space, including cleanroom area. Both are equipped with the latest generation equipment for 300mm wafers.

The new Malaysian facility

is designed and laid-out to accommodate mass-production, and is capable of handling up to 600,000 wafers per year.

Pac Tech Asia will provide a variety of special applications designed to enhance and support the Asian semiconductor manufacturing community. The applications supported will include: electroless Ni/Au under-bump metallization for copper and aluminum devices, solder-paste stencil print-

1217 WILDWOOD AVENUE • SUNNYVALE, CA 94089

www.meptec.org

ing for flip-chips, solder-ball placement for wafer-level CSPs down to  $200\mu$ m ball diameters, and micro solder-ball placement for fine-pitch applications down to  $80\mu$ m. More advanced applications include: Ni/Pd/Au metalization for today's power MOSFET devices and gold wire bonding, tall Ni/Au bumping for RFID applications. The facility offers up to 300mm wafer processing capability. The facility is now accepting process qualification orders. Semiconductor companies can begin to provide Pac Tech GmbH and Pac Tech USA with their wafer forecasts in order to begin allocation of time and schedule them into the production planning. Pac Tech GmbH and Pac Tech USA can also be contacted to begin the pre-qualification of processes to be used in the new Asian facility.

Dr. Thorsten Teutsch, President of Pac Tech USA and Vice President of Operations for Pac Tech Asia, comments, "The new facility in Malaysia establishes our global presence. It will also help Pac Tech USA address new customers and increase our domestic business as an entry portal for highvolume customers to our Asian facility."

More information is available at www.pactech.com.

### Hesse & Knipps Presents Most Flexible and Fastest Wedge Bonder for Both Ribbon and Wire Bonding

SAN JOSE, CA – Hesse & Knipps, leading manufacturer of high-speed, fine pitch wedge bonders for the back-end semiconductor industry, introduced the BONDJET BJ820 during Semicon West'08. The BOND-JET BJ820 is a high-speed, fully automatic wedge bonder that offers the ultimate in flexi-

bility for both high-speed round wire and deep access ribbon and wire bonding. It handles all challenging fine pitch wire bonding applications in a single platform - including RF and microwave devices, COB, MCM and hybrids, fiber optics and automotive - using aluminum or gold wire or ribbon. The fastest wedge bonder on the market, BONDJET BJ820 offers bond speeds up to 7 wires/second.

With axis repeatability of  $1\mu m$  at a balanced encoder resolution of 20nm, the BOND-JET BJ820 provides increased process stability that enables reliable bonding of extremely small bond pads with a larger wire diameter. A highly versatile 12" x 16.1" work area can serve as two or more smaller stations for efficient handling of smaller products or substrates. Coupled with intelligent automation solutions, parallel bond stations in one work area can eliminate significant indexing time, resulting in 60% greater throughput than competing machines.

Other significant machine capabilities include:

- 12.5µm to 85µm diameter wire bonding

- Ribbon bonding from  $6\mu m x$  $35\mu m$  to  $25\mu m x 250\mu m$

- Constant loop height and wire length

- Maintains parallel loops with

10987 Via Frontera • San Diego, CA 92127 • 858-674-4676 • Fax 858-674-4681 a division of Delphon

## **3-D Architectures for Semiconductor** Integration and Packaging

### **Examining Routes to Success**

Premier Sponsors

Media Sponsor

**Event Sponsor**

In Association With

Coordinated by

### For more information or to register, visit: http://techventure.rti.org

**Participating Companies** • Alcatel Micromachining • Alchimer • Allvia • Amkor • Aviza Technology • Brewer Sciences • CEA Leti • EV Group • Freescale Semiconductor • IBM • IMEC • Intel • Lam Research • Microelectonic Consultants of NC • Micron Technology • NEXX Systems • Qualcomm • R3Logic • RTI International • SEMATECH • Semitool • siXis • Surface Technology Systems • SUSS MicroTec • Synopsys • TechSearch International • Tezzaron Semiconductor • Tohoku University • TSMC • Yole Développement • Xilinx • XSiL • Ziptronix • ZyCube

## Maine Industry News

in mixed reference system

• Auto teach for linear applications, reducing programming time

"The BONDJET BJ820 defines the benchmark in the industry by offering the fastest wiring speed, largest work area and greatest axis accuracy among its competition," summarizes Bubel.

With a footprint of only 720 x 1250mm, the BONDJET BJ820 can be easily integrated into existing floor plan configurations or new concepts.

For more information on the BONDJET BJ820, email info@ hesse-knipps.us or visit www. hesse-knipps.com.

### Rudolph Technologies Announces Orders for WaferWoRx 300 Probing Process Analysis Systems

ISSAQUAH, WA – Rudolph Technologies, Inc. has announced the receipt of orders from a major European semiconductor manufacturer for two WaferWoRx<sup>®</sup> 300 Probing Process Analysis Systems. The orders were placed as part of a multi-tool agreement signed in June 2008.

The WaferWoRx 300 System allows semiconductor manufacturers to make informed decisions based on quantifiable data about their wafer probing process in order to increase yields and reduce operating costs.

Rudolph's Probe Card Test and Analysis product manager, Darren James, stated, "We are continually seeking opportunities to reduce the cost and complexity of wafer probing and other final test processes. With today's multi-site, multiple test probe processes, determining the root cause of yield loss is a challenge for our customers. The WaferWoRx generates analyses that helps pin-point the most likely source of probing process problems."

The WaferWoRx 300 is a probing process analysis system that uncovers potential process