## Volume 14, Number 1 Volume 14, Number 1 Volume 14, Number 1 Volume 14, Number 1

A Publication of The MicroElectronics Packaging & Test Engineering Council

**INDUSTRY NEWS**

Asia Pacific Microsystems, Inc. has announced that it has shipped over 2 million MEMS pressure sensor elements to a leading global automotive electronic company. *page 12*

A multidisciplinary research team at the **Nationasl Institute of Standards and Technol-ogy (NIST)** has found that an organic semiconductor may be a viable candidate for creating large-area electronics, such as solar cells and displays that can be sprayed onto a surface as easily as paint. *page 12*

**Synopsys, Inc.** and the Belgian nanoelectronics research center, **imec**, have announced that they have entered into a collaboration to use Synopsys TCAD (Technology Computer-Aided Design) finite-element method tools for characterizing and optimizing the reliability and electrical performance of through-silicon vias (TSVs). *page 13*

**Sonoscan** has publicly announced Sonoscan Critical Evaluation<sup>Trackarrow</sup> (SCE), a confidential service that acoustically inspects critical electronic components. *page 14*

ECTC 2010 - The 60th Electronic Components and Technology Conference will be held June 1 - 4 at the Paris Las Vegas Hotel in Las Vegas, Nevada.  $page\ 20$

#### www.meptec.org

# 8th Annual PULL-OUT BROCHURE MEMS and IC System Integration: From Sensing to Awareness

A Special One Day Symposium and Exhibits Coming to San Jose, CA May 20th

#### **MEMBER COMPANY PROFILE**

In 2009 **Honeywell Electronic Materials** announced a new material that improves the efficiency and power output of photovoltaic (PV) panels. The new product, called Honeywell SOLARC<sup>m</sup>, is a transparent coating material that improves the light transmittance through the glass that covers PV panels, thus increasing the PV module efficiency and power output. This coating also significantly reduces glare from the glass, allowing the PV panels to better blend with their surroundings. *page 6*

s one of the most diversified technology and manufacturing leaders, Honeywell International

SEE

serves customers worldwide with aerospace products and services; control technologies for buildings, homes and industry; automotive products; turbochargers; and specialty materials.

Semiconductor equipment billings increase 423.3% over March 2009 level. *page 14*

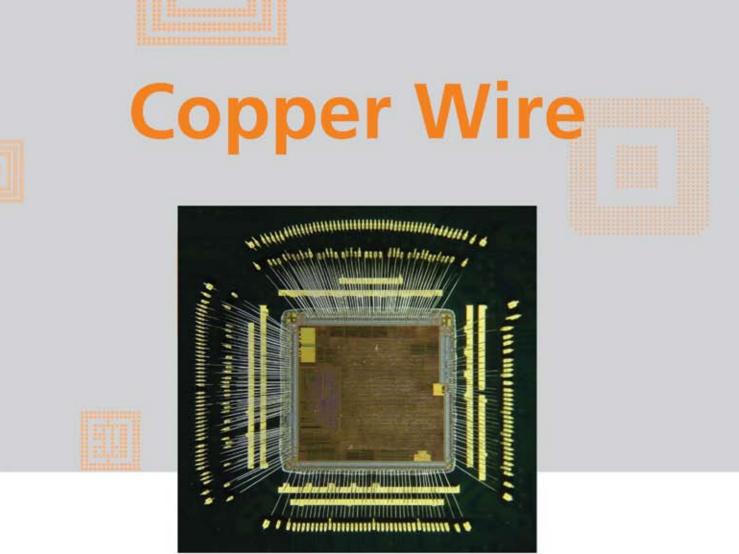

Copper Wire is a lower cost alternative to the traditional gold wire used in semiconductor packaging. Offering clear advantages, copper wire bonding is gaining popularity for products at 25 microns and below, where the majority of wire bond applications lie. ASE's copper wire bonding initiative is geared towards this group of applications. Bonding pad composition and wafer structure are major factors for copper wire evaluation, and ASE is customizing products based in specific customer needs.

© 2010 ASE Group. All rights reserved.

Volume 14, Number 1 A Publication of The MicroElectronics Packaging & Test Engineering Council

P. O. Box 222 Medicine Park, OK 73557 Tel: (650) 714-1570 Email: info@meptec.org

> Published By MEPCOM

Editor Bette Cooper

Design and Production Gary Brown

> Sales Manager Gina Edwards

#### **MEPTEC Advisory Board**

Seth Alavi SunSil, Inc.

Jeffrey Braden SkyCross, Inc.

Philippe Briot

Joel Camarda GTronix

Gary Catlin Plexus

Tom Clifford

Rob Cole

John Crane J. H. Crane & Associates

Jeffrey C. Demmin Tessera

> Bruce Euzent Altera Corporation

> > Skip Fehr

Anna Gualtieri Elle Technology

Bance Hom Consultech International, Inc

Ron Jones N-Able Group International

Nick Leonardi Premier Semiconductor Services

> Phil Marcoux PPM Associates

Mary Olsson Gary Smith EDA

Marc Papageorge Semiconductor Outsourcing Solutions

> Mike Pinelis MEMS Investor Journal

> > Rich Rice ASE (US) Inc.

Dr. Michael Todd Henkel Corporation

> Jim Walker Gartner Dataquest

Russ Winslow Six Sigma

MEPTEC Report Vol. 14, No. 1. Published quarterly by MEPCOM, P. O. Box 222, Medicine Park, OK 73557. Copyright 2010 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact Gina Edwards at 408-858-5493, Fax Toll Free 1-866-424-0130.

www.meptec.org

elcome to our Spring 2010 issue! Our first event of 2010 was *"From Chip to System: Design Challenges and Solutions"* and was held on February 25 at the Holiday Inn in San Jose. The event explored co-design solutions – bridging the gap from silicon to system, ensuring quality and reliability in the design process, disruptive design solutions, and navigating the design IP minefield. CD's of the proceedings are available; visit www.meptec.org to order.

Our next event will be the 8th Annual MEMS Technology Symposium, MEMS and IC System Integration: From Sensing to Awareness. This symposium will cover the many integration technologies that have emerged over the last few years, each with its strengths and weaknesses. The keynote presentation will be Philippe Kahn, CEO and Founder of Fullpower Technologies, speaking on "Accelerometrics: The Art of Motion Sensing...Because Motion is Life". Kahn is a technology visionary and creator of the first complete camera-phone solution. He has received numerous technology and business awards including the 2002 International Imaging Association (I3A) Leadership Award and in 1995 was selected as one of Byte Magazine's twenty most important people in the history of the computer industry. You will find a pull out brochure for this symposium in this issue. Details and registration are available on www.meptec.org.

Our Industry Analysis this issue is by MEPTEC member Jan Vardaman of TechSearch International, Inc. In *"Semiconductor Packaging Expands in the Third Dimension"*, Jan explains that there are numerous approaches to 3D packaging, including SiP, PoP, PiP, CoC, etc. She shows that the adoption of 3D through TSV offers the best in 3D integration. Go to page 4 for this informative piece.

Our Company Profile comes from long-time MEPTEC member **Honeywell Electronic Materials**. Honeywell International is a diversified technology and manufacturing leader, with products that are ubiquitous in our everyday lives: planes, cars, heating and cooling our homes, medication dispensing, and many more. Honeywell's Electronics Materials division is a global leader in the semiconductor materials industry, and serves many sectors of technology. See their story on page 6.

One of our feature articles this issue is from long-time Corporate MEPTEC member company **ASE (US) Inc.** on "Advanced QFN Package for Low Cost Solutions". The article describes ASE's aQFN package, which is an enhanced version of a conventional QFN and is a good solution for electrical components of portable communication devices. See page 9 for details.

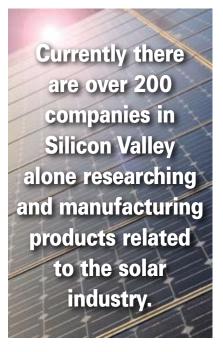

Our editorial in this issue is by MEPTEC Advisory Board member **Seth Alavi** of **SunSil, Inc.** Seth wrote this piece as a follow up to our Q4-09 event, *"Semiconductor to Solar: Growth Opportunities for the IC Industry"*. Seth talks about a "technology renaissance" that has occurred over the last 50 years. He suggests that the next wave of technology for our industry just might lie in the solar/PV areana – see page 22 for this interesting piece.

We'd like to thank all of our contributors for making this a great issue. If you're reading our publication for the first time, or if you're a new member, we hope you enjoy it.

Thanks for joining us!

#### MEPTEC signs MOU with ASTSA

The Asia Semiconductor Trading Support Association (ASTSA) and MEPTEC have signed an MOU (strategic partnership). The ceremony took place at the 9th Annual Microelectronics and Advanced Packaging (MAP) International Workshop which was held in Fukuoka on November 13, 2009. Founded in October 2006, ASTSA has signed MOUs with a number of semiconductorrelated organizations in several different Asian countries since its inception; however, this was the first time that MEPTEC, an organization with a long history of more than 30 years, has entered into an MOU with another semiconductor industry organization. Mr. Joseph Fjelstad, who represented MEPTEC at the signing ceremony commented on the value of the relationship between MEPTEC and Asia after the signing and implied the possibility of global expansion. Mr Fjelstad noted that: "More than 91% of 278 corporate members of MEPTEC are presently located in the US. Although MEPTEC has until now largely operated in the US providing technical forums and information to its members, MEPTEC hopes and plans to actively increase the number of its members in Asia, which is clearly leading production in the semiconductor packaging industry."

## METEC Industry Analysis

## Semiconductor Packaging Expands in The Third Dimension

#### E. Jan Vardaman, President TechSearch International, Inc.

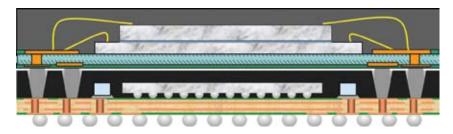

here are many approaches to 3D packaging. These include versions of system-in-package (SiP) such as stacked die, stacked packages - package-on-package (PoP), package-in-package (PiP), and chip-on-chip (CoC) – in production today as well as versions being discussed for the future such as system-on-package (SOP), 3D fan-out wafer level packages, and vertical side interconnection techniques. While these packaging methods provide many benefits, the adoption of 3D through silicon via (TSV) technology offers the ultimate in 3D integration. Table 1 shows the advantages of various technologies.

#### **Stacked Die**

Applications for stacked die are typically portable products such as mobile phones, digital cameras, and music players but are also increasingly found in medical, industrial, and aerospace applications. Memory products with stacked die include solid-state drives (SSDs), microSD cards, and USB memory sticks. The die for these applications are typically less than 100  $\mu$ m, with some companies reportedly with 25 $\mu$ m die thickness in R&D for microSD cards. The highest die stacks in production are reported to be up to 17 (memory die plus a controller) for microSD cards from both Samsung and Toshiba.

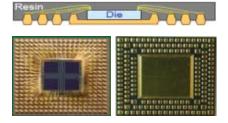

Stacked die CSPs are ideal for applications requiring multiple die in a small space, whether driven by form factor requirements or the need for maximum memory capacity. Two or more die are assembled into a stack that is then overmolded into a single, standard laminate CSP package. Typically most of these die are wire bonded, but some stacks contain flip chip die on the bottom. These packages ship in high volume, with more than 2.5 billion stacked die CSPs estimated to have been shipped in 2009. While most of these packages contain only two die, stacked die CSPs with nine or more die are in production. Figure 1 shows ASE's aQFN.

#### PoP

Package-on-package offers a different business model from stacked die, in that

| Table 1. | Advantages of | Various Package | Configurations. |

|----------|---------------|-----------------|-----------------|

|----------|---------------|-----------------|-----------------|

|                          | Die Stack                          | Side by Side                                         | PoP                                                     | TSV  |  |

|--------------------------|------------------------------------|------------------------------------------------------|---------------------------------------------------------|------|--|

| Advantage                | Small,<br>high-density<br>circuits | Extremely<br>reliable<br>High thermal<br>dissipation | Variable<br>memory volume<br>Memory shrink<br>supported |      |  |

| Smaller,<br>high density | Excellent                          | Fair                                                 | Good                                                    |      |  |

| Thermal resistance       | Good                               | Excellent                                            | Good                                                    |      |  |

| Reliability              | Excellent                          | Excellent                                            | Good                                                    |      |  |

| Cost                     | Good                               | Good Fair Fair                                       |                                                         | Fair |  |

Source: TechSearch International, Inc. adapted from Renesas Technology Corporation.

Figure 1. A stacked die in ASE's aQFN package.

Source: ASE.

the memory die which are typically housed in the top package can be separately tested and burned in, if necessary, before they are committed to the stack. Logistics are simpler when the memory can be sourced in a standard package and assembled to the bottom package, and this approach also gives the flexibility to use different types of memory, depending on the application.

The primary applications for PoP continue to be logic plus memory stacks for smartphones, but the technology is also popular in digital cameras, MP3 players, and other multimedia applications. Demand for PoP is driven by integration and miniaturization, business and logistics advantages, and the requirements for standard and efficient interfaces for the high-speed bus between the processor and memory. Amkor leads in production volumes of PoPs. Amkor's bottom, highdensity package that enables PoP stacks has been one of the fastest growing new products in Amkor's history<sup>1</sup>, and has indicated that it is the fastest growing unit volume packages in the company's history. TechSearch International estimates that more than 220 million PoPs shipped in 2009 and the volumes will continue to grow.

One disadvantage of the PoP compared to the stacked die CSP is height. Substrate thickness and ball pitch/diameter are key factors governing package height. There has been considerable work in both areas, resulting in lower profile packages. In addition some companies have developed new packages. For example, through molded via (TMV<sup>TM</sup>) is a new bottom PoP technology developed by Amkor (see Figure 2). TMV<sup>TM</sup> is a matrix-molded package with solder-filled openings for the stacked interface to the top PoP. TMV<sup>™</sup> offers improved warpage control, which allows the bottom PoP to be thinner, and it appears to be ideally suited to 0.5mm and 0.4mm interface pitch requirements in emerging JEDEC low power DDR2 (LP DDR2) specifications.<sup>2</sup>

Other companies, including CMK and Dia Nippon Printing have developed bottom package substrates with embedded components that offer a lower profile PoP. While these are not in production yet, several companies including Renesas show the technology on their roadmaps.

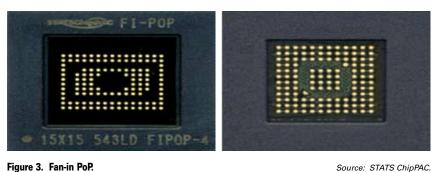

Fan-in PoP also addresses constraints associated with the peripheral connections between the top and bottom PoP packages, including large package size and warpage. Instead of peripheral connections, fan-in PoP provides a full array of connection points directly above the bottom silicon by using an interposer substrate on the top side of the bottom package. Advantages of fan-in PoP include a potentially smaller package footprint with less warpage, and a larger die/package ratio.3 STATS Chip-PAC has developed a fan-in PoP, and the Kyushu Institute of Technology has developed a similar solution known as the Dual Face Package. Samsung has developed a fan-in package with blind vias onto the silicon in the bottom PoP. Figure 3 shows a fan-in PoP.

#### PiP

Package-in-package is an intermediate solution. It is similar to a stacked die package, except that one of the stacked devices is a memory package - essentially a very thin LGA – that is pre-tested before being assembled and molded into the package. The PiP is also similar to stacked die in that it offers a thin, standard package for board assembly, but it has lower risk than stacked die because the memory package is tested and is only used if it is good. PiP is found in portable products such as mobile phones and digital cameras. The volumes for PiPs are in the tens of millions of units.

#### CoC

Chip-on-chip (CoC) is the first step in moving to 3D at the wafer level. In this technology the chips are thinned and faceto-face bonded without TSVs. Researchers at AT&T Bell Labs proposed one of the first concepts.<sup>4</sup> Infineon announced a CoC interconnection in 2005 when it introduced the Cu/Sn diffusion solder process called SLID. The first prototype application was for a smart card and included the integration of a memory and a controller, but it was not commercialized. In 2005, Sony introduced a microcontroller and memory CoC for the PlayStation. One of

Figure 2. Through Mold Via (TMV<sup>™</sup>) is a new bottom PoP technology developed by Amkor.

Figure 3. Fan-in PoP.

the drivers for the adoption was that Sony was unable to find a way to make the die cheaper by scaling embedded DRAM process technology from 90nm to 65nm. Sony noted that even with the adoption of a single chip DRAM and logic, each with a different manufacturing process, it would take a long time to obtain acceptable yield levels.5

#### **TSV: The Ultimate in 3D**

Many companies have commented that 3D ICs designed with TSV are the only option. Increased bandwidth is achieved because more data can be passed between the chips. The shorter interconnects enable faster data transfer. Lower power I/O signaling between the stacked die is also achieved because the signals do not have to be driven through packages and boards. Data transfer between stacked die is possible with short vertical interconnect lines that act as on-chip transmission lines and there is less loss and noise, therefore simple, low power drivers and receivers can be used for signaling. 3D integration also provides smaller form factor for systems by creating the option of building in the vertical direction.6

Applications for 3D TSV with stacked die include a variety of memory and logic combinations. The timing for mass production for 3D TSV technology depends on several factors. Clearly, there is demand for 3D TSVs, the infrastructure must be ready and how the TSV compares in terms of cost with existing technologies is critical. In many cases, this means wire bonded die stacking. While performance is a driver, cost is a limiting factor. While

many DRAM makers have shipped samples of stacked memory with TSVs, the first commercial application for DRAM with TSVs is not expected until 2012, assuming reliability requirements can be met and current technologies are not able to meet the performance needs with lower cost. While many companies in the wireless application space would like to adopt a TSV solution today, the earliest adoption for volume production is expected to be 2012 when foundries have production lines fully qualified.7

As companies move from R&D into production the difficult work begins in addressing the issues of design, thermal management, test, and assembly. Different needs and economic factors determine the timing of adoption in each application. Issues in moving to volume production include the installation and qualification of high-volume 300mm production lines, assembly and test capability, the availability of TSV interposers, and reliability data. As the major issues are resolved, the ultimate in 3D packaging will be achieved.◆

- 'Amkor PoPs Cork for Fast Growing Package on Package Solution" Press Release April 18, 2007.

- M. Dreiza, "Package-on-Package IMAPS Webinar," Jan 2009. F. Carson, "Advancements in 3D IC Packaging", Semicon

- Japan, December 2008.

- Y. Los, R. Frye, and K. O'Connor, "Design Methodology for Chip-on-Chip Applications," IEEE Transactions CPMT, Part B, Volume 21, 1998, p. 298.

- M. Uno, "Chip-on-Chip Offers Higher Memory Capacity, Speed," Nikkei Electronics Asia, February 2007, pp. 28-32.

- M. Shapiro, et al., "Reliable Through Silicon Vias for 3D Silicon Applications," International Interconnect Technology Conference, June 1-3, 2009, pp. 63-66

E. J. Vardaman and P. Garrou, "3D Through Silicon Via: Infrastructure and Markets," TechSearch International, Inc., January 2010.

## METEC Member Company Profile

## Honeywell Electronic materials

**Honeywell International** is a diversified technology and manufacturing leader, serving customers worldwide with aerospace products and services; control technologies for buildings, homes and industry; automotive products; turbochargers; and specialty materials.

Whether you're flying on a plane, driving a car, heating or cooling a home, furnishing an apartment, taking medication or playing a sport, Honeywell products touch most peoples' lives everyday. Honeywell's brand promise commits to "...building a world that's safer and more secure ... more comfortable and energy efficient ... more innovative and productive."

#### **Damper Flapper**

Honeywell can trace its roots back to 1885, when an inventor named Albert Butz patented the furnace regulator and alarm. He formed the Butz Thermo-Electric Regulator Co., Minneapolis, on April 23, 1886, and a few weeks later invented a simple, yet ingenious device that he called the "damper flapper," a predecessor to the modern day thermostat that many people associate with Honeywell. In fact, the company introduced the T-86 "Round" thermostat in 1953, and it became one of the world's most recognizable designs; it remains in production today and adorns the walls of more households around the world than any other thermostat!

#### Honeywell "Round" Thermostat

Today, Honeywell employs over 120,000 people in more than 100 countries. It is a Fortune 100 company with sales of \$31B in 2009.

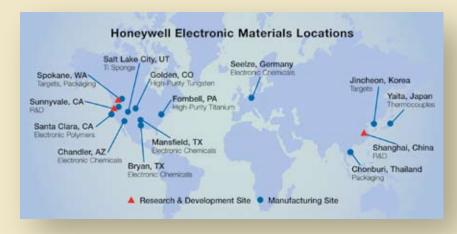

#### **Honeywell Electronic Materials**

A rich heritage of innovation and experience backs Honeywell Electronic Materials, a strategic business enterprise of Honeywell International. Honeywell is a global leader in the supply of critical materials to the semiconductor industry, enabling customers to develop innovative technologies and overcome manufacturing challenges. Honeywell's expertise in both chemistry and metallurgy and commitment to disciplined quality processes result in the development of superior technologies that are now being introduced to the adjacent markets such as photovoltaic, optoelectronic, LED and printable electronics. With global manufacturing and R&D locations, Honeywell is near to its customers and development partners.

Honeywell serves customers in the semiconductor, photovoltaic, LED, printable electronics and optoelectronics markets with product offerings including advanced electronic polymers, electronic chemicals, sputtering targets and coil sets, packaging solutions for thermal management and electrical interconnect, and precious metal thermocouples for temperature control.

#### A Focus on Thermal Management and Electrical Interconnect

As microprocessors become smaller and faster, heat dissipation and environmental requirements have emerged as major technology challenges in the supply of electrical interconnect materials. Honeywell Electronic Materials has established itself as a leading supplier of electrical and thermal interconnect products for semiconductor packaging.

Specifically, Honeywell supplies heat spreaders used in both desktop CPU and chipsets, thermal interface materials (TIM1.5 and TIM2) for computing and memory modules, and low alpha Pb and Pb-free soldering material for chip interconnection applications. Packaging materials expertise also includes the production of high purity evaporation charges, electroplating anode products used for under bumping and wafer bumping of flip chips and other electrical interconnection products such as Al wire, Boron Oxide, die attach wire, and pure metals.

**Semiconductor Packaging Materials**

#### **PCM45 Phase Change Materials**

Honeywell supplies a family of phase change materials that offer industry leading thermal management performance. Known as "PCM45," these phase change

**Honeywell PCM45 Phase Change Materials**

Honeywell Heat Spreaders and Mechanical Stiffeners

**Honeywell Electrical Interconnect Offerings**

materials are available in tape and roll as well as screen printable formats. They consist of a sophisticated thermally conductive material and maintain optimum filler size distribution to achieve maximum packing density compared to conventional phase change materials.

#### Heat Spreaders and Mechanical Stiffeners

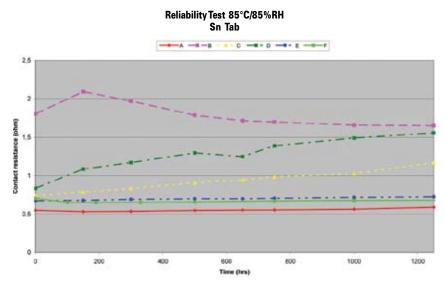

Honeywell Electronic Materials is a premier supplier of formed and finished components to the semiconductor industry for packaging applications. These components are used in multiple types of packages for thermal management, die protection and mechanical support. Metal finishing on packaging components can be tuned for performance on a wide variety of adhesives.

#### **Electrical Interconnect**

For electrical interconnect, Honeywell offers evaporation and electroplating materials for back and underbump metallization and wafer bumping of flipchip die, as well as low-alpha lead products for solder bumping and Pb-free high temperature die attach wire for high power devices and the automotive industry.

In 2009, the company introduced Honeywell Pb-free Die Attach Solder, a lead-free thermal interface material that effectively manages the tremendous heat produced by semiconductor chips in order to improve chip reliability.

Honeywell had been developing leadfree die attach solder alloys for many years to meet the industry's environmental requirements that emerged with the use of lead-free solder at the circuit board level. This new alloy will replace highlead alloys and provides better thermal management than other proposed lead-free thermal management alternatives such as polymer-based materials.

Demand for lead-free solders is growing, driven in part by regulation. Honeywell's new Pb-free Die Attach Solder is an advanced technology that meets these requirements, but is also cost effective. Lead-based solders are currently used for power/discrete die attach because they have a very good combination of melting temperature, wetting behavior, and mechanical properties. The new lead-free solder alloys are designed to meet these requirements, particularly resistance to melting during board level solder reflow.

The lead-free material is based on Honeywell's metallurgical expertise and long experience as a supplier of die-attach solders. Honeywell Pb-free Die Attach Solder is designed to be used mainly in wire form and compliments Honeywell's large diameter aluminum wire products.

#### **Adjacent Markets: A Bright Future**

Later in 2009, Honeywell Electronic Materials announced a new material that improves the efficiency and power output of photovoltaic (PV) panels. The new product, called Honeywell SOLARC<sup>TM</sup>, is a transparent coating material that improves the light transmittance through the glass that covers PV panels, thus increasing the PV module efficiency and power output. This coating also significantly reduces glare from the glass, allowing the PV panels to better blend with their surroundings.

"SOLARC has already demonstrated the highest efficiency of any anti-reflective (A/R) coatings commercially available today," said Dmitry Shashkov, marketing director for Honeywell Electronic Materials. "This is another example of Honeywell applying its materials expertise, developed from 50 years of innovation for the semiconductor industry, to meet the challenges of the PV industry."

Most commercially available PV panels today lose approximately 4 percent of their potential power output due to light reflection from the front surface of the cover glass. In addition to the decreased electricity generation, the glare from the reflection light is considered aesthetically undesirable, especially in residential rooftop installations.

SOLARC coating reduces reflection significantly, resulting in more light reaching the solar cell, which translates into higher electricity output. While use of such A/R coating is relatively low in the PV industry today, it is widely expected to become the industry norm over the next few years, according to the major PV manufacturers.

Honeywell's SOLARC, which is a liquid-based coating, can be used by all common types of PV modules. However, it provides the most benefits to rooftop installations, where space is limited

## **MEPTEC Member Company Profile**

and any increase in efficiency is critical. Because SOLARC coating reduces glare from the glass, it also contributes to a discreet, blend-in look of residential PV panels that has become very desirable to consumers installing the panels.

The coating is compatible with many coating processes, including spray, roller, curtain, slot-die and spin-on coating. Unlike other commercially available A/R coatings, Honeywell SOLARC does not require mixing of two components prior to deposition, and has at least a six month shelf life.

Demonstrating a 4 percent increase in transmission at 550 nanometers, Honeywell's SOLARC has demonstrated a very good response across a broad solar spectrum that is relevant for PV cell operation, from 350 nanometers through 1,100 nanometers. SOLARC coating has also demonstrated superior durability in a broad variety of accelerated tests designed to imitate harsh environmental conditions to which a PV panel is likely to be exposed during its lifetime.

Furthermore, environmental testing of SOLARC coating has shown that it provides additional protection to the glass, especially under hot and humid conditions that may lead to gradual glass deterioration. The coating has been further optimized to enable anti-soiling and self-cleaning functionality that prevents dust accumulation. This represents another valuable property of SOLARC, as solar panels lose on average 7 percent of their power output due to particulate contamination, according to the California Energy Commission.

Honeywell's SOLARC is based on proprietary technology and is validated by strong internal development processes and recognized industry test methods and laboratories.

The release of SOLARC coating further broadens Honeywell's portfolio of materials for the PV industry, which already includes backing sheet laminates, dopants, solar-grade electronic chemicals, and precision thermocouples.

Also in 2009, Honeywell announced that it developed a new thermal management material that improves energy efficiency of light emitting diodes (LEDs), which are increasingly being used in applications such as street lamps, automotive lighting, flat panel TV displays and computer monitors.

The new product, called Honeywell LTM6300-SP, is a thermal interface material that highly effectively transfers heat generated by LED lamps. As LEDs become smaller, faster and more powerful, more heat is being generated in a confined space, which can threaten to damage the LEDs' performance. If LEDs overheat,

**Photovoltaic Module**

they become dim, their color is muted and their lifespans are shortened.

Because LEDs are semiconductor devices, they require more precise heat management than traditional light sources. Honeywell's thermal management materials are designed to meet this specific challenge, helping to effectively transfer heat in semiconductor applications.

Honeywell is committed to energy efficiency technology, and this newly developed thermal management material, which enhances the performance of energy efficient LEDs, is the first in a series of Honeywell phase change materials being developed for the growing LED segment.

LTM6300-SP was designed for LED backlights for flat panel displays, but the packaging technology can be also be implemented in LEDs used in a wide range of industries, from automobiles to computers. Honeywell LTM6300-SP is a high-thermal-performance phase change material that is superior to silicone-based products, which typically pump out and degrade at high temperatures.

The lighting industry has evolved from incandescent bulbs toward more energyefficient options such as fluorescent bulbs and LEDs. Demand for LEDs is growing because they have several benefits over traditional light sources, such as lower energy consumption, longer lifespan, and smaller size. They also produce more light per watt than incandescent bulbs, are more durable and faster, and are mercury-free.

#### **LED Stoplights**

When used instead of traditional light sources, LEDs also reduce pollution and carbon footprint because they demand less power, which translates into energy savings that result in lower carbon dioxide and mercury emissions.

For more information on Honeywell Electronic Materials products and services, contact them at:

Phone: 509-252-2102 Fax: 509-252-8617 www.honeywell.com

### **MEDIC Packaging Technology**

## Advanced QFN Package for Low Cost Solution

#### Andy Tseng and Bernd Appelt, ASE (US), Inc.

Yi-Shao Lai, Mark Lin, Bruce Hu, JW Chen, Louie Huang and Sunny Lee Advanced Semiconductor Engineering, Inc. (Taiwan)

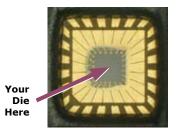

dvanced QFN (aQFN) is an enhanced version of QFN (Quad Flat No-Lead package) with multiple rows of terminals featuring higher number of I/O ports. The thermal and electrical performance of aQFN should is superior due to a smaller profile and shorter interconnects. Solder wettability control and board-level thermo mechanical reliability of aQFN is greatly enhanced over conventional QFN and similar types of lead frame packages because of the greater standoff of the aQFN Cu posts. aQFN provides similar I/O numbers as BGA-type chipscale packages (CSP) but at much less cost since the expensive substrate is replaced by a lead frame. aQFN turns out to be an ideal low cost solution for electrical components for portable telecommunication applications such as IrDA, Bluetooth, RFID, cell phone baseband etc. because of its superior thermal, electrical, reliability performances and miniaturized package size.

Recently, Cu wire bonding for IC packaging has been used to replace Au wire bonding in fine bond pad pitch applications to reduce package cost. aQFN is one of the packages adopting Cu wire bonding. The overall cost of aQFN packages with Cu wire bonding has been decreased significantly by about 10-15% for each individual piece. With such advantages, it is expected that aQFN will replace many CSP applications, especially for handheld & PDA devices and related applications.

#### Introduction

IC packages are demanding to be smaller, lighter, and fine pitch for high performances and multiple operation functions of electronic devices. For such demands, chip-scale BGAs (CSP), waferlevel chip-scale packages (WLCSP), and leadless packages such as quad flat no-lead packages (QFN) are favored packaging choices. CSP shows the best design flexibility by three-dimensional circuit routing within the substrate. WLCSP provides reasonably good design flexibility by circuit routing through the redistribution layer (RDL). However, the electrical and thermal performances for WLCSP are rela-

Figure 1. Schematic and package outline of aQFN.

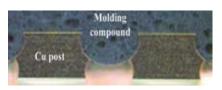

Figure 2. Cross-sectional view of aQFN.

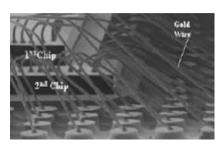

Figure 3. Stacked-die aQFN.

tively low, and the layout is not feasible for high-power applications with the presence of RDL. Both, CSP and WLCSP, are relatively high in cost. Leadless packages possess the best electrical and thermal performances<sup>[1]</sup> as well as the lowest fabrication cost among these packages, however, their lead counts are quite low and their design flexibility clearly is the worst.

In order to expand the application range of leadless packages and to preserve their cost and performance advantages, efforts have been devoted to increasing the number of leads, following the QFN structure in particular (e.g., $[^{2,3]}$ ). The multiplerow QFN does suffer from solder bridging between neighboring terminals when the pitch is small. The low stand-off of QFN solder joints may also raise thermo mechanical reliability risks. To overcome these issues, the *a*QFN package, whose schematic and outline are shown in Figure

1, has been proposed and developed <sup>[4, 5]</sup>.

aQFN is an enhanced version of conventional QFN and is capable of providing many more footprints at an identical package size, with the I/O number approaching that of CSP. The unique fabrication process of aQFN consists of double-sided etching of the Cu lead frame to create isolated Cu posts with a relatively high standoff (see Figure 2). The higher standoff leads to enhanced solder wettability control which enables fine-pitch devices as well as improved thermomechanical reliability of the solder joints<sup>[3]</sup>. This particular packaging structure also offers the possibility of die stacking, as shown in Figure 3. Furthermore, a certain amount of routing can be done through post-to-post wire bonds or within the mother board.

#### Fabrication Process of aQFN

The fabrication process of aQFN is composed of two major sections. In section one, NiAu is plated in the pattern of the aQFN circuit pattern. The NiAu layer is then used as a photo resist or etching mask for half-etching the copper strip. The half-etched lead frame is shipped to the assembly house for IC packaging. The assembly process follows sequentially with die attach, wire bond, and molding. Clearly, the half-etched lead frame is capable of providing a cavity for the die that enables die stacking with low package profiles, or it avoids excessive thinning of the die, and hence reduces the fabrication risk during the wafer thinning process. The half-etched lead frame also eliminates the possibility of mold flash along the interface between lead frame and tape as in a conventional QFN process. After molding, the Cu lead frame undergoes another etching step down to the compound to form the isolated Cu posts, as shown in Figure 2.

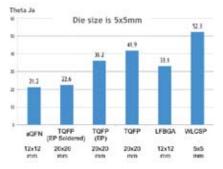

Three packages: aQFN, BCC++ and QFN, all leadless packages were modeled. We note that thermal performances are similar among all leadless packages. Slight differences of  $\theta_{JA}$  among aQFN, QFN and BCC++ come from the thickness of the die pad. Thicker die pads benefit the heat dissipation.

The thermal characteristics of exposed pad LQFP, regular LQFP, CSP and

## MEPTEC Packaging Technology

Figure 4. Thermal data of different type packages.

WLCSP, were evaluated via  $\theta_{JA}$  and are compared in Figure 4. Power dissipation was set to 2W and ambient temperature to 25°C. We note that thickness of die and package does not have a significant effect on thermal characteristics. Clearly from the chart, the thermal performances are similar for packages with die attach paddle soldered to the PCB. CSP has multi-Cu layers which enhance thermal performance. Bare die of WLCSP has the worst heat dissipation.

#### Performance Comparison: aQFN vs. CSP

To demonstrate the excellent performances of aQFN over CSP, identical functions are intentionally designed into both aQFN and CSP packaging structures, so that thermal and electrical performances of these two structures can be reasonably compared. With the same functions, aQFN allows a thicker die (or a lower fabrication risk during wafer thinning process) as well as a smaller and thinner package silhouette compared to CSP (see Table 1).

Comparisons of thermal and electrical characteristics between the two packages are listed in Tables 2 and 3, respectively, in

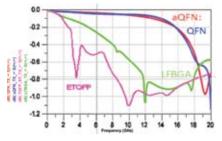

Figure 5.1. Insertion loss of *a*QFN, QFN, TQFP and CSP.

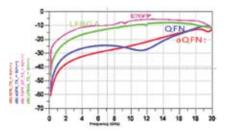

Figure 5.2. Return loss of *a*QFN, QFN, TQFP and CSP.

|                      | aQFN                         | CSP              |  |  |

|----------------------|------------------------------|------------------|--|--|

| Package size         | 10.4 × 10 × 0.85             | 13 × 13 × 1.4    |  |  |

| Lead count           | 254                          | 293              |  |  |

| Die size             | $4.6 \times 4.4 \times 0.28$ | 4.6 × 4.4 × 0.13 |  |  |

| Die pad size         | 5.2 × 5                      |                  |  |  |

| Die attach thickness | 0.025                        |                  |  |  |

| Terminal/Ball size   | 0.2 × 0.2                    | 0.3              |  |  |

| Terminal/Ball pitch  | 0.4                          | 0.65             |  |  |

| Standoff             | 0.03                         | 0.3              |  |  |

| Substrate thickness  |                              | 0.26             |  |  |

Table 1. Component Dimensions of Packages.

| Package Type | Air Velocity (m/s) | θ <sub>JA</sub> (°C/W) |  |

|--------------|--------------------|------------------------|--|

|              | 0                  | 23.53                  |  |

| <i>a</i> QFN | 1                  | 17.78                  |  |

|              | 2.5                | 15.74                  |  |

|              | 0                  | 35.72                  |  |

| CSP          | 1                  | 31.32                  |  |

|              | 2.5                | 29.11                  |  |

Table 2. Comparison of Thermal Characteristics.

| Package Type | Trace Length (mm) | <b>R (m</b> Ω) | L (nH) | C (pF) |  |

|--------------|-------------------|----------------|--------|--------|--|

| aQFN         | Shortest: 0.91    | 70.4           | 0.982  | 0.160  |  |

| aurn         | Longest: 3.31     | 210.5          | 3.845  | 0.329  |  |

| CSP          | Shorter: 2.97     | 157.2          | 2.723  | 0.742  |  |

|              | Longest: 3.00     | 232.2          | 5.854  | 0.953  |  |

Table 3. Comparison of Electrical Characteristics.

which the thermal characteristics are evaluated under a power dissipation of 1W and an ambient temperature of 25°C. It is clear from the tables that *a*QFN outperforms CSP in terms of thermal and electrical performances, even though the longest trace in CSP is shorter than that in *a*QFN.

The electrical simulation data in the frequency domains are shown in Figure 5.1 (Insertion loss) and Figure 5.2 (Return loss). From both data, the *a*QFN can run above 16GHz (at -0.3dB) and 17GHz (at -15dB) which is a lot higher than CSP packages. Besides the excellent thermal and electrical performances, *a*QFN is also cost-effective compared to CSP because of the absence of the substrate.

#### aQFN Package Qualification

A 10.2x10.2mm *a*QFN 246L package has been chosen for packaging qualification under the conditions shown in Table 4. This package passed moisture sensitivity level 2a of pre-condition and also passed TCT 1000 cycles, PCT 336 hours and HTST 1700 hours.

#### aQFN Surface Mount Process Study

Given the lower package standoff  $(50\mu m)$ and fine pitch terminals (0.47mm) of *a*QFN when compared to CSP  $(200\mu m$  solder ball height and 0.5mm pitch), SMT tends to be more difficult. To improve the assembly yield, SMT DOEs were performed and

| Condition<br>(Package)     | Progress                  |

|----------------------------|---------------------------|

| Moisture<br>Sensitivity    | Passed Level-2a<br>@260°C |

| TCT:<br>-65°C ~ RT ~ 150°C | Passed 1000 cycles        |

| HTST: +150°C               | Passed 1700 hours         |

| PCT:<br>121°C 85%RH, 2atm  | Passed 336 hours          |

#### Table 4. Packaging Qualification Conditions.

"aQFN Surface Mount Application Notes" have been developed to ensure that it has high yield rate in SMT assembly. Some design rules from the application notes are listed in Table 5.

Table 6 shows the yield data from five different SMT assembly houses which followed the "aQFN SMT Application Notes". The overall yield is 99.3%. The top 3 defect modes are solder bridging (short), cold joints (open) and mis-alignment (placement accuracy).

#### Conclusions

aQFN package is an enhanced version of conventional QFN which is capable of providing many more footprints at an identical package size and with the I/O number approaching that of CSP. It is an ideal solution for electrical components of portable telecommunication devices for its superior thermal, electrical, and reliability performances and miniaturized package size. It is expected that *a*QFN will replace many CSP-BGAs.

It has been shown that the electrical and thermal performance of lead frame packages is retained at similarly low costs. *a*QFN outperforms CSP and WLCSP packages electrically and thermally and most importantly in cost.

"aQFN Surface Mount application Notes" have been developed and very high SMT assembly yields have been demonstrated at five independent assembly houses.

#### Acknowledgments

The authors would like to thank Yuan-Ting Chang, Chang-Chi Lee, and Chi-Wei Wu with ASE, Inc. for their support in performing thermal and electrical analyses.

#### References

- I. Lu, A. C. W. et al, "Electrical and Thermal Modelling of QFN Packages," Proc. 3rd Electron. Packag. Technol. Conf., Singapore, 2000, pp. 352-356.

- Retuta, D. V. et al, "Design and Process Optimization for Dual Row QFN," Proc. 56th Electron. Comp. Technol. Conf., San Diego, CA, USA, 2006, pp. 1827-1835.

- Ramos, M. J. et al, "The Method of Making Low-cost Multiple-Row QFN," Proc. 32nd Int. Electron. Manuf. Technol. Symp., San Jose, CA, USA, 2007, pp. 257-263.

- United States Patent Nos. 6,238,952; 6,261,864; 6,306,685;

6,333,252; 6,342,730; 6,495,909; 6,528,893; 6,700,188;

6,861,295.

- 5. Japanese Patent No. 3,780,122.

- 6. Courtesy by Mitsui High-tec, Inc.

- 7. ASE group, "aQFN Surface Mount Application Notes V9", 2009-11-12.

| aQFN Package       |                       |               | PCB Land Pad Design |                    |                             | Stencil           |                 |

|--------------------|-----------------------|---------------|---------------------|--------------------|-----------------------------|-------------------|-----------------|

| Land Pitch<br>(mm) | Terminal<br>Size (mm) | Land<br>Shape | Land<br>Shape       | Copper<br>Pad (mm) | Solder Mask<br>Opening (mm) | Thickness<br>(mm) | Opening<br>(mm) |

| 0.8                | 0.4                   | Square        | Square              | 0.43               | 0.53                        | 0.12              | 0.48            |

| 0.8                | 0.4                   | Circle        | Circle              | 0.43               | 0.53                        | 0.12              | 0.48            |

| 0.65               | 0.35                  | Square        | Square              | 0.375              | 0.475                       | 0.12              | 0.4             |

| 0.65               | 0.35                  | Circle        | Circle              | 0.375              | 0.475                       | 0.12              | 0.4             |

| 0.5                | 0.3                   | Square        | Square              | 0.325              | 0.425                       | 0.1               | 0.38            |

| 0.5                | 0.3                   | Circle        | Circle              | 0.325              | 0.425                       | 0.1               | 0.38            |

| 0.5                | 0.25                  | Square        | Square              | 0.275              | 0.375                       | 0.1               | 0.33            |

| 0.5                | 0.25                  | Circle        | Circle              | 0.275              | 0.375                       | 0.1               | 0.33            |

| 0.47               | 0.27                  | Circle        | Circle              | 0.27               | 0.37                        | 0.1               | 0.32            |

| 0.47               | 0.245                 | Circle        | Circle              | 0.27               | 0.37                        | 0.1               | 0.32            |

| 0.4                | 0.2                   | Square        | Square              | 0.225              | 0.325                       | 0.1               | 0.27            |

| 0.4                | 0.2                   | Circle        | Circle              | 0.225              | 0.325                       | 0.1               | 0.27            |

#### Table 5. Design Rules of Stencil Opening.

| SMT Assembly         | X-ray                        | O/S Test                     | Yield |

|----------------------|------------------------------|------------------------------|-------|

| House                | (passed units)/(total units) | (passed units)/(total units) | %     |

| SMT Assembly House 1 | 9989/9998                    | 9987/9998                    | 99.9% |

| SMT Assembly House 2 | 12993/13020 12977/13020      |                              | 99.7% |

| SMT Assembly House 3 | 9982/9990                    | 9952/9990                    | 99.6% |

| SMT Assembly House 4 | 14997/15055                  | 14865/15055                  | 98.7% |

| SMT Assembly House 5 | 11981/11996 11854/11996      |                              | 98.8% |

| Summary              | 59942/60064                  | 59635/60064                  | 99.3% |

#### Table 6. Yield Data from Five SMT Assembly Houses.

#### **Custom Turn-Key Assembly Solutions in 24 Hours or Less**

Wafer Preparation · Backgrinding to 58µ

- Wafer dicing, including MPW

- · Die sort via wafer map or ink dot

Unlimited Plastic Package Types

Latest packages including dual row MLF, DFN, µBGA, etc

#### www.icproto.com

Assembly Services

Plastic or ceramic

Gold wire bonding

Stacked die, MEMS, etc

- · Remolding to JEDEC spec

- · Branding

- · BGA Balling

10987 Via Frontera · San Diego, CA 92127 · 858-674-4676 · Fax 858-674-4681 a division of Delphon

## METEC Industry News

Editor's Note: A portion of the press release below was omitted in our last issue and is being rerun in its entirety.

#### IEEE Rayleigh Award to Sonoscan's Dr. Kessler

Dr. Lawrence W. Kessler guiding the latest developments in acoustic microscopy.

ELK GROVE VILLAGE, IL – On September 21 in Rome, Italy, Sonoscan president Dr. Lawrence W. Kessler received the prestigious Rayleigh Award presented by the Ultrasonics, Ferroelectrics, and Frequency Control (UFFC) Society of the IEEE.

Each year a recipient is selected on the basis of achievements in research, education, publications, and technical innovations. Since he founded Sonoscan in 1974, Dr. Kessler has been a conspicuous leader in each of these areas. As the Chief Technology Officer of Sonoscan, he has been responsible for many of the numerous patents that Sonoscan has received over the years.

He has also spearheaded the continuous flow of technical innovations that have grown the utility and versatility of acoustic micro imaging systems into the industry that we have today. In 1975 Sonoscan introduced the first commercially available acoustic microscope, the SLAM (Scanning Laser Acoustic Microscope). In 1984 Sonoscan introduced the reflection-mode C-SAM" (C-Mode Scanning Acoustic Microscope) system, which was the precursor of all modern acoustic microscope systems.

Sonoscan, Inc., 2149 East Pratt Blvd., Elk Grove Village, IL60007, Phone: 847.437.6400, x240, Email: info@sonoscan. com, Web: www.sonoscan.com.

#### Honeywell Announces New Thermal Management Materials for Portable Computing Devices

MORRIS TOWNSHIP, NJ – Honeywell Electronic Materials has announced a new printable thermal management material designed to help manage the tremendous heat produced by increasingly powerful semiconductors in portable computing devices such as laptops and netbooks.

Honeywell is a recognized leader in developing thermal management solutions that transfer and dissipate heat, and the new material. Honeywell PCM45M-SP, builds on Electronic Materials' existing line of thermal management materials. As semiconductors become more powerful and smaller. more heat is being generated in the confined spaces where semiconductors are packaged for end-use applications. This tremendous heat can damage the semiconductor or degrade its performance, and it can damage the device as well.

In typical mobile computing applications, chip temperature rises steeply at start-up and remains high during operations. PCM45M-SP is designed to meet these specific thermal management requirements, delivering reliable power cycling performance where other thermal materials would typically fail.

PCM45M-SP can withstand more than 1,000 hours at 150°C without degradation and more than 1,000 temperature cycles. The application is not limited to heat sink design, and the material may be applied to a component, heat sink or thermal spreader in any shape built into the printing screen. Additionally, the enhanced stability of this new material minimizes or eliminates the need for premixing, conserving time and resources.

For more information about Honeywell products visit www. honeywell.com/em.

#### Simultaneous Double Sided Probing System

WINOOSKI, VT - SemiProbe has announced the installation of a new enabling technology - simultaneous double sided prober. The system will provide test access to a next generation sensors. Previously, double sided probers were used primarily as a part of an emission microscope system which required the device to be probed from either the top or the bottom depending upon the orientation of the emission microscope. These systems were designed to allow probe contact on either side of the wafer, but not both at the same time. New devices with active regions on both sides of the wafer as well as some TSV (Thru Silicon Via) technologies will require individual probe contact on both sides of the wafer at the same time. The new system installed at a leading research laboratory is an enabling technology allowing access to device information never before available thru simultaneous contact with probes on both sides of the wafer.

More information about SemiProbe may be found at www.semiprobe.com or by calling (802) 860-7000.

#### APM Ships Pressure Sensor Elements to Automotive Industry

HSINCHU, TAIWAN – Asia Pacific Microsystems, Inc. (APM) announced that it has shipped over 2 million MEMS pressure sensor elements to a leading global automotive electronic company. APM provides MEMS foundry services for the piezoresistive sensor elements which are key components for the pressure sensor business. With intensive engineering development and product qualification work with this customer, the first production was launched in May 2009, and so have the additional product families in early 2010. APM is shipping the sensor elements to this first tier customer's plant for module assembly and calibration.

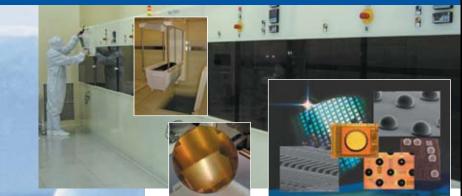

APM is also a key partner to the same customer for the MEMS pressure sensor development roadmap. Early collaboration between the customer's design group and APM's process experts facilitates the turn-key proto-type fabrication and a true "design for manufacturability" model. This type of relationship aids in launching cost efficient, high quality, and high yield products.

APM is a pure-play MEMS wafer foundry founded in 2001. It is one of the leading MEMS wafer foundry service providers with a 27,000 square foot 6-inch MEMS fab comprised of a broad range of MEMS fabrication capabilities. APM, an affiliated company of United Microelectronics Corporation, is ISO 9001, ISO14001 and TS16949 certified.

#### NIST Studies Spray-On Manufacturing of Transistors

A multidisciplinary research team at the National Institute of Standards and Technology (NIST) has found that an organic semiconductor may be a viable candidate for creating large-area electronics, such as solar cells and displays that can be sprayed onto a surface as easily as paint.

While the electronics will not be ready for market anytime soon, the research team says the material they studied could overcome one of the main cost hurdles blocking the large-scale manufacture of organic thinfilm transistors, the development of which also could lead to a host of devices inexpensive enough to be disposable.

#### FCPR

ΤΕ C Η ΝΙ C A L ONE-DAY SYMPOSIUM & EXHIBITS A

MEPTEC MEMS Symposium

SOCIATION SPONSOR MANCEF

**MEMS and IC System Integration:** From Sensing to Awareness

May 20, 2010 • Wyndham Hotel • San Jose, California

**Presenting Companies:**

8th Annual

- Amkor Technology

- Analog Devices

- Fraunhofer Institute for Silicon Technology (ISIT)

- Fullpower Technologies

- IMEC

- Intel Corporation

- IntelliSense

- **MEMS Industry Group (MIG)**

- **Roger Grace Associates** Sandia National Laboratories Silicon Clocks SVTC **University of California** at Berkeley

- WiSpry, Inc.

- Yole Développement

ONL **C**. **O R G** REGISTER **ODAY** МЕР Т Ξ

MEDIA SPONSORS

semiconductor packaging news SMALLTIMES

#### A SPECIAL ONE-DAY TECHNICAL SYMPOSIUM & EXHIBITS

**AEPTECPRESENTS**

May 20, 2010

Wyndham San Jose San Jose, California 8:00 a.m. to 5:00 p.m.

Table Top Exhibits 10:00 a.m. to 6:30 p.m.

Reception 5:00 p.m. to 6:30 p.m.

SYMPOSIUM CO-CHAIRS AND COMMITTEE

Janusz Bryzek, Ph.D. Chief Technical Officer & Chairman LV Sensors

Sean Cahill VP of Research and Development Bridge Wave Communications

John Heck, Ph.D. Research Scientist, MEMS Packaging Intel Corporation

Bance Hom President Consultech International

Joseph R. Mallon, Jr. CTO axept / Stanford University researcher

## 8th Annual **MEPTEC MEMS Symposium** MEMS and IC System Integration: From Sensing to Awareness

ew technologies have life cycles of about 50 years. The semiconductor industry emerged in 1950s, and the market leaders experienced extended periods of high (70%) gross margins. The days of such margins seem to be over, and the number of market segments with significant (>25%/y) growth has shrunk. However, many high growth segments are correlated to MEMS-based devices, which add real-world sensing and actuation to digital logic and memory to create smart, aware systems. From a MEMS perspective, access to advanced custom ICs has become easy and inexpensive, enabling a wealth of new, intelligent, integrated systems.

As high volume MEMS markets have emerged, we have witnessed a trend from discrete sensors to "smart" sensors integrated with electronics, bringing a potential for extending the period of de-commoditized (high gross margin) semiconductor applications through system level MEMS-IC integration. We are now at the cusp of another wave of integration, where multiple sensors can be integrated together with electronics into systems that are significantly more "aware" – providing not just sensing, but gesture recognition, pinpoint location, human activity, and environmental conditions to name a few. Networking all of these sensors together provides yet another level of smart integration.

While first generations of MEMS devices were offered without electronics, with time a lot of effort went towards on-chip integration of electronics. This symposium will cover the many integration technologies that have emerged, each with its strengths and weaknesses.

#### Symposium Keynote

#### Accelerometrics: The Art of Motion Sensing... Because Motion is Life

Philippe Kahn, CEO and Founder of Fullpower Technologies

In his keynote presentation Philippe Kahn will discuss the art of motion sensing. Please join him as he reflects on how motion shapes lives and how hybrid sensors hold a special opportunity for the next generation of mobile devices to integrate complex and advanced motion solutions and the necessary software technology. Just like microphones couldn't deliver advanced speech recognition solutions, the best sensors need an advanced motion recognition engine. What is this engine? Kahn will use the MotionX technology platform as an illustration of these advanced software solutions.

Philippe Kahn is a technology visionary and creator of the first complete camera-phone solution. Kahn is presently CEO and founder of Fullpower Technologies, his fourth successful technology company, which specializes in mobile sensing solutions for use in mobile phones and other consumer electronic devices. He holds a master's degree in mathematics and is the author of dozens of patents. In addition Kahn has received numerous technology and business awards including the 2002 International Imaging Association (I3A) Leadership Award and in 1995 was selected as one of Byte Magazine's twenty most important people in the history of the computer industry.

#### MEMS Industry Group's Members Only event, METRIC 2010

We are pleased to be co-locating with the MEMS Industry Group's Members Only event, METRIC 2010. METRIC will be held the day preceding the MEPTEC symposium, on May 19, with a special reception and panel discussion on May 18. Visit the MIG website at **www.memsindustrygroup.org** for details.

#### **TECHNICAL PRESENTATIONS** Listed Alphabetically by Company

MEMS Packaging Capabilities Enabling Higher Level of IC Integration

Jeff Miks Senior Director for BGA and MEMS Products

Amkor Technology

#### Monolithic to Multi Chip Integration: Advantages and Disadvantages

Rob O'Reilly Member Technical Staff MEM Sensors

#### Analog Devices

#### Technologies for a Small Scale Co-integration of MEMS and ASIC in Vacuum Wafer Level Packages

Norman Marenco Research Scientist

Fraunhofer Institute for Silicon Technology (ISIT)

#### SiGe MEMS Technology: A Monolithic Integration Approach

Raffaella Borzi, Ph.D. Business Development Director

#### IMEC

#### MEMS Integration Strategies with Applications in Wireless and Computing

John Heck, Ph.D. Research Scientist

#### Intel Corporation

#### New Generation EDA Tools Supporting Various MEMS-ASIC Integration Strategies

Sandeep Akkaraju CEO

#### IntelliSense

#### From Wafer to Wii: An Industry Group's Perspective on MEMS Fabrication

Karen Lightman Managing Director *MEMS Industry Group (MIG)*

#### MEMS-Based System Solutions: Current and Future High Volume Applications

Roger H. Grace President

#### **Roger Grace Associates**

#### Next Frontier for MEMS-IC Integration: Aluminum Nitride (AIN) Frequency References, Filters and Sensors... Drivers and Challenges

Kenneth E. Wojciechowski, Ph.D. Principle Member of Technical Staff

Sandia National Laboratories

#### CMEMSTM: CMOS-Integrated SiGe MEMS Resonators for Timing and More

Emmanuel Quevy Founder, President & CTO

#### Silicon Clocks

#### Enabling MEMS Integration with CMOS at 200mm Wafer Processing

Wilbur Catabay, Vice President Technology and Engineering

#### SVTC

#### Integration Benefits for Micromechanical RF Circuits

Prof. Clark T.-C. Nguyen Department of Electrical Engineering and Computer Sciences

University of California at Berkeley

#### Integrated RF-CMOS MEMS Solutions for Mobile Applications

Jeffrey L. Hilbert President, COO & Co-Founder

#### WiSpry, Inc.

#### MEMS Manufacturing Evolution: From Hybrid to Monolithic to 3D Integration

Jeffrey Perkins Director, North America Business Development

Yole Développement

#### TABLE TOP EXHIBITORS As of 4/9/2010

- A.M. Fitzgerald & Associates, LLC

- AGC Electronics America

- Asia Pacific Microsystems (APM)

- ASE Group

- Boschman Technologies

- Coventor, Inc.

- cyber TECHNOLOGIES USA, LLC

- EV Group

- -

- FRT of America

i2a Technologies

Mühlbauer, Inc.

Palomar Technologies

Pac Tech USA

- MEMS Industry Group

- MEMS & Nanotechnology Exchange

- Mirror Semiconductor

- Tegal Corporation

Tousimis

- Yole Développement

PhotoSciences, Inc.

Silex Microsystems

Promex Industries, Inc.

XACTIX, Inc.

SoftMEMS

For more information contact Bette Cooper at 650-714-1570, email: bcooper@meptec.org, fax: 866-424-0130, or visit the MEPTEC web site at meptec.org.

## MEPTECPRES

#### SYMPOSIUM REGISTRATION

#### 8th Annual **MEPTEC** MEMS **Symposium**

**MEMS and IC System Integration: From Sensing to** Awareness

#### May 20, 2010

Wyndham San Jose San Jose, California

8:00 am - 5:00 pm Exhibits 10:00 am - 6:30 pm Reception 5:00 pm - 6:30 pm

#### **Pre-Registration /** Cancellation

Guaranteed registration will be accepted by mail, fax, phone or e-mail. Space is available on a first come, first served basis. Preregistering and pre-paying will guarantee you admission, proceedings materials and lunch.

Please note that you may pay at door for attendance, but you must hold your registration with a credit card. There will be an additional \$25.00 fee to register at door on the day of the event without a pre-paid or held reservation.

**Refunds for advance payment** will be given in full provided cancellation is received 72 hours prior to the event (by end of day Friday, May 8). If you chose to pay at the door but do not show and do not cancel 72 hours in advance, the credit card you provide to hold the reservation will be charged.

#### **Please Register by** May 14th

Registration confirmation, lo-cation map and other information will be sent to you.

#### **Hotel Information**

A limited block of rooms has been reserved at the Wyndham Hotel for a rate of \$129.00. The hotel is conveniently located at 1350 North First Street, San Jose, CA in close proximity to the San Jose Airport. Call 408-453-6200 or 800-996-3426 to reserve your room. Be sure to mention MEPTEC in order to secure the special rate.

| Name           |     |  |

|----------------|-----|--|

| Title          |     |  |

| Company        |     |  |

| Address        |     |  |

| City/State/Zip |     |  |

| Phone          | Fax |  |

| E-mail         |     |  |

|                |     |  |

#### **Symposium Fees:**

| Attendance Fee: D MEPTEC/MIG Members \$395 D Non-Members \$495<br>Includes Break Refreshments, Lunch, Reception and Proceedings.                                                                      | \$                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Proceedings on CD: D MEPTEC/MIG Member or Non-Member \$35                                                                                                                                             | \$                     |

| Non-Attendee Proceedings on CD: Quantity of@ \$75 each<br>Will be shipped two weeks following event.                                                                                                  | \$                     |

| Image: Table Top Exhibit Space*:       Image: Medical Method is a method in the symposium attendance, lunch and proceedings.         Image: Includes one symposium attendance, lunch and proceedings. | \$                     |

| <b>Exhibits Only:</b> You must Pre-register to attend exhibits at no charge.                                                                                                                          | <u></u> \$ <b>FREE</b> |

| <b>3 MEPTEC Membership:</b> Take this opportunity to sign up for a MEPTEC membership and enjoy an <u>immediate discount</u> on this symposium!                                                        |                        |

| 🖵 Individual Membership / 1 yr. / \$95                                                                                                                                                                | \$                     |

| Individual Membership / 1 yr. / \$95 Corporate Membership / 1 yr. / \$475 (Includes 6 members)                                                                                                        | \$<br>\$               |

|                                                                                                                                                                                                       | \$<br>\$               |

Check enclosed (Make payable to MEPTEC or MEPCOM) □ Will pay at door (see pre-registration information) Credit Card: UVisa □ MasterCard □ American Express

Discover Exp. Date

Card Holder Name

Card Number

Signature

5 Mail or fax this form to: MEPTEC, P.O. Box 222, Medicine Park, OK 73557

The team's work showed that a commonly used organic transistor material, poly (3hexylthiophene), or P3HT, works well as a spray-on transistor material because, like beauty, transistors aren't very deep. When sprayed onto a flat surface, inhomogeneities give the P3HT film a rough and uneven top surface that causes problems in other applications. But because the transistor effects occur along its lower surface – where it contacts the substrate - it functions quite well.

The simplicity of spray-on electronics gives it a potential cost advantage over other manufacturing processes for organic electronics. Other candidate processes require costly equipment to function or are simply not suitable for use in high-volume manufacturing.

#### Imec and Synopsys Collaborate on 3D Stacked IC Development

MOUNTAIN VIEW, CA - Synopsys, Inc. and the Belgian nanoelectronics research center, imec, have announced that they have entered into a collaboration to use Synopsys TCAD (Technology Computer-Aided Design) finite-element method tools for characterizing and optimizing the reliability and electrical performance of through-silicon vias (TSVs). The collaboration will accelerate the development of 3D stacked IC technologies.

While considered an emerging technology, 3D stacked IC complements conventional transistor scaling and allows multiple chips to be stacked and integrated into a single package. This technology reduces form factor and power consumption, and increases bandwidth of inter-chip communication by minimizing connections through the circuit board with high parasitic capacitance. As with other innovative technologies, 3D stacked IC introduces a number of new issues that can potentially affect its reliability and performance. The collaborative research to address these issues will take place at imec, where silicon wafers with test structures will be manufactured and tested, and Synopsys' TCAD tools will be used to model the TSVs in the chip stacks to optimize 3D stacked IC performance and reliability.

Synopsys is headquartered in Mountain View, California, and has more than 65 offices located throughout North America, Europe, Japan, Asia and India. Visit Synopsys online at www.synopsys.com.

Imec is headquartered in Leuven, Belgium, and has offices in Belgium, the Netherlands, Taiwan, US, China and Japan. Further information on imec can be found at www. imec.be.

### Global Low-Cost Wafer Bumping Services

• Europe – USA – Asia •

- Quick-turn and mass-production

- Highly competitive, low-cost bumping technology

- Exceptional quality through high-level expertise

#### PAC TECH

Pac Tech GmbH Tel: +49 (0)3321/4495-100 sales@pactech.de www.pactech.de

Pac Tech USA Tel: 408-588-1925, ext. 202 sales@pactech-usa.com www.pactech-usa.com

Pac Tech Asia Sdn. Bhd. Tel: +60 (4) 6430 628 sales@pactech-asia.com www.pactech-asia.com

#### NAGASE & CO., LTD.

Tel: +81-3-5640-2282 takahiro.okumura@nagase.co.jp www.nagase.co.jp

#### **Available Processes**

- Electroless Ni/Au under-bump metallization

- Ni/Au bump for ACF or NCP assembly

- Solder paste stencil printing

- Solder ball drop for wafer-level CSP

- Solder jet for micro-ball placement

- BGA and CSP reballing

- Wafer backside thinning and wafer dicing

#### **Special Features/Technologies**

- Over 10 years experience

- U.S. Government Certified

- 4- to 12-inch wafer capability

- Wafer pad metallization: Al and Cu

- Solder alloys: eutectic SnPb37, lead-free, low-alpha, and AuSn

- Fluxless and contactless bumping for MEMS and optoelectronics

- Ni/Au interface for wire-bond applications

The leader in low-cost electroless wafer bumping.

## Industry News

#### Amkor Technology **Installs Systems from SUSS MicroTec**

GARCHING. GERMANY. - SUSS MicroTec has received orders for multiple 300mm lithography systems from Amkor Technology Inc. The equipment package includes MA300 Gen2 mask aligner systems and ACS300 Gen2 wafer processing clusters for wafer level packaging, wafer bumping and 3D integration technology. Installations at Amkor's K4 plant in Gwangju, Korea, and T1 fab in Hsin-Chu, Taiwan, are scheduled to be completed in Q3 2010.

"As a contract manufacturer for semiconductor companies worldwide we are committed to bringing leading-edge packaging solutions to market". said ChoonHeung Lee, CVP and CTO, Amkor Technology. "SUSS MicroTec's lithography systems have been an integral part of our success and have set an exceptional track record for process capability, reliability, support and overall cost of ownership for our worldwide operations."

For more information about SUSS MicroTec visit their website at www.suss.com.

More about Amkor is available from the company's SEC filings and www.amkor.com.

#### Mil/Aero Reliability **Inspection for Latent** Defects

3-D acoustic image of hybrid device. Arrow indicates internal defect.

ELK GROVE VILLAGE. IL - Sonoscan has publicly announced Sonoscan Critical Evaluation<sup>™</sup>(SCE), a con-

fidential service that acoustically inspects critical electronic components such as hybrids, capacitors and plastic-encapsulated microcircuits used in military and aerospace systems. The service became active in mid-2009.

Acoustic Micro Imaging nondestructively images hidden latent defects such as delaminations, cracks and voids - for example, a delamination on the face of a silicon chip. It also characterizes materials such as encapsulants.

SCE handles individual components, hybrid devices, and printed wiring boards. The purpose of imaging is to locate, identify and analyze internal

## North American Semiconductor Equipment Industry Posts March 2010 Book-To-Bill Ratio of 1.19

SAN JOSE, CA - North America-based manufacturers of semiconductor equipment posted \$1.29 billion in orders in March 2010 (three-month average basis) and a book-to-bill ratio of 1.19, according to the March 2010 Book-to-Bill Report published by SEMI. A book-tobill of 1.19 means that \$119 worth of orders was received for every \$100 of product billed for the month.

The three-month average of worldwide bookings in March 2010 was \$1.29 billion. The bookings figure is up 2.7 percent from the final February 2010 level of \$1.25 billion, and is 423.3 percent above the \$245.6 million in orders posted in March 2009.

The three-month average of worldwide billings in March 2010 was \$1.08 billion. The billings figure is up 6.4 percent from the final February 2010 level of \$1.02 billion, and is 146.8 percent above the March 2009 billings level of \$438.3 million.

"Bookings have now returned to levels seen in late 2007," said Stanley T. Myers, president and CEO of SEMI. "The steady and consistent rise in bookings and billings shows that the industry is on a well-managed growth path."

three-month moving average bookings to millions of U.S. dollars. three-month moving average shipments.

The SEMI book-to-bill is a ratio of Shipments and bookings figures are in

anomalies that can cause electrical failures in service, such as die attach voids in a hybrid device or singulation cracks in a capacitor.

In some applications, the interest is on purely mechanical features in items such as micro spot welds or multi-layer composite materials.

Two groups work together to provide SCE:

the SonoLab<sup>®</sup> applications laboratory personnel; and

hardware engineering, machine shop, software engineering and other Sonoscan departments that give specific support as needed.

Typically client engineers handle their own parts and load them into a laboratory C-SAM<sup>®</sup> system in a secure, certified room at the Elk Grove Village SonoLab<sup>®</sup>. Acoustic imaging, according to the client's requirements, is supervised by Sonoscan specialists who apply their expertise in critical areas such as image interpretation and the use of alternate imaging techniques to achieve the component reliability required by the client.

SCE gives the client company's engineers the control they need over testing and evaluation of their parts as well as the in-house resources to meet the full spectrum of challenges that are part of advanced testing of critical components.

For more information contact SonoLab manager Ray Thomas at 847-437-6400 x 245.

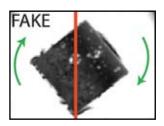

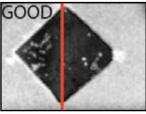

#### Sonoscan Expands Counterfeit Identification Menu

ELK GROVE VILLAGE, IL – SonoLab<sup>®</sup>, the applications laboratory division of Sonoscan, has recently developed analytical techniques that bring to 25 the number of acoustically detectable features and characteristics used to separate counterfeit plastic IC packages from genuine packages.

"The increase in useful tools is the result of our growing base of experience in separating counterfeit components from genuine parts – often within a mixed lot shipment," said SonoLab manager Ray Thomas. "Our laboratories are seeing more questionable parts because the industry has become much more interested in weeding out counterfeit parts. Ideally, engineers have known genuine parts to which they can compare incoming parts."