# Volume 8, Number 4 Creport

### QUARTER FOUR 2004

A Publication of The MicroElectronics Packaging & Test Engineering Council

**INDUSTRY NEWS**

**CMC INTERCONNECT TECHNOLOGIES** has announced the addition of industry veteran **Dr. Rudy Enck** to their technical staff for thermal and electrical measurements. *page 13*

**SILICON BANDWIDTH, INC.** has announced the expansion of their sales and marketing force with the naming of two new Directors of Sales. *page 14*

**HONEYWELL** acquires **MITSUBISHI**'s stake in **GEM MICROELECTRONIC MATERIALS**. page 15

### **TECHNOLOGY**

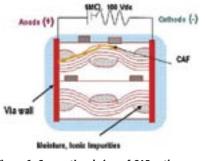

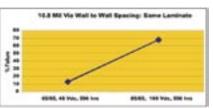

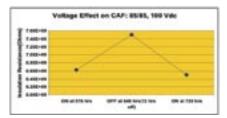

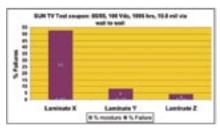

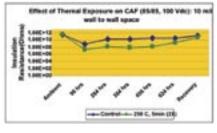

**Gus Karavakis** and **Silvio Bertling** of **Park/ Nelco, Inc.** present *Conductive Anodic Filament (CAF) – The Threat to Miniaturization of the Electronics Industry.* page 24

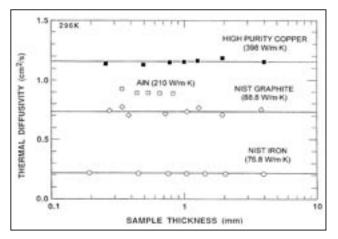

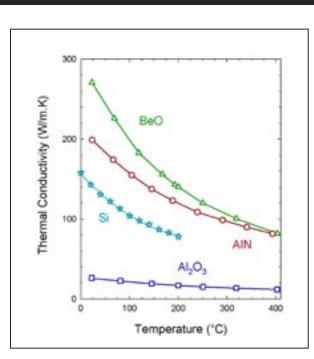

**Rudy Enck, Ph.D.** of **CMC Interconnect Technologies** discusses the important topic of thermal management as it relates to packaging materials. *page 28*

APEX 2005 Exhibition & Conference, colocated with the IPC Printed Circuits Expo, will be held February 22nd - 24th at the Anaheim Convention Center, Anaheim, CA.

One Day Technical Symposium and Exhibits Coming to San Jose February 16th ... page 4

### MEMBER COMPANY PROFILE

nder the leadership of Chief Executive Officer Harry Rozakis, ASAT has launched its Peak Performance Initiative to drive ASAT to become the leader in advanced semiconductor package development by setting industry standards for acceptance, performance, reliability, and time-to-revenue.

**ASAT Holdings Limited** is a global provider of semiconductor assembly, test and package design services. Founded in 1988, ASAT is one of the top ten leading semiconductor, assembly and test services companies. The company offers a definitive selection of semiconductor packages and world-class manufacturing lines. With over 1900 employees, ASAT offers worldwide sales, engineering, and support with operations in the U.S., Asia and Europe. *page 20*

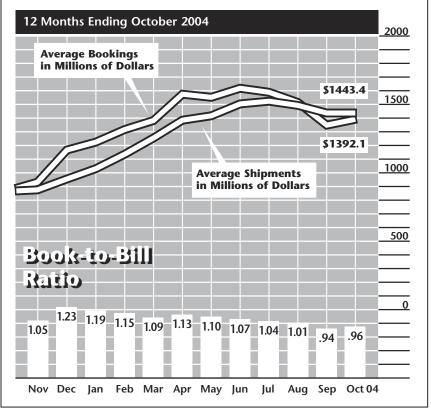

Semiconductor equipment bookings increase 60% above October 2003 level. *page 18*

METALS = CHEMICALS = DIELECTRICS PACKAGING = OPTOELECTRONICS

# Putting the Pieces Together

### Providing the Most Complete Solutions for Your Interconnect Packaging Challenges...

Honeywell is established as a prime supplier in electrical and thermal interconnect products used in the manufacture of high performance BGA and flipchip packages. Our capabilities include design, prototyping, specialized fabrication, metal finishing and high volume manufacturing.

### **Electrical Interconnect: Evaporation & Power Products**

Honeywell's core competencies include manufacture of the high-purity evaporation charges and electroplating anode products that are used for back metallization, underbump metallization and wafer bumping of flipchip die. We offer a comprehensive material set for the manufacture of high power devices.

### Thermal Management: Spreaders, Lids & Stiffeners

Honeywell provides a wide range of thermal heat spreaders, heat slugs and stiffeners used to overcome today's thermal management challenges. We specialize in providing novel thermal solutions for applications requiring the highest performance and tightest tolerances.

#### Thermal Management: Thermal Interface–Phase Change Materials

Our packaging science expertise allows us to address thermal management concerns at various levels within both die-to-package and package-to-system assemblies. Honeywell's PCM45 Series materials exhibit excellent surface wetting characteristics resulting in low contact resistance, but do not degrade with use.

### Putting Together Added Value-

### Combo-Spreader<sup>™</sup> with Pre-attached Phase Change Material

Available only from Honeywell, the Combo-Spreader is an innovative solution for today's advanced thermal challenges. By combining the benchmark thermal performance of PCM45 with our industry leading thermal spreaders, we provide a lasting solution well ahead of the ITRS roadmap, with fewer production steps required.

Our expertise in materials science, metallurgy and chemistry enables Honeywell to provide solutions to your interconnect packaging needs at a reduced cost of ownership...from layer one to package done.<sup>TM</sup>

www.electronicmaterials.com 408-962-2055

© 2004 Honeywell International Inc. All rights reserved. Combo-Spreader and "From Layer One to Package Done" are trademarks of Honeywell International Inc.

### **ELECTRONIC MATERIALS**

#### Volume 8, Number 4 A Publication of The MicroElectronics Packaging & Test Engineering Council

801 W. El Camino Real, No. 258 Mountain View, CA 94040

Tel: (650) 988-7125

Fax: (650) 962-8684

Email: info@meptec.org

nail: info@meptec. Published By

MEPCOM Editor Bette Cooper Design and Production Gary Brown Sales and Marketing Kim Barber

MEPTEC Advisory Board

Phil Marcoux

MEPTEC Executive Director SensArray Seth Alavi SunSil John Bubello Advanced Packaging Magazine

Joel Camarda Camarda Associates

Gary Catlin Global Technology Links Rob Cole FICO America

John Crane J. H. Crane & Associates

Jeffrey C. Demmin

Mark DiOrio MTBSolutions, Inc

Bruce Euzent Altera Corporation

Skip Fehr

Chip Greely Qualcomm Anna Gualtieri

SPEL Bance Hom

Consultech International, Inc. Ron lones

N-Able Group International Pat Kennedy

GEL-PAK

Nick Leonardi CMC Interconnect Technologies Abhay Maheshwari

Xilinx Mary Olsson

Gartner Dataquest

Marc Papageorge Semiconductor Outsourcing Solutions Doug Pecchenino

Ray Petit

Pacific Rim Technology Jerry Secrest Secrest Research

Secrest Research

Gartner Dataquest Russ Winslow Six Sigma

MEPTEC Report Vol. 8, No. 4. Published quarterly by MEPCOM, 801 W. El Camino Real, Mountain View, CA 94040. Copyright 2004 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact Kim Barber, Sales & Marketing at (408) 309-3900, Fax (650) 962-8684.

t seems just a short time ago we were just wrapping up our last issue of 2003, and now it's upon us again! We feel a lot of optimism as we face the close of this "recovery" year, and look forward to an even stronger 2005. We also look forward to continuing to bring you our high quality services which include our popular technical programs, as well as networking and marketing opportunities.

Our next event will be held on Wednesday, February 16, 2005 at the Hyatt San Jose hotel in San Jose, California. The event, entitled The Heat is On: Thermal Management Issues in Semiconductor Packaging, came about as most of our events do: during discussion at one of our very active Advisory Board meetings. This is one of the benefits of an organization like MEPTEC; it doesn't take long once an idea is hit upon to form a committee, set up a kick-off meeting, and off we go! And since this was such a "hot" topic (no pun intended!) we felt it was an easy decision to move forward with the planning of this event. We're pleased that Ananth Naman of **Honeywell**, a long-time MEPTEC supporter and Corporate member, is heading up the event as Symposium Technical Chair. See page 4 for information on this exciting event.

We also offer a follow-up look on a couple of past symposiums. These follow-ups are becoming regular features in each issue. For each event, Jody Mahaffey of JDM Resources writes a pre-symposium article wherein she previews the program, interviews participants, and summarizes in an article which gets distributed to the trade magazines and on-line publications. After the symposium she updates and finalizes the article, and that is what you will see here. See page 6 for her follow-up on our November 11 Innovations in Equipment and Materials for Microelectronics Packaging - Complexity Drives Collaboration. In addition, Julia Goldstein, editor at Advanced Packaging magazine, follows up with a review of our August event on Wafer Level Packaging - see page 7.

One of the feature articles this issue is contributed by **Konstantine (Gus) Karavakis** and **Silvio Bertling** of **Park/Nelco, Inc.**, on *Conductive Anodic Filament (CAF) – The Threat to Miniaturization of the Electronics Industry.* Gus made a presentation on this topic at our October luncheons in both Sunnyvale and Phoenix. This is a highly critical issue that needs to be looked at much more closely. As stated in the article, "CAF will become a major issue for the electronics industry since the trend is for very fine features in the future". See page 24 for this informative piece.

### Our other feature article is Laser Flash Method for Measurement of Thermal Conductivity of Packaging Materials. Since we will be featuring Thermal Management at our next event, we asked MEPTEC Advisory Board member Nick Leonardi, who recently joined CMC Interconnect Technologies, to get their Principal Scientist Rudy Enck, Ph.D. to discuss the important topic of thermal management as it relates to packaging materials. The team at CMC are experts in the area of failure analysis, physical, thermal, and electrical characterization, etc. Dr. Jonathan Harris of CMC will be presenting at the January MEPTEC luncheons in both Sunnyvale and Phoenix on this important topic of Thermal Performance Materials.

Our Editorial this issue is contributed by Leonette Stafford, Silicon Valley Chapter President of the American Society of Test Engineers (ASTE). Leonette lent us her expertise as the Chair of the Test and Burn-In Session at our August Wafer Level Packaging symposium. In her article Analyzing the World of Medical Testing (see page 34), Leonette offers an interesting dual discussion of not just the technological implications of testing in the medical industry, but also how it affects us in a personal and societal manner as well.

Our Industry Analysis coverage this issue is contributed by **Jim Walker** of **Gartner Dataquest**, and longtime MEPTEC Advisory Board member. Jim is always the person

continued on page 5

### **Issue Highlights**

| From The Director                      | page 5  |

|----------------------------------------|---------|

| MEPTEC Events Follow-up                | page 6  |

| Industry Analysis                      | page 9  |

| University News                        | page 11 |

| Industry News                          | page 13 |

| Member Company Profile                 | page 20 |

| Feature Articles                       |         |

| • Conductive Anodic<br>Filament (CAF)  | page 24 |

| • Laser Flash Method of<br>Measurement | page 28 |

| Calendar                               | page 33 |

| Editorial                              | page 34 |

|                                        |         |

## MEPTEC Council Update

# **IEPTECPresents**

MicroElectronics Packaging and Test Engineering Council

#### SYMPOSIUM ONE-DAY TECHNICAL 8 ЕХНІВІТЅ A

# Honeywell

**ELECTRONIC MATERIALS**

GOLD SPONSORS

CERAMICS PROCESS SYSTEMS

SILVER SPONSORS

February 16, 2005 • Hyatt San Jose, San Jose, CA • 8:00 a.m. - 5:00 p.m. Table Top Exhibits 10:00 a.m. - 7:00 p.m. • Reception 5:00 p.m. - 7:00 p.m.

# The Heat Is On: **Thermal Management Issues in Semiconductor Packaging**

icroprocessors are the core of the systems that enable the "on-demand" information age we enjoy today. From "4 GHz laptops" to "download and view" movies to blade servers that store massive amounts of information, the centerpiece of the enabling technology is the ever more powerful microprocessor. While the industry has attempted to stay true to Moore's Law, with exponential growth in the number of transistors per integrated circuit, the future trajectory is not so clear due to on-chip thermal management challenges.

Today, companies are preparing to ramp into production CPU and GPU designs that are approaching one billion transistors. As these chips become more powerful and run at higher frequencies, they draw more power that must be dissipated from the chip during its operation. The drive to shrink die size will further magnify this problem, with the localized thermal flux on-chip expected to rise from 200 to 500 W/cm<sup>2</sup> in the next few years! While solutions exist today - refrigeration systems, liquid cooling, diamond coatings - cost continues to limit their proliferation into high volume markets. Thermal management of microelectronic systems is moving into the spotlight as one of the major challenges that may potentially limit the continued increase in performance that the semiconductor industry has grown to expect.

Thermal management is a concern for users throughout the value chain, from systems providers to IC manufacturers. Content providers such as Google and Yahoo need to maintain low temperatures in their server farms. Designers of graphics

chips and microprocessors have to balance thermal management with reliability, die size and transistor count. Materials suppliers need to consider how the properties of their materials will affect thermal performance. Thermal issues are more important than ever to packaging engineers as they implement 3D technologies. Thermal management at each level impacts the entire value chain, and cost tradeoffs will help determine where to focus efforts. Improvements in heat dissipation at the package level could, for example, ultimately decrease the amount of system level cooling required in a server, resulting in overall cost savings even though the package may be more expensive. Both thermal modeling and cost modeling are critical as the industry moves toward viable solutions.

In order to better understand the ramifications of these issues, MEPTEC is bringing together a variety of speakers in a one-day symposium to highlight major problems and potential solutions, with an emphasis on approaches at the package level. Chipmakers, package manufacturers, thermal designers, systems integrators and other semiconductor industry players will share their expertise, with the goal of helping attendees understand the critical role thermal management issues will play in strategic planning for tomorrow's new products.

### **Session Topics:**

- Keynote and Forecasting

- Thermal Issues and Challenges

- Characterization and Modeling

- Thermal Management Solutions

REGISTER ONLINE TODAY AT WWW.MEPTEC.ORG

MEDIA SPONSORS

semicondu

### **From The Director**

# Keep Those Innovations Coming!

e all know that new products are needed to keep an industry vibrant and moving forward. But how often do we think about how many players it takes to create the new products?

This thought hit me as I attended the Advanced Packaging Magazine 2004 Advanced Packaging Awards held each year during Semicon West. Nineteen awards were presented to a wide array of material, equipment and IP suppliers. Discussing the awards with AP's Publisher, John Bubello, I learned that these nineteen were from a pool of over sixty candidates, and all excellent. AP judges the product innovation on ingenuity in the areas

of 3-D design, test, inspection, manufacturing methods, and materials.

Many of the products recognized at this event were created due to the expressed need of an end user of, in our case, semiconductor packages. Others were brainchilds of smart inventors who've studied the way we have been doing things and want to try something better

Wanting to expand on AP's efforts to recognize these achievements, MEPTEC sponsored a symposium titled "Innovations in Equipment and Materials for Microelectronics Packaging - Complexity Drives Collaboration", on November 11 at the Hyatt in San Jose. Under the capable Chairmanship

of Marc Papageorge, we were able to allow twenty-nine companies to showcase one of their new innovations.

A couple of our goals with this event were to understand and to take away what these "enablers" are doing in the areas of process development, equipment innovations, materials, partnerships, and the array of other areas necessary for meeting the needs of tomorrow's semiconductors. The feedback from attendees was so positive that I'm sure this will become another of the many repeat topics sponsored by MEPTEC.

Phil Marcoux Executive Director, MEPTEC

# **MEPTEC Council Update**

continued from page 3

we turn to for help in understanding our ever-changing industry trends related to worldwide semiconductor packaging and assembly. See page 9 for his article entitled Semiconductor Utilization Has Peaked.

Our Member Company Profile this issue is a long-time MEPTEC supporter and Corporate member, and major powerhouse in the industry, ASAT. They are one of the top ten leading SATS companies, and have an impressive portfolio of advanced packaging products. They recently opened Phase 1 of a new manufacturing facility in China. With completion of Phase II in 2005, it will make ASAT one of the largest subcontract assembly companies in China. See their story on page 20.

For our University profile this issue we take a look at North Dakota State University (NDSU). The high plains of the U.S. may seem a strange location for high-tech research, but that's just the case with this unique university entity, known as a Center of Excellence (COE), that is involved with microsensor design and manufacturing. Teaming up with the Department of Defense, this COE is a "key component of an NDSU strategic initiative to promote large-scale multidisciplinary government and industry research programs". We have Jeff Demmin of Tessera, and MEPTEC Advisory Board member, to thank for letting us know about this interesting program (see page 11).

We'd like to thank all of our contributors for making this a great issue. If you're reading our publication for the first time at one of the many events where we distribute, or if you're a new member, we hope you enjoy it.

Thanks for joining us!

**MEETINGS AT** HYATT SAN JOSE. Easier to plan. Easier to enjoy. **GROUP RATE**

## 119 per room, with at least 10 rooms booked per night

Only 1/2 mile from the San Jose Int'l Airport and close to corporate offices, our full service banquet and catering staff can help you plan the perfect meeting. We have 20,000 square feet of beautiful meeting space and all guestrooms and meeting rooms have high-speed wireless Internet access. We will be sure that our full-service business center, two restaurants, room service and in-room amenities meet your every need. For reservations call 408 793 3979. FEEL THE HYATT TOUCH.

Mention this "MEPTEC Report" ad to receive this special rate.

1740 North First Street, San Jose hyattsanjose.hyatt.com

Valid 1/1/05 to 3/31/05 at Hyatt San Jose when you book and hold your meeting by 3/31/05. Offer valid for new bookings only. To qualify for the rate, meetings must consist of at least 10 paid room nights per night. Reservations subject to availability and must be made in advance. Offer is not combinable with other promotional offers. Not valid in conjunction with previously booked/held meetings or any other promotions/offers. Offer applies to all eligible bookings, including bookings by travel agents and other qualifying third parties at a commissionable rate. Subject to availability of function space and guestrooms at time of booking. To participate in Hyatt Meeting Dividends, meetings must consist of at least 10 paid room nights per night. Qualifying planners must be a Gold Passport members to participate in the Hyatt Meeting Dividends program. For complete Meeting Dividends program terms and conditions visit hyatt.com. Hyatt reserves the right to withdraw this offer at any time. Hyatt Hotels and Resorts encompasses hotels and resorts managed, franchised or leased by two separate groups of companies. Hyatt Corporation and its affiliated and affiliates of Hyatt International Corporation. ©2004 Hyatt Corp.

# **MEPTEC Events Follow-up**

Innovation and Collaboration: The Combination for Success in 2005

### Jody Mahaffey JDM Resources

2004 has been a strong growth year for the semiconductor industry; however, a new round of uncertainty has surfaced as the industry enters the fourth quarter. That's why it's more important than ever for semiconductor companies to find the right combination for that critical production win. Many people in the industry today feel that innovative new products and collaboration between links in the supply chain are the best way to achieve this.

MEPTEC (MicroElectronics Packaging and Test Engineering Council) recently brought together suppliers from the backend equipment and materials world for its fourth technical symposium of 2004 entitled "Innovations in Equipment and Materials for Microelectronics Packaging – Complexity Drives Collaboration." The one-day symposium was held on November 11th to give attendees a taste for new products coming out and to see how companies have worked together to see positive results.

To help get an overview of the equipment and materials industry and forecast for 2005, MEPTEC was fortunate to get two top analysts in those areas to act as session chairs for the symposium. Those session chairs offered some insight to help us better understand the challenges the industry faces when developing "innovative" products.

The first question many people ask is what makes a product truly "innovative". Dan Tracy, Senior Director, Industry Research & Statistics at SEMI was Session Chair for the Materials Session of the Symposium. He believes, "A product is innovative when it brings forth a new way of manufacturing or designing a product. Perhaps more importantly, an innovative product or idea generates new growth opportunities in its respective markets, and, if innovative in a truly revolutionary sense, new growth opportunities in a broader range of markets."

Mark Stromberg, Semiconductor Equipment Market Analyst for Gartner/Dataquest served as Session Chair for the Equipment Session of the Symposium. Stromberg feels that, "What makes new equipment innovative is that it enables production of new technology or significantly enhances the productivity of current production methods. The equipment discussed at the symposium will enable advanced packaging solutions for the semiconductor industry. These advanced processes include wafer-level packaging, system-in-package and their device testing requirements."

With ever-shortening product life cycles, it can be difficult to develop an innovative new product and get it out to the market in time. This is where the need for collaboration comes in. Marc Papageorge of Semiconductor Outsourcing Solutions (SOS) acted as Symposium Chair for the MEPTEC event. He feels strongly that in order to make it to market in time, collaboration between suppliers and the end customer is a critical place to start. According to Papageorge, "Suppliers must understand what improvements need to be made for product success in the shortest period of time. This can only be done by knowing what the end customers' requirements really are. Ultimately all parties in the supply chain are needed to assure the end solution is understood and met."

Dan Tracy agrees. "A key factor, given that technology is accelerating and product life cycles are shortening," says Tracy, "is for the companies launching or creating innovative products to have firm and open partnerships to drive the innovative product forward. Individual companies cannot go it alone, so partnerships with key suppliers and key customers are critical to the successful launch of an innovative product."

Mark Stromberg believes that this collaboration effort shouldn't focus only on the back-end participants but needs to include the front-end of the supply chain also. According to Stromberg, "The best way for equipment producers to meet product life-cycle demands is to partner closely with device makers throughout the development process. This is also a two-way street as device makers will need ever advanced tooling to meet their requirements and fully take advantage of the end-products revenue-maximizing period."

Narrowing it down some, everyone seems to agree that specifically equipment and material suppliers need to work together to solve industry problems and create innovative products. Tracy feels that it's very critical for companies to work together saying, "Without strong partnerships, the full advantage of launching an innovative product may be missed or a critical criteria overlooked. From a materials technology standpoint, the materials suppliers need to be involved in the process to assure an appropriate starting material is available. Given the complex interactions with various types of materials in semiconductor devices and packages, collaboration needs to involve suppliers of the other materials and equipment used to manufacture the device and assemble the package."

Papageorge further points out the potential downfalls of equipment and materials suppliers not working together by adding that, "If materials and equipment suppliers don't work closely together, the response of a material behavior to a set of process equipment can be off-base and therefore can be very frustrating to the user. This can slow down equipment and/or material qualification and may cause the innovative product to miss the market window of opportunity."

Stromberg emphasized that besides potential problems between material sets and equipment processes, delivery needs to be taken into consideration. "Delivery of materials and equipment in an efficient and coordinated way is absolutely essential to efficient production. If suppliers cannot provide that to manufacturers, they will have to look elsewhere for inputs. Collaboration throughout the supply chain is key to all product success but especially for new products. When dealing with innovative technology the market failures are magnified because of the limited if nonexistent secondary providers."

Even with all the current innovative products being introduced today, there are still many areas that will need to be addressed by future innovative products. Dan Tracy believes that, "The move to System-in-a-Package (SiP) and stacked-die technology clearly offers continued opportunities related to the processing of ultra-thin die and the assembly of stacked-die packages. Innovative solutions will deliver on the cost and reliability targets needed to satisfy this growth market."

Innovative products are being developed every day in our industry; products to solve current problems and products that will create a whole new set of problems for other companies along the supply chain. Despite some dark days and the potential for the unknown lurking around the corner, the semiconductor industry continues to work together to find just the right combination for success. As Stromberg put it, "As long as there is a steady supply of ever more demanding consumers and smart people who create products that the public will demand, the electronics and semiconductor industries will continue to innovate and collaborate to meet the needs of the industry and capture an ever-growing chunk of the economy.'

Wafer Level Packaging Makes Gains, But Isn't Quite 'Mainstream' Yet

### Julia Goldstein, Technical Editor Advanced Packaging Magazine

MEPTEC hosted its second Wafer Level Packaging (WLP) Symposium on August 19, featuring panel discussions in the areas of applications, equipment and processes, test and burn-in and strategies for industry collaboration. The goal of the symposium, according to co-chair Nick Leonardi, was to answer the question, "Where is wafer level globally today?" and provide insight into where the industry is headed.

Keynote speaker Tom Di Stefano described WLP as "one of the most important revolutions in electronics," noting that WLP is a method of producing chip scale packages (CSP) that is enabling the next wave of I/O density increase after surface mount technology (SMT). WLP today is mostly limited to small, low-pin-count chips for the cell phone market, but Di Stefano predicts the technology will take over in diverse applications in coming years - beginning with memory chips over the next year and eventually expanding into microprocessors and ASICs. Several technological issues need to be overcome, such as accommodating CTE mismatch between the chip and the PCB to provide a reliable connection for large die (die 3-mm or less on a side typically are not underfilled, but larger ones will need to be), and further development of microvia substrates for high-density wiring. Another key technological advance is moving power and grounds connections on-chip, which improves performance and minimizes the number of I/O that must be routed to a substrate.

One of the largest obstacles to widespread

adoption of WLP is the difficulty of test and burn-in, both from a technology and a cost perspective. Panelists discussed the tradeoffs between various test process flows and approaches. Two realistic options are placing singulated WLP devices in temporary carriers for burn-in and test or conducting wafer- level burn-in and test (WLBT) before dicing. As Carl Buck of Aehr Test Systems explained, WLBT has the advantage of being able to test a full wafer of die simultaneously, but has technical challenges, such as dissipating heat and maintaining a constant test temperature across a wafer, controlling the high contact forces required to make contact with tens of thousands of pins, and dealing with shorts on a die. The capital investment for WLBT makes it cost effective only for very high volumes of wafers, making temporary carriers the least costly solution in the short term. Jim Rhodes of Unisys discussed the use of boundary scan technologies, also known as JTAG, commonly used for board-level testing but applicable to WLP applications. The boundary scan approach provides built-in self-test (BIST) circuits on the die, simplifying the test process by limiting the number of contacts required on a wafer for WLBT. There is some debate in the industry, however, over whether burn-in should even be required. Larry Gilg, managing director of

# **MEPTEC Events Follow-up**

the Die Products Consortium, suggested that WLP burn-in should be avoided if possible, partly because changes in chip design and processing have made opens in circuits more common. Open circuits are more difficult to detect than shorts, making the time-consuming burn-in process less likely to weed out defective devices.

Equipment and Processes session chair Vivek Dutta described the various processes that exist for WLP, most of which involve solder bumped wafers, using a variety of methods to apply solder bumps and metal redistribution layers. Takeshi Wakabayashi explained Casio's process, which includes electroplated copper posts instead of relying solely on solder for interconnection. This approach allows for greater standoff height, important for reliability as die size increases. The panel included representatives from two industry consortia, ApiA (Manish Ranjan) and SECAP (Paul Siblerud), made up of equipment suppliers and designed to help companies interested in expanding into new technologies such as WLP. As new customers enter the WLP arena, clearly laid-out design and process rules are critical, explained Nikhil Kelkar

of National Semiconductor, "it's important to tell the customer what not to do."

The final session of the conference was devoted to strategies required to, as moderator William Chen of ASE stated, "make this great idea a reality." Panelists ranged from Robert Dickinson, whose company, California Micro Devices (CMD), has been involved in WLCSP since 1999 and is currently shipping over 70M units per quarter, to John Jackson of Analog Devices (ADI), a company just starting to look into WLP. While Dickinson noted the current availability of two sources for outsourcing of WLP assembly, Jackson is still struggling to convince those within ADI of the benefits of WLP technology. Mulugeta Abtew of Sanmina-SCI gave the board assemblers' perspective, with the message that component suppliers need to provide process and materials details, not merely ball pitch data, to help them solve problems such as cracking in WLP solder joints.

As to the question of whether WLP will be done by wafer fabricators or assembly subcontractors, the consensus was that foundries do not want to get into the WLP business and consider wafer bumping to be a back-end process. As Tom Chung of Maxim explained, the geometries required for post-passivation layers on wafers are much larger than those used in wafer fab processes, making WLP processing much more attractive to packaging houses than to wafer foundries. ASE is aggressively pursuing WLP, and Amkor has positioned itself in the market with the acquisition of Unitive. John Hunt of ASE emphasized the necessity of working closely with both customers and suppliers, especially since "very few of the designs we get are what we could call standard." Standardization is a complicated issue, since the die defines the package.

Processes vary tremendously, with, for example, each licensee of Flip Chip International's WLP process having their own variations. While progress has been made in the two years since MEPTEC's first WLP Symposium, it may still be awhile before WLP becomes a mainstream technology.

# UTC

System in Package

DRAM Stack

# UltraTera Corporation

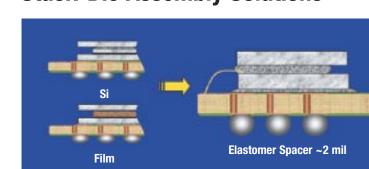

# **Stack-Die Assembly Solutions**

### **Multiple Any-Size Die Stacking**

UltraTera Corporation (UTC) has developed a patented portfolio of materials and processes that enables the thinnest multi-die stacking wire-bonded solutions. The dieattach material is selectively applied with our 3D stencil-printing process, while the die stack is encapsulated with traditional molding automated equipment and materials.

UltraTera stack-die/SiP portfolio includes the unique capability to stack on top of silicon dice with centerline of bond pads, enabling compelling solutions for SiP with standard DRAM components.

UltraTera provides full in-house package development and volume production, including laminate substrate design services.

- Flexibility in stacking order, easier routing

Thinnest spacing between dice

In-house wafer thinning capability to 50µm

- Low profile wire bonding

Unlimited overhang capability

#### Taiwan Headquarters

No.2 Li Hsin Road 3, Science-Based Ind. Park Hsinchu, Taiwan, ROC Mr. Sam Au +886 3 578-8780 x6610 Sam\_Au@utc.com.tw California Office 46848 Lakeview Boulevard Fremont, CA 94538 Mr. Emilio Salvioni 510 354-6683 esalvioni@utca.com Korea - Seoul Office

601, #945-15, Janghak Foundation Bldg., Daechi-Dong Gangnam-Gu, Seoul, Korea Mr. Anthony Roh +82 2 557-4277 okroh@utckorea.com

# Industry Analysis

# Semiconductor Utilization Has Peaked

Jim Walker Principal Analyst Semiconductor Packaging and Assembly Service Gartner Dataquest

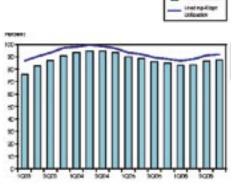

Worldwide semiconductor wafer fab utilization was down slightly in Q3 going into Q4 from the 95 percent at the end of the first half of 2004, as wafer manufacturing increased to keep pace with higher demand for semiconductors. While leading-edge utilization for wafer fab exceeded 99 percent going into the third quarter, end-user demand softened slightly, and semiconductor inventories began to rise. In response, semiconductor manufacturers announced production cutbacks, which in many cases were reductions in planned capacity increases. As a result, Gartner Dataquest forecasts continued softening of utilization rates in the fourth quarter of 2004. Going into next year, semiconductor demand growth will slow to the mid-single-digit realm, as new capacity comes online driven by the surge of already existing equipment shipments for 2004. Accordingly, utilization rates for both front end and back end will continue to decline for 2005 through mid-2006, as semiconductor manufacturers balance between adding new capacity and meeting market demand.

For front end manufacturing, wafer fab capacity growth has been a result of semiconductor manufacturers' sharply increasing their spending in the first and second quarters of 2004. New equipment shipments were up sharply, but the equipment book-to-bill ratio has dropped close to unity for the period. Shipments for the remainder of the year will not increase over current rates on a quarterly basis, and capacity growth will continue to lead

demand slightly through 2004 and 2005. This will cause leading-edge utilization rates to drop from their extremely high 99 percent level to the more desirable high-80 percent to low-90 percent range - a level that gives fab managers the needed flexibility to tailor production to demand in the most efficient manner. Overall utilization rates will remain in the 85 percent to 90 percent range through 2005, before dropping into the mid-to-low-80 percent range, where they will remain through the first half of 2006. Rates will begin to edge upward in the second half of 2006 as demand increases. Figure 1 shows expected fab utilization rates through 2006.

Turning to the back end, worldwide semiconductor packaging and assembly utilization was relatively tight for the first half of 2004 However, by the end of Q3, packaging utilization rates for the overall industry have eased toward 85 percent. Leading-edge utilization — defined as ball grid array (BGA), chip scale package (CSP), and flip-chip packaging and processes — has decreased to approximately 90 percent. For the first half of 2005, we see further moderation in utilization rates, dropping to the low to mid 80's.

Capacity had been tight earlier in the year because of the major transition and adoption of the lead-frame-based leadless packages. These quad flatpack, no leads (QFN), small outline, no leads (SON) and bumpless chip carrier (BCC) variations of CSPs are being used in wireless and portable product applications as replacements for the larger, more mature smalloutline integrated circuit (IC) and lowerlead-count quad flat packages. In addition flip chip, system-in-a-package and 3-D stacked package capacity was tight. Now, as Q4 is underway, we will continue to see a moderation in the back end services and equipment markets.

Figure 1. Expected fab utilization rates through 2006.

aging/Assembly and Test equipment), the investment cycle has matured faster and peaked sooner than for wafer fabrication equipment. Because advanced packaging and overall device demand have been growing so significantly throughout the past year and a half, capacity tightened as the back end market continued its rapid growth into the first half of 2004. In many cases, capital spending announcements were revised upward and continued to give way to orders. Then late in the second quarter macroeconomic growth began to soften. This slow down, coupled with several cautious semiconductor industry earnings calls, forced many SATS makers to review their previously aggressive spending plans, resulting in the delaying of equipment deliveries.

Following last year's strong gains of 30 percent growth, we estimate additional growth at approximately 50 percent for backend equipment in 2004. As in the past, the major growth area for PAE equipment usage will be in Asia/Pacific. PAE consumption in the Asia/Pacific region will grow nearly 51 percent this year. For 2005, we see a contraction in the packaging equipment market, with a contraction of 14 percent.

Thus, as enter Q4, our most-likely forecast for the global semiconductor market will be an increase of near 27 percent in revenue in 2004. But the outlook for 2005 is much more pessimistic. Revenue growth in 2005 will be in the single digits – approximately 7 to 9 percent, with the possibility of even slower growth depending upon how robust the holiday season is. The industry's period of supply shortages is coming to an end. All the main supply and demand factors point to a relative increase of supply in 2005, which will favor buyers, not sellers, and won't be conducive to strong revenue growth. ◆

In the back end equipment area (Pack-

# **Profit From Our Experience**

# Lower Costs, Lower Risks, Higher Profits

ASAT's 15 years of experience in advanced semiconductor packaging and test is a valuable asset our customers can bank on. With a portfolio of leading-edge packaging technologies and exceptional customer service, ASAT has become the standard bearer for performance and reliability. The opening of ASAT's new state-of-the-art manufacturing facility – strategically located in Southern China—demonstrates our ability to continue to set benchmarks that define the industry.

We're ready to make a commitment to you, so come make a commitment to us and profit from our experience.

www.asat.com 800-788-ASAT

# **University News**

# North Dakota State University

New Microelectronics Team on the High Plains

Gregory J. McCarthy, Director, Center for Nanoscale Science and Engineering

here is a new university entity with some unique electronics capabilities out on the high plains of North Dakota. In 2001, North Dakota State University (NDSU), located in Fargo, joined with DoD's Defense Microelectronics Activity to launch a Center of Excellence (COE) for microsensor design and manufacturing. This COE is a key component of an NDSU strategic initiative to promote large-scale multidisciplinary government and industry research programs, enabled by new facilities in the NDSU Research and Technology Park (RTP).

Through this microelectronics COE, which in 2002 was incorporated in its new Center for Nanoscale Science and Engineering (CNSE), NDSU has established expertise in design of wireless, low-power, miniaturized electronics, and fabrication using technologies licensed and transferred from industry-leaders. The Center has developed a broad-based portfolio of basic and applied research supported by DoD and other U.S. Government agencies and industry. In addition to microelectronics, CNSE core competencies include protective coatings (soft and hard) and polymer materials discovery, synthesis and optimization. CNSE houses the largest polymer-focused Combinatorial Materials Science program and tool base at any U.S. university. Future plans are to bring these specializations to bear on electronics failure analysis, packaging and ruggedization

In 2004, CNSE moved into the new R&D facility in the RTP. Research 2 has a unique

suite of licensed technologies and tools for electronics design and fabrication, focused currently on microsensors and wireless communication applications. A 15,000 square foot wing houses three bays (2,300sf) of Class 100 and three bays (4,250sf) of Class 10,000 cleanrooms, equipped with more than \$5M of fabrication and characterization tools. Other specialized space includes 8,750sf of materials chemistry and nanoscience laboratories, and 4,650sf of engineering design, testing, equipment development and back-end fabrication laboratories.

Uniqueness in electronics design and prototype fabrication comes from the combination of a suite of modern electronics design and manufacturing tools with two microelectronics technologies licensed from R&D partners Alien Technology and Tessera Technologies. Alien, headquartered in Silicon

Figure 1. These Alien Technology NanoBlock ICs measuring 77 and 350 micrometers on an edge are shown against the Denver (D) mint mark on a Dime. (Photo by Dr. Mark Hadley, Alien Technology Corporation)

Research 2 in the Research and Technology Park on the NDSU campus houses the microelectronics design and fabrication Center of Excellence. (Photo by Dan Koeck, NDSU Publication Services)

Valley, recently opened a Fargo branch that assembles Radio Frequency Identification tags, and will build its first manufacturing plant in the NDSU Research and Technology Park in 2005. NDSU is the only university licensed to practice Alien's NanoBlock<sup>®</sup> IC and Fluidic Self Assembly (FSA<sup>®</sup>) technology. Tessera Technologies is a leading company in miniaturization technology (Chip Scale Packaging and System-in-a-Package) and licenses technology utilized by most manufacturers of cell phones, PDAs, computers, and high-capacity memory.

By mid-2005 these technologies will have been fully transferred to NDSU, and CNSE will have an impressive suite of electronics miniaturization and fabrication capabilities:

• Two high mix/low volume surface mount technology (SMT) prototype lines that are capable of fabricating a broad range of electronic systems, analog or digital, and rigid or flexible.

• Fully capable Chip Scale Package (CSP) prototype line that is capable of producing conventional or advanced packages such as BGA, micro-BGA, and system-in-a-packages.

• Fluidic Self Assembly (FSA) line that is uniquely suited for the rapid assembly of integrated circuit chips [Figure 1] on a flex

# **University News**

### Figure 2. Research Engineer Bernd Scholz utilizing the reactive ion etcher in a process step of NanoBlock fabrication.

(Photo by Dan Koeck, NDSU Publication Services)

ible substrate for the fabrication of miniaturized electronics suitable for sensor and many other applications. This front-end, high-volume electronics fabrication technology is proprietary to Alien Technology, a leading manufacturer of EPC global-compliant radio frequency identification (RFID) logistical tags. In FSA, very small (typically <1mm square) ICs with tailored geometries are suspended in fluid and flowed across a flexible substrate in which precisely placed receptors have been embossed. These ICs constitute the circuit elements of the target devices. The technology practiced by NDSU includes design of the NanoBlock ASICs, release of the NanoBlocks from wafers [Figure 2], and interconnect metallization by thin film or thick film methodology.

At the receiving end of these transfers are twelve CNSE engineers and technicians with more than 150 cumulative years of industry experience with companies like Intel, Micron, Motorola, Honeywell, Imation, Texas Instruments, Hutchinson, Rockwell-Collins, and Lucent. CNSE's engineers specialize in ultra-low power, wireless, modular, reconfigurable, and scalable electronics, applied to application-specific integrated circuits (ASICs) and circuits for wireless microsensors.

CNSE forms an interface between faculty research and government and industrial customers for this research. Faculty from the Departments of Coatings & Polymeric Materials, Chemistry & Molecular Biology (College of Science and Mathematics), and Electrical, Mechanical, Industrial & Manufacturing, and Civil Engineering (College of Engineering and Architecture) were instrumental in launching and developing CNSE. Faculty and faculty-CNSE teams are constantly opening up and funding new research areas that utilize CNSE's unique capabilities. Prominent among its team research are projects on advanced FSA processes, direct write interconnect of ICs, and development of polymer materials suitable for FSA processes.

Currently, 65 NDSU students and faculty work with 35 science and engineering staff on government and industry grants and contracts. [Figure 3] In addition to the experience of working on cutting-edge projects in state-of-the-art facilities, students benefit from graduate and undergraduate research assistantships that help finance their education.

The Center's principal electronics efforts address the need for low-cost sensors with motion, acoustic, seismic, magnetic, and other modalities. Wireless integration of these

sensors, combined with cost-cutting designs and advanced high-density electronic packaging and manufacturing technologies, permit overcoming size and cost limitations in the military's current unattended ground sensors. Food safety, transportation of highvalue goods and perishables, and asset protection are among the many civilian applications for CNSE's sensors.

In support of its sensor programs, CNSE has developed the Tenali processor, the first custom Application Specific Integrated Circuit (ASIC) designed in North Dakota. The chip was architected by Faculty Associate Dr. Joel Jorgenson of the Electrical and Computer Engineering Department, and designed by ECE students working with CNSE engineers. The name honors Tenali, India, the hometown of one of these students. Three components, a computer, a clock circuit, and storage memory, have been integrated into Figure 3. Electrical and Computer Engineering Graduate Research Assistant Kumar Mangipudi prepares the Tenali NanoBlock IC for characterization. (Photo by Dan Koeck, NDSU Publication Services)

one chip for low-cost, low-power sensor applications utilizing the Alien Technology NanoBlock form factor [Figure 1].

For more information about NDSU electronics capabilities go to www.ndsu.edu/cnse and http://www.ndsu.edu/ndsu/academic/ factsheets/eng\_arch/electrl.shtml, or contact: Karen White, Center for Nanoscale Science and Engineering, 1805 NDSU Research Park Drive, Fargo, ND 58102 701-231-5828 ◆

This material is based on research sponsored by the Defense Microelectronics Activity (DMEA) under agreement number H94003-04-2-0406. The United States Government is authorized to reproduce and distribute reprints for Government purposes, notwithstanding any copyright notation thereon.

# STATS ChipPAC Appoints Chief Strategy Officer

SINGAPORE and UNITED STATES – STATS ChipPAC Ltd. has announced the appointment of Scott J. Jewler as Chief Strategy Officer.

Reporting directly to STATS ChipPAC's President and CEO, Jewler will have overall responsibility for product line management as well as market and technology strategy. In his capacity as Chief Strategy Officer, Jewler will help define STATS ChipPAC's business focus and strategic direction in the various geographic and end markets served. He will ensure effective positioning of STATS ChipPAC's products and services to benefit from technology trends, customer engagements and corporate development.

"I am delighted to welcome Scott to STATS ChipPAC," said Tan Lay Koon, STATS ChipPAC's President and CEO. "Scott brings with him many years of outsourced semiconductor assembly and test experience that is very relevant to STATS ChipPAC. He has more than 15 years of experience managing business line P&L and driving operational efficiency in our industry. His past experience in sales, marketing, manufacturing and technology will be invaluable to STATS ChipPAC as we drive towards profitable growth and position ourselves as one of the world's leading and largest test and assembly providers."

Jewler joins STATS ChipPAC from Amkor Technology Inc. where he held various senior management positions including Senior Vice President, Assembly Business Unit and Vice President, Laminate Products. Most recently, Jewler served as President of Amkor Technology Taiwan where he held P&L responsibility for Amkor's Taiwan operations including all sales, marketing, manufacturing, business development and manufacturing support activities. Prior to joining Amkor, he was a Senior Process Engineer and Equipment Engineering Manager with Mitsubishi Semiconductor America, Inc.

Further information is available at www. statschippac.com

# CMC Adds Dr. Rudy Enck to Technical Staff for Thermal and Electrical Measurements

TEMPE, AZ - CMC Interconnect Technologies, a provider of outsourced analytical, reliability and technical consulting services to the semiconductor and electronics industries, has announced the addition of industry veteran Dr. Rudy Enck to the technical staff. "Dr. Enck is a key addition to our company", stated Dr. Jonathan Harris, CMC President, noting, "Rudy will significantly increase our capabilities in the areas of thermal and electrical measurement". CMC's capabilities include thermal characterization of materials and interfaces utilizing the Laser Flash Thermal Diffusivity System. Electrical characterization includes dielectric measurements up to 26 Giga-hertz, as well as, dielectric breakdown voltage (dielectric strength) of insulating materials.

CMC Interconnect Technologies, which is located in the ASU Research Park, services a broad range of customers, with involvement in various industry organizations to define requirements for packaging and material analysis, reliability and characterization. "MEPTEC is an excellent venue for CMC exposure in the industry," noted Nicholas Leonardi, VP Sales and Marketing, adding, "especially with the national and global focus of our company in characterization". Corporate vision is to be the premier stateof-the-art analytical services provider in packaging and materials.

For more information visit the CMC web site at www.CMCinterconnect.com.

## DeWeyl Tool Company Names David Pasfield Sales Director

PETALUMA, CA – DeWeyl Tool Company is pleased to announce the addition of David Pasfield as Sales Director, assigned to Global Sales and Marketing responsibilities.

Graduating from California Polytechnic State University, San Luis Obispo, with a

BS in Industrial Engineering, David has over 14 years of back-end assembly & materials experience having previously held Sales and Marketing positions with Kyocera, Small Precision Tools (SPT), Newport (MRSI) and RJR Polymers, Inc. David can be contacted at dpasfield@deweyl.com, 707-782-9257.

# Silicon Bandwidth, Inc. Names Leo Yuan to Technical Advisory Board

### Former Sun Microsystems "Distinguished Engineer" accepts position

SAN JOSE, CA – Silicon Bandwidth, Inc., a leading innovator of high-performance, low-cost interconnect solutions for computing and communications platforms, has announced that Leo Yuan has accepted a position as a member of its Advisory Board.

Mr. Yuan, until most recently a Distinguished Engineer and Manager in System Technology, Enterprise Server Products at Sun Microsystems, Inc., has been named to the five-year-old San Jose-based company's Technical Advisory Board. At Sun, Mr. Yuan oversaw the design and development of enterprise multi-processor (SMP) server systems. During his fifteen years there, he was instrumental in the design and delivery of three generations of Sun's Enterprise Server Systems, and was recently working on the fourth generation, a Gbps I/O, IB SERDES, still in development.

Previous to Sun, he held positions with MIPS, Inc.; Cydrome, Inc.; Tandem Computers; Trilogy Systems; and IBM's General Technology Division. He co-invented an industry-first commercial GTL bus system (GTL became JEDEC standard and later Intel adopted the PC bus). Mr. Yuan has been involved in the design of ASICs, I/O timing and system-level bus timing, electrical design of backplane and system board, parallel optical interconnect, system clock distribution and skew control (PLL) on backplane, board, and ASICs, high speed analog circuit and I/O testing, manufacturing test specifications, system-to-tester correlation, vendor sourcing strategy, and system thermal design, among others.

The author or co-author of more than ten patents, he earned a Bachelor of Science degree in Electrical Engineering from National Cheng-Kung University, Taiwan, a Masters in EE from State University of New York at Buffalo, and he attended the MBA program at University of Phoenix, San Jose. He has published or co-authored a number of technical papers concerning systems design, has been a guest speaker at

Stanford University, and has been repeatedly honored with industry awards, including Sun Microsystems President's Award in 1998.

Visit the Silicon Bandwidth website at www.siliconbandwidth.com for more information.

# STATS ChipPAC Appoints Chief Operating Officer

SINGAPORE and UNITED STATES – STATS ChipPAC Ltd. has announced the appointment of Wan Choong Hoe as Chief Operating Officer.

Reporting directly to the President and Chief Executive Officer of STATS Chip-PAC, Wan's mission is to build the industry leading world-class manufacturing organization with best-in-class execution and service mindset across all plants. He will also drive a "one look and one experience" standard in all our plants for our customers.

"I am delighted to welcome Choong Hoe to STATS ChipPAC," said Tan Lay Koon, STATS ChipPAC's President and CEO. "Choong Hoe's 25+ years of manufacturing experience will provide significant and relevant strengths to the leadership team of STATS ChipPAC, as we implement strategies to drive operational excellence in our worldwide manufacturing plants. Choong Hoe has been very successful in manufacturing start-ups, cost reduction, improved operational metrics, building strong teams, and implementing Six Sigma. His extensive operational background in assembly, test, planning, process/product engineering and maintenance functions make Choong Hoe ideally suited to ensure that all STATS Chip-PAC operations incorporate industry best practices while remaining agile and responsive to our customers' requirements. He will help ensure that we develop and motivate a strong operational leadership team and that our operational performance metrics deliver superior results in the market place."

Wan joins STATS ChipPAC from National Semiconductor Manufacturer Singapore Pte. Ltd. where he held various senior management positions such as Vice President, Managing Director and Director of Operations & QRA. Most recently, Wan served as Vice President & Managing Director, responsible for Singapore and China operations. Additionally, Wan led the startup of the Suzhou/China Plant and served as Chairman of the Gintic Research Institute Management Board. Prior to joining National Semiconductor, Wan held numerous management and engineering positions at Texas Instruments Singapore Pte. Ltd.

Wan holds an Electrical and Electronics Engineering degree from the University of Singapore and resides with his family in Singapore.

# Silicon Bandwidth, Inc. Grows Sales Force

# Industry veterans accept positions

SAN JOSE, CA – Silicon Bandwidth, Inc. announced the expansion of their sales and marketing force with the naming of Mr. Greg Wadas and Ms. Robynn Ridley as Directors of Sales. Both Mr. Wadas and Ms. Ridley join the five-year-old San Jose company with extensive experience in interconnect and semiconductor technologies, the basis of the leading-edge products Silicon Bandwidth, Inc. has developed.

Mr. Wadas has more than twenty years' sales experience in Silicon Valley. He has been a manufacturers' rep and the owner of a northern California rep company. He comes to Silicon Bandwidth after nine years as an Account Executive with Arrow Electronics, where he received several Presidents' Club awards. Additionally he has the distinction of having been named First in Sales at every company for whom he has worked during his career.

Ms. Ridley was most recently with Quantum Coefficient, Inc. for four years, where she had account responsibility for design-in and support of ASICs, MCU, integrated connectors, power supplies, and passive-related components at major OEM's. Ms Ridley began her career at Spectra Electronics, a distributor of electromechanical components, where in eight years she moved from inside sales to Sales Manager. She holds a Bachelors Degree in Marketing from San Jose State.

Silicon Bandwidth President and CEO Ajit Medhekar said, "At Silicon Bandwidth,

we've moved into a new phase in corporate development. With our C Round of Funding completed, we're expanding sales and marketing efforts to service the growing number of accounts who are attracted by our systemwide approach to improving signal integrity and time-to-market. We've attracted some of the area's outstanding talents from the engineering and manufacturing pools, and now we're adding some equally talented sales people to service our customers. Greg and Robynn bring technical know-how and outstanding customer care to complement our innovative product solutions."

Visit the Silicon Bandwidth website at www.siliconbandwidth.com for more information.

# Advanced Interconnect Technologies Chosen by Anadigics for Package Assembly Services

SINGAPORE – Advanced Interconnect Technologies (AIT) has announced that Anadigics has selected AIT's Land Grid Array (LGA) package for the CHP1237 InGaP HBT power amplifier (PA). AIT was chosen by Anadigics because of their ability to deliver a package solution that meets the stringent quality requirements for the highly integrated CHP1237. Additionally, AIT was able to meet their requirement for a package with a reduced footprint and ultra-thin profile.

"Anadigics recognizes AIT as a quality supplier of land grid array package technology," said Dave Coller, vice president of operations for Anadigics, Inc. "We continue to develop strong relationships throughout the supply chain in order to ensure that our customers receive the highest levels of quality in the industry."

"With our expertise in advanced packaging solutions, we are raising the bar in performance, compatibility and physical design," said Mike McKerreghan, chief operating officer at AIT. "Our product offerings are designed to provide the market with competitive solutions that can deliver an array of competitive advantages from size, power and performance. AIT's continued long term strategy has been to offer packaging solutions that enable an array of superior performance advantages."

With approximately 3,600 employees worldwide, AIT has factory locations in Batam, Indonesia and Sunnyvale, Calif. The company is headquartered in Singapore.

For more information about the company, its products and services please visit their website at www.aithome.com.

# K&S Announces Grand Opening of New Wafer Test Manufacturing Facility in Taiwan

WILLOW GROVE, PA – Kulicke & Soffa Industries, Inc. held a grand opening event on October 15, 2004 at its new state-of-theart probe card manufacturing facility located in Hsin Chu, Taiwan.

With a floor size of over 2,400 square meters, this new facility has full manufacturing capability for all types of enhanced cantilever probe cards. The facility can produce optimized probe designs for each customer's application. Additionally, this new K&S plant can handle probe wire diameters from 75 to 250 microns, along with very fine pitch probing.

Oded Lendner, vice president, K&S worldwide operations, said, "Our objective for the plant is to provide advanced probe card manufacturing technology to meet the growing trends and expanding markets for IC testing in Taiwan. Additionally, this new factory will follow our copy exact manufacturing model to match the K&S test quality and performance that we have achieved in other expanding test markets around the globe."

Also, this new facility is strategically working with key Taiwan-based customers for cantilever probe cards, and the Company plans to increase its presence in the vertical probe card market. The Hsin Chu facility also has a full repair center for vertical, cobra technology probe cards and has announced plans for vertical, cobra technology probe card assembly-repair capabilities by mid-2005.

Jack Belani, K&S vice president of marketing and business units, commented, "Our fast design capability, combined with our superior application support and manufacturing, will allow us to better serve our growing customer base in Taiwan." He continued, "We are in the final stages of building our Hsin Chu after-sales support center to provide enhanced repair and rebuild services."

For more information visit the K&S web site at www.kns.com.

# STATS ChipPAC Achieves ISO/TS16949 Certification in Singapore

Supporting quality goal of One Look, One Experience

SINGAPORE and UNITED STATES – STATS ChipPAC Ltd. has announced the company's Singapore operation has been awarded ISO/TS 16949:2002 certification by PSB Certification Pte Ltd. ISO/TS 16949:2002 is considered to be the most comprehensive quality standard in the industry today. This certification marks the fifth STATS ChipPAC operation to have achieved this level of quality management.

Developed by the International Automotive Task Force (IATF) and Japan Automobile Manufacturers' Association, Inc. (JAMA), in conjunction with the International Organization for Standardization (ISO), ISO/TS 16949:2002 specifies quality system requirements for the design, development, production, installation and servicing of automotive related products. It aligns existing American (QS-9000), German (VDA6.1), French (EAQF) and Italian (AVSQ) automotive quality systems standards within the global automotive industry to provide a single certification standard and common approach to quality management systems.

With ISO/TS 16949:2002 certification of the Singapore operation, STATS Chip-PAC is the first semiconductor assembly and test service provider to achieve certification companywide. STATS ChipPAC is certified in South Korea, Malaysia, China, Taiwan and Singapore.

# Honeywell Acquires Mitsubishi's Stake in GEM Microelectronic Materials

MORRIS TOWNSHIP, NJ – Honeywell has announced that it has acquired Mitsubishi Chemical America's 40 percent stake in GEM Microelectronics Materials, giving Honeywell sole ownership of the venture, which manufactures chemicals for the semiconductor industry.

Financial terms of the deal were not disclosed. GEM Microelectronics Materials was formed in 2001 when Mitsubishi and Honeywell combined their wet-process chemicals businesses. The business has annual revenues of \$40 million.

The business' core competency is its ultra-high purity straight, wet-etch and cleaning chemistries. GEM's focus on quality is critical to semiconductor manufacturers' processes especially with wet cleaning chemistries, which are used in nearly every stage of semiconductor production. The business has also recently expanded its product portfolio to include performance cleans, ultra-high selective etchants and wafer-thinning products designed to meet specific customer needs.

The GEM Microelectronics Materials business has headquarters and manufacturing facilities in Chandler, Arizona, as well as manufacturing operations in Bryan, and Mansfield, Texas. Honeywell intends to discontinue use of the GEM name and market the products under its Honeywell Electronic Materials business, which makes a wide range of materials for the semiconductor industry based upon its expertise in both chemistry and metallurgy. Supplying to both the "front-end" (wafer production) and "back- end" (packaging), Honeywell's offerings can be found on the technology roadmaps of most of the top manufacturers in the semiconductor industry. Honeywell Electronic Materials employs approximately 1,200 people.

For additional information, please visit www.honeywell.com.

# Carsem Clarifies Patent Litigation Statements

SCOTTS VALLEY, CA – Carsem has announced that there appears to be some conflicting interpretations of the ITC ruling in the action that Amkor brought against Carsem.

The facts of the decision are as follows:

1. There were a total of 21 claims asserted against Carsem. Every claim asserted against Carsem was found EITHER invalid, not infringed, or both.

2. While it is true that there were 4 claims that were found to be infringed, those same 4 claims were found to be INVALID. As a result and by law, an invalid claim cannot be infringed.

3. There were also 4 other, different claims that were found to be VALID claims but that Carsem was found to have NOT IN-FRINGED.

4. The Administrative Law Judge determined that NO VIOLATION of Section 337 of the Tariff Act of 1930 was present. To be clear, this means that Carsem PREVAILED on all aspects of this case. As a result of this decision, there will be no injunction imposed on the importation of Carsem assembled MLP products into the United States.

On the request to have the full commission review the ruling; this is a logical step for either or both sides to take after the initial

determination is issued and is almost a prerequisite to the formal appeal process generally sought in the Court of Appeals for the Federal Circuit after the final ruling is issued by the Commission.

Carsem is a member of the Hong Leong Group with factories located in Ipoh, Malaysia, Suzhou, China and sales offices across the USA, plus the UK. Carsem, Inc. sales headquarters is located at 269 Mt. Hermon Road, Suite 104, Scotts Valley, CA 95066, phone (831) 438-6861, fax (831) 438-6863, web site: www.carsem.com.

# Rohm and Haas Electronic Materials and UP Chemical Company Announce Partnership to Supply High-K ALD Precursors

MARLBOROUGH, MA and PYEONG-TAEK, KOREA – Rohm and Haas Electronic Materials and UP Chemical Company have announced the commercial availability of Hi-k Grade aluminum and hafnium precursors for the production of high-k dielectric films.

The two companies will initially focus on supplying Hi-k Grade aluminum and hafnium precursors to global markets, but are also uniquely positioned to expand their precursor line to support future CVD and ALD technologies. Rohm and Haas Electronic Materials will use UP Chemical Company's proprietary technology to manufacture Hik Grade products. Rohm and Haas Electronic Materials' manufacturing processes are meticulously qualified to the exacting manufacturing standards of UP Chemical Company. The two companies will coordinate their quality assurance efforts to ensure a smooth and transparent availability of Hi-k Grade precursors worldwide.

This announcement builds on the 1998 Investment Agreement between Rohm and Haas and UP Chemical that established Rohm and Haas as the supplier of these technologies to the global market outside Korea. "We realized the potential benefits of UP Chemical Company's patented and proprietary precursors early on and strategically invested in this Korean company" said Dr. Yi Hyon Paik, President, Rohm and Haas Electronic Materials Microelectronic Technologies. "Rohm and Haas' investment in UP Chemical Company fostered the development of novel CVD materials for the Korean market where the use of aluminum and hafnium precursors is growing rapidly" continued Dr. Paik.

Rohm and Haas Electronic Materials, through its Microelectronic Technologies business unit, is a leading supplier of highpurity MOCVD precursors to the compound semiconductor industry. Emphasizing product consistency and quality, which is evident by its ISO-9001-2000 certification, the company has developed a unique combination of patented and proprietary purification processes for its precursors. UP Chemical Company specializes in DRAM and high-k gate dielectric precursors based on aluminum, hafnium, tantalum and titanium.

Additional information is available at http://electronicmaterials.rohmhaas.com.

# Carsem's China Factory Holds Grand Opening Ceremony

SCOTTS VALLEY, CA – Carsem recently held their official Grand Opening Ceremony for the Carsem-Suzhou factory. The 172K sq. ft. (16K sq. m.) facility is located in the Suzhou Industrial Park, which is in the province of Jiangsu 50 miles (80 km) west of Shanghai.

The Grand Opening was attended by executives from several of Carsem's customers including Allegro, Elmos, Infineon, Micro Analog Systems, National Semiconductor, Semtech, Skyworks, STMicroelectronics, and Zarlink.

Among the executives in attendance from Carsem were Mr. David Comley, Group Managing Director, S.W Woo, Chief Operating Officer, and T.W. Hee, General Manager of Carsem-Suzhou. Carsem is a member company of Malaysian Pacific Industries, which is part of the Hong Leong Group. Representing Hong Leong was Mr. Kwek Leng San, Executive Chairman of Malaysian Pacific Industries and representing the Suzhou Industrial Park were Mr. Wang Ming, Standing Member of Jiangsu Provincial Party Committee, Secretary of Suzhou Municipal Party Committee and Mr. Wang Jin Hua, Deputy Secretary of Suzhou Municipal Party Committee, Chairman of Suzhou Industrial Park Administration Committee.

The Carsem-Suzhou factory began shipping production volumes in July this year and currently offers full turnkey assembly and test services for the production of the entire range of MLPQ (Quad) and MLPD (Dual) packages, which is a saw-singulated version of QFN & SON compliant packages per JEDEC's MO220 and MO229 standard's.

For more information visit the Carsem web site at www.carsem.com. For more information about the Hong Leong Group, go to www.hongleong.com.

# Printer's Unique Auto Unload Feature Eliminates Need for PCB Handling Equipment

HUNTINGTON BEACH, CA - Surface Mount Techniques' AUL2220 printer with auto unload saves money by reducing the need for PCB handling equipment, saves floor space, and brings greater flexibility to the SMT printing process. Its unique auto unload feature, developed exclusively by Surface Mount Techniques, eliminates substrate handling issues for high volume fine pitch production runs. This enhancement may also eliminate the need for expensive bare-board and magazine loaders. Allowing greater flexibility, the AuL2220 allows transport upstream automatically to the pick and place station. The AUL2220 can also be unloaded manually as well.

The AuL2220 is a stand alone, fully automatic, high precision printer with large capacity. It is equipped with Surface Mount Techniques' Accu-Lign Series 3 auto vision alignment with over 10,000 individual program file storage, and is equipped with adjustable magnetic PCB support, programmable squeegee drive, pressure, stroke and speed. The AuL also features an understencil wiper module (with vacuum), and motorized or programmable conveyor width adjustment. A Pentium/Windows® or Windows NT<sup>™</sup> based single processor controlled operating system offers the simplicity of an interactive point and click graphical user interface. The AuL2220 has a large 20" x 23" print area and will accommodate both cast and welded tubular stencils as well.

Surface Mount Techniques is the second largest manufacturer of surface mount printing systems in North America, for more than 20 years providing the highest quality solder and adhesive printing equipment to the electronics industry. For more information, visit www.smtprinters.com or contact the company at 714-903-8100; Fax: +1-714-903-8897; E-Mail: surfmntteq@aol.com.

# Carsem Continues to Expand MLP (QFN) Capacity

SCOTTS VALLEY, CA - Carsem has announced that they will increase their capacity for the MLP (Micro Leadframe Package) family to a total of 155 million units per month. In September last year Carsem had a monthly capacity of 50 million in their Malaysian factories. Since then it has been increased to a current capacity of 90 million and by November this year the capacity will be ramped to 135 million. In addition, another 20 million is being added in the new Carsem-Suzhou factory, which is in the province of Jiangsu 50 miles (80 km) west of Shanghai. The total capacity is a combination of both saw and mechanical singulation technologies.

According to Paul Smith, Carsem's Director of Marketing, "Although this package still represents less than 5% of the IC packages assembled world wide it continues to be a very popular choice for many of the new generation devices, especially in the area of RF applications." Smith further stated, "The popularity is enhanced because of our ability to quickly provide new package designs utilizing our sister company Dynacraft, which is a major supplier of leadframes. This, combined with our saw singulation technology, allows us to significantly shorten the lead time in producing prototype parts and drastically reduces our customer's time to market.'

For more information visit the Carsem web site at www.carsem.com. For further information about Dynacraft see their web site at www.dynacraft.com.

## K&S Launches a New 3N Gold Wire for Superior Ball Reliability

WILLOW GROVE, PA – Kulicke & Soffa Industries, Inc. has just released a new Gold Bonding Wire entitled the Radix. This new K&S wire has been specifically engineered for higher intermetallic stability for improved reliability in the most demanding wire bonding applications.

"Many of our global customers have been asking for higher reliability without compromising lower electrical resistivity," states Dr. Ilan Hadar, K&S Vice President, Bonding Materials. "Radix wire gives customers the best of both worlds."

Radix bonding wire has shown superior reliability on a wide range of aluminum bond pad compositions and thicknesses. K&S offers a wide range of diameters, including wire sizes typically used in high-power applications.

"Radix provides customers with a total solution in wire bonding by offering high reliability over a large variety of wire diameters, including high-power applications," explains Jack Belani, Vice President of K&S Business Units and Marketing.

Additionally, this new bonding wire lowers hardness on free-air balls (FAB), which allows for bonding on sensitive devices structures like low-K dielectrics and bonding over active circuitry.

For data on the new Radix Gold Bonding Wire, visit www.kns.com.

# AIT Delivers New Etched Leadless Package Family for Next Generation Portable Consumer and R/F Wireless Applications

AIT leverages patented technology with high density, low cost package family

SINGAPORE - Advanced Interconnect Technologies (AIT) has announced the availability of new a family of Etched Leadless Packages (ELP) that delivers design flexibility, increased density and a reduced footprint. Based upon AIT's newly confirmed patented technology, the advanced ELP framework leverages AIT's world-class selective Etching process, allowing tight integration of multiple I/Os into a reduce area. These new members of AIT's leadframe based package family are available in three unique variations including: ELP (Etched Leadless Package), ELPF (Etched Leadless Package-Flip Chip) and ELGA (Etched Leadless Grid Array), allowing designers to chose a solution that best fits there system needs. The ELGA version is also the industry's most populated leadless package technology on the market today.