# Progress and Prospects of Heterogeneous Integration at DARPA

#### Daniel S. Green

U.S. Defense Advanced Research Projects Agency (DARPA) Arlington, VA

2016 Semiconductor Packaging Roadmap Symposium San Jose, CA

14 November 2016

#### Terminology:

InP = indium phosphide, GaN = gallium nitride, SiGe = silicon germanium, ABCS = antimonide-based compound semiconductor HBT = heterojunction bipolar transistor, HEMT = high electron mobility transistor, CMOS = complementary metal oxide semiconductor COSMOS = Compound Semiconductor Materials on Silicon

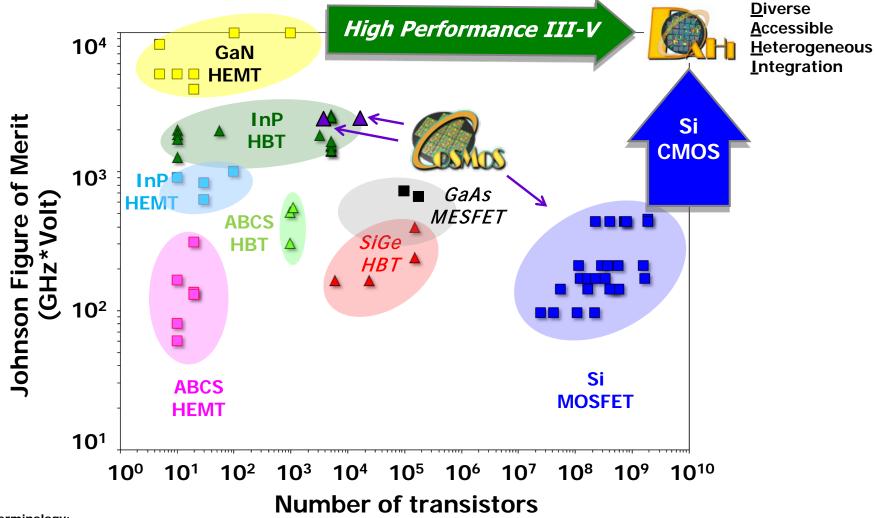

# Motivates a portfolio of investment

|                      |                       |                                                 | ←───      | device r                                      | materials                                         |                  | integration                       |

|----------------------|-----------------------|-------------------------------------------------|-----------|-----------------------------------------------|---------------------------------------------------|------------------|-----------------------------------|

| Parameter            | Why?                  | Unit                                            | Si        | GaAs                                          | InP <sup>1</sup>                                  | GaN <sup>2</sup> | COSMOS / DAHI                     |

| Electron<br>Mobility | Carrier<br>velocity   | 10 <sup>3</sup> cm²/V⋅s                         | 1.4       | 8.5                                           | 12                                                | <1               | InP                               |

| V <sub>peak</sub>    | Transit time          | 10 <sup>7</sup> cm/s                            | 1         | 2                                             | 2.5                                               | 2.5              | InP / GaN                         |

| Е <sub>вк</sub>      | Voltage<br>swing      | 10⁵ V/cm                                        | 5.7       | 6.4                                           | 4                                                 | 40               | GaN                               |

| E <sub>g</sub>       | Charge<br>density     | eV                                              | 1.12      | 1.42                                          | 0.74                                              | 3.4              | GaN                               |

| κ                    | Heat<br>removal       | W∕cm∙K                                          | 1.3       | 0.5                                           | 0.05                                              | 2.9              | GaN / Si                          |

| Maturity             | Circuit<br>complexity |                                                 | Excellent | Good                                          | ок                                                | Limited          | Si + GaN + InP<br>(heterogeneous) |

| DAR                  | PA Invest             | ment                                            | ~\$100M   | ~\$600M                                       | ~\$200M                                           | ~\$300M          | ~\$180M                           |

| Programs             |                       | Portions of<br>GRATE,<br>ADRT, LPE,<br>and TEAM | МІМІС     | SWIFT,<br>TFAST, THz<br>Electronics,<br>SMART | GaN Title<br>III, WBGS-<br>RF, NEXT,<br>MPC, NJTT | COSMOS, DAHI     |                                   |

#### Materials and device parameters favor a diversity of semiconductors

1. InGaAs channel

2. SiC substrate

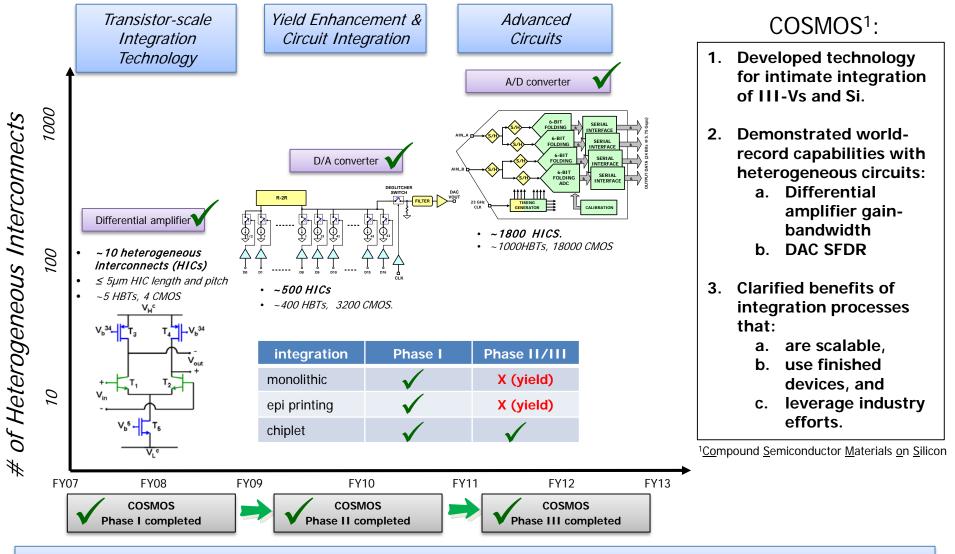

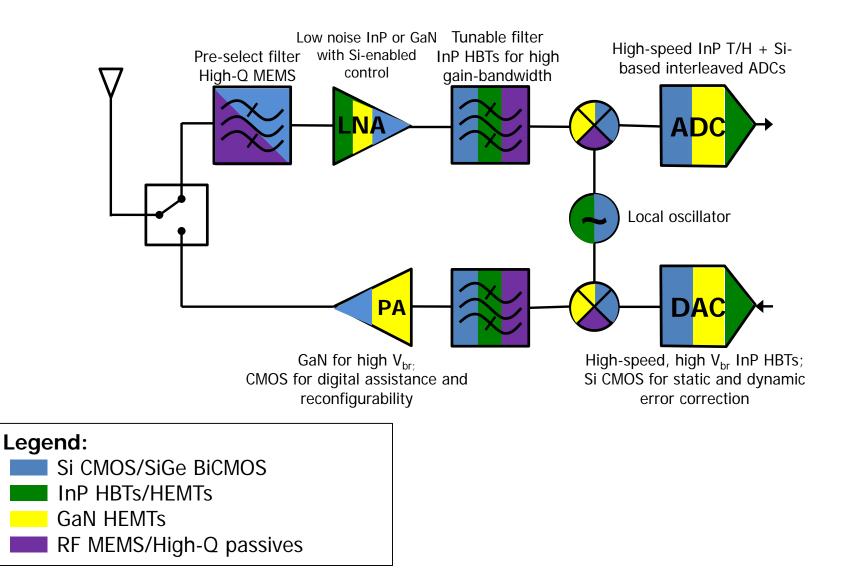

# Progress of Heterogeneous Integration at DARPA

**COSMOS:** Demonstrated benefits of integration of completed devices.

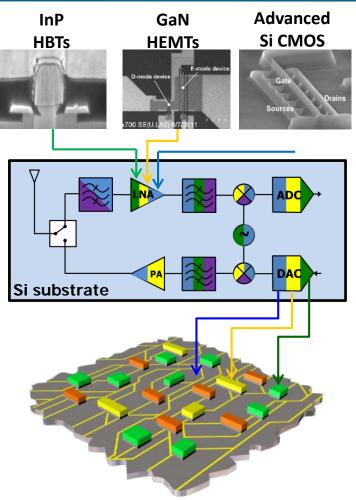

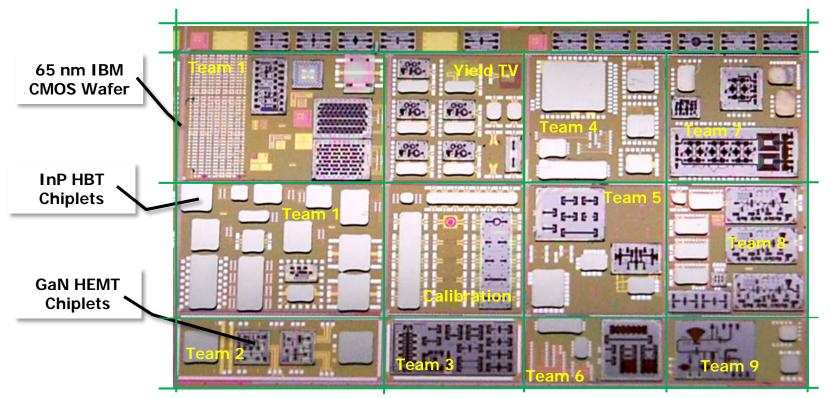

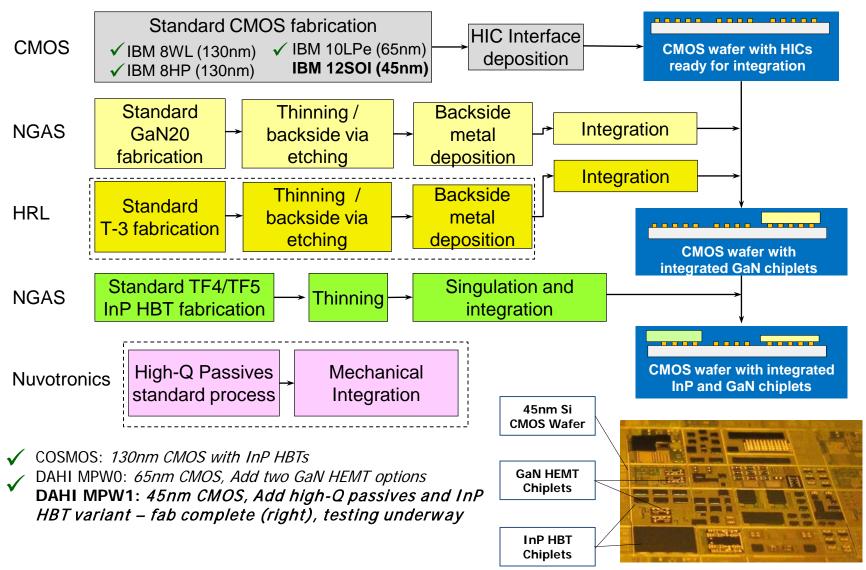

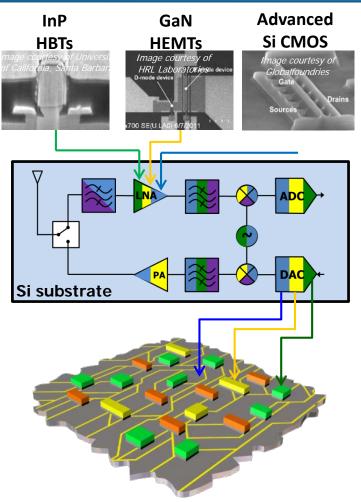

# Diverse Accessible Heterogeneous Integration (DAHI) Foundry for Heterogeneous Integration

Heterogeneous technology integration in accessible foundry

(first three-technology integration demonstrated in Jan 2015)

Heterogeneous Integration of a diverse array of devices on a common Si CMOS platform

*Goal:* To establish a versatile platform of heterogeneous integration that enables pervasive impact on DoD systems.

(3 technology integration demonstrated in Jan 2015)

Successful integration of high performance III-V technologies with CMOS.

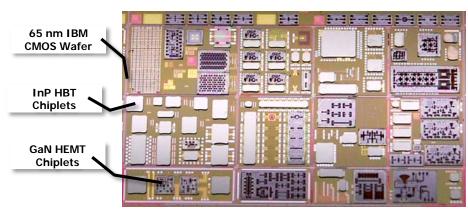

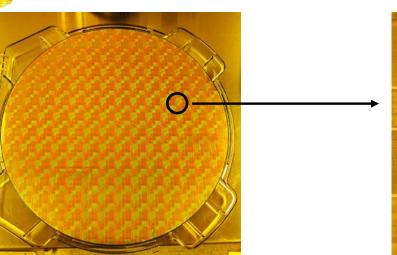

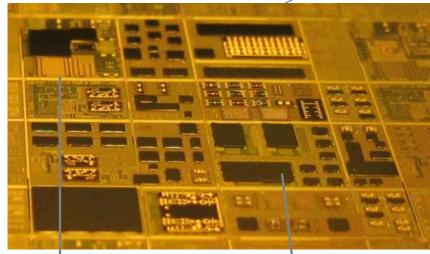

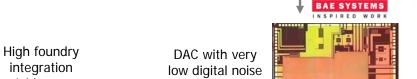

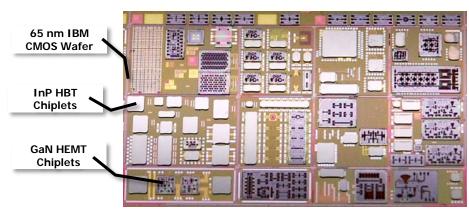

# **DARPA** DAHI MPW1: Excellent Yield, Successful Initial Tests

FOUNDRIES

NORTHROP GRUMMAN

60

- Beta at 1mA

DE HBT Array

300mm diameter Si CMOS wafer (45nm node)

DAHI integration (Dec 2015): Si (45nm), InP (TF5 HBT), GaN (GaN20 HEMT)

NORTHROP GRUMMAN

Successful testing identified optimal S/H circuit for ADC (>65dB SFDR @ 2GHz)

DAC with very low digital noise (-70dBc)

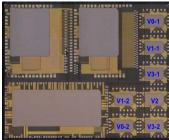

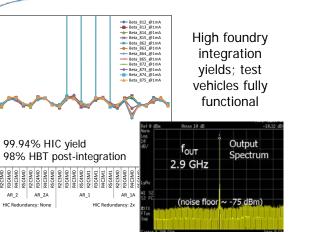

# DAHI MPW1: Dual-Band Frequency Synthesizer Demonstrates Modularity

#### MPW1 Q/E Dual Band Frequency Synthesizer (36 and 72 GHz)

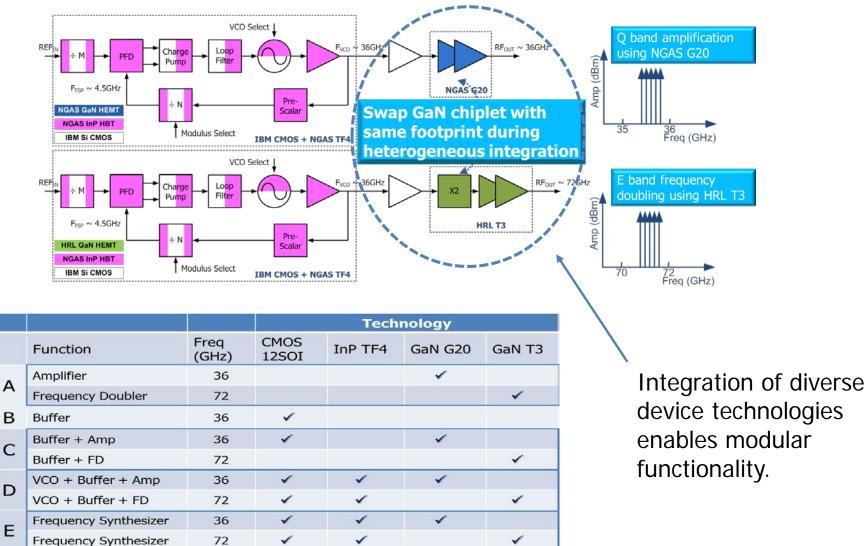

## **DAHI Alternate Flow:** Wafer Bonding of InP and Si CMOS (Teledyne/Tezzaron)

3000

2500

1.0E-01

# **Exploring Emerging Integration Technologies**

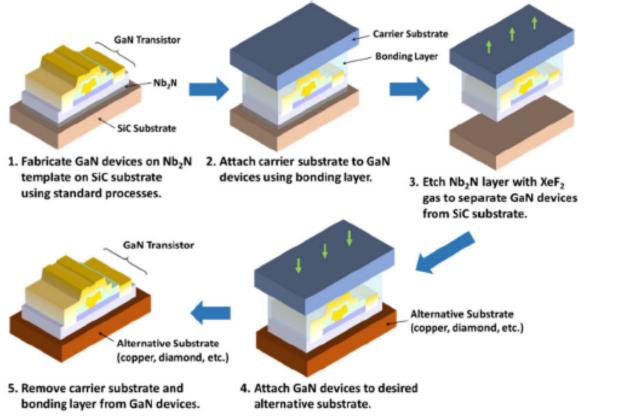

Figure 1. Epitaxial liftoff and transfer of GaN transistor from Nb2N/SiC.

Source: Naval Research Laboratory, CS ManTech 2016

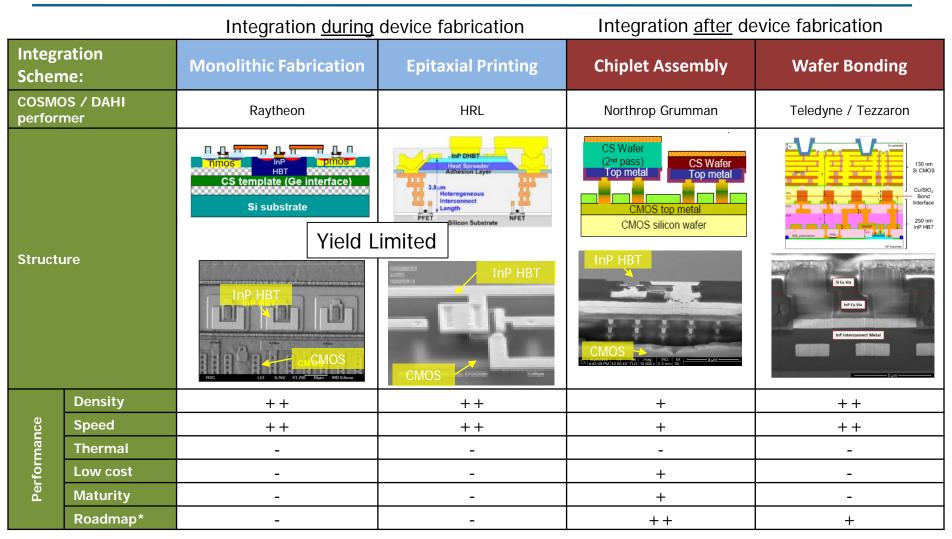

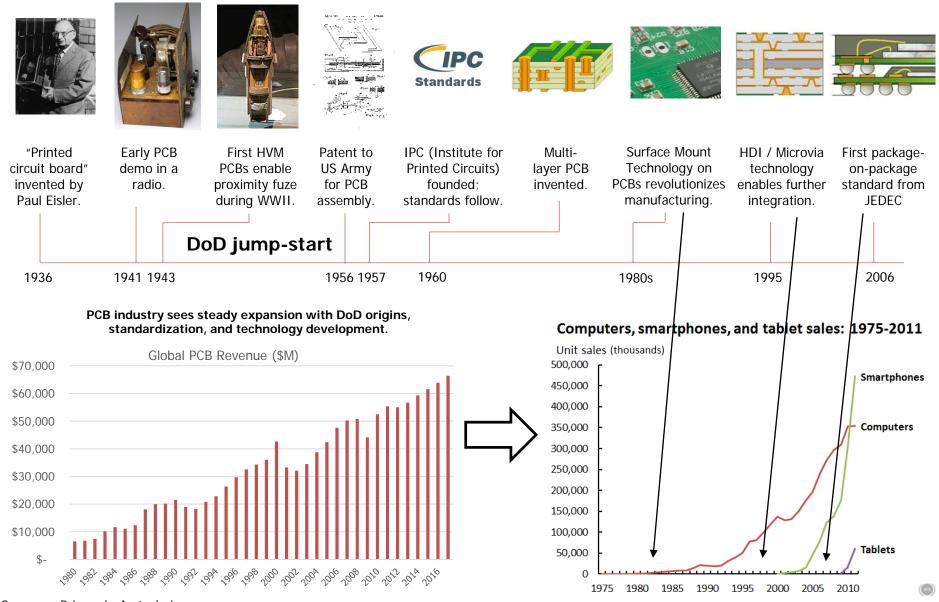

**DARPA** Heterogeneous Integration Platform Options

\*"Roadmap" metric indicates ease of integrating new technologies in the future.

DAHI integration (post-device fabrication) provides a platform combining density, performance, heterogeneity, and ease of integrating new technologies

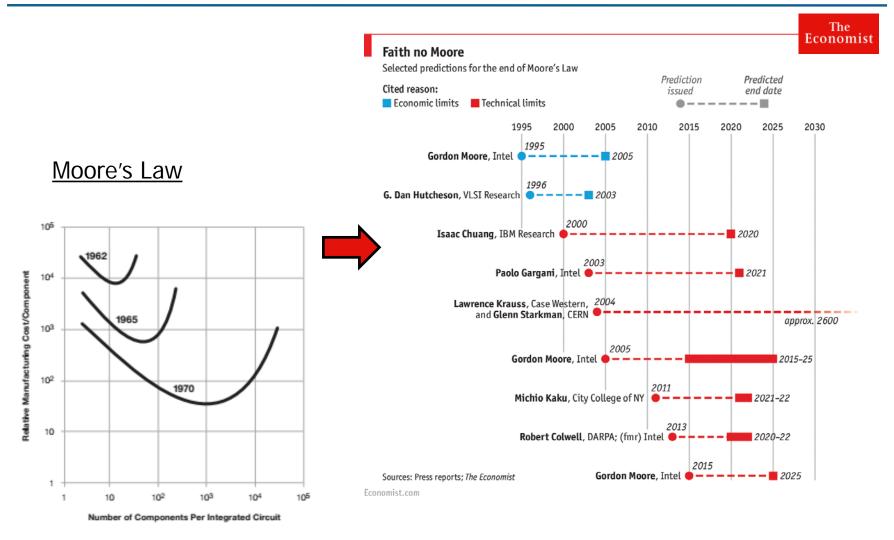

### End of Moore's Law?

#### End of Moore's Law means everyone is becoming low volume

Data source: Electronics Magazine, Economist.com

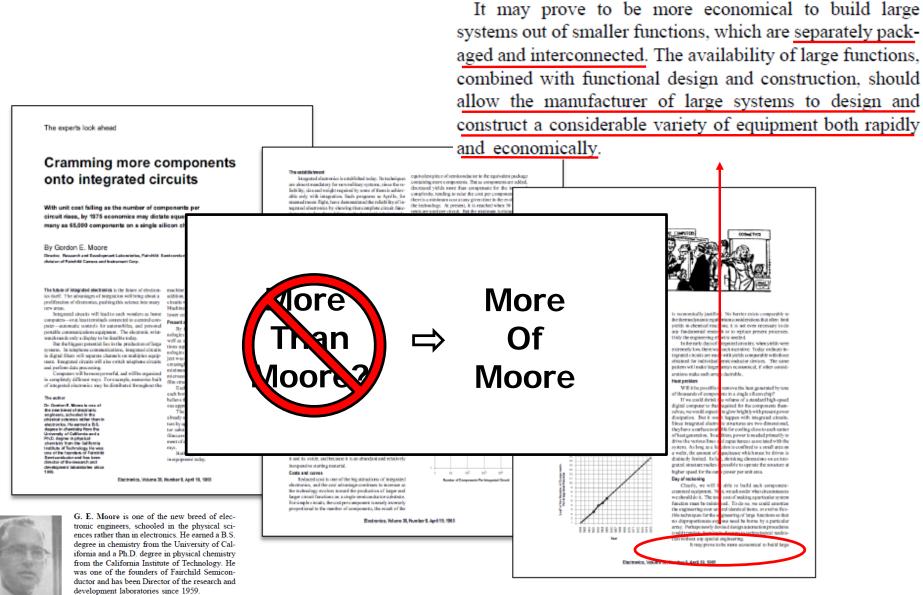

It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.

#### The experts look ahead

#### Cramming more components onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing as many as 65,000 components on a single silicon chip

By Gordon E. Moore **Director:** Research and Development Laboratories, Pairofild Reviewelscher detailors of Palinhild Carrens and Instrument Corp.

The More of integrated electronics is the finance of electronits itself. The advantages of integration will bring about a addition, the improved reliability made possible proliferation of electronics, pushing this science into many NOW OF CASE. Integrated circuits will lead to such wonders as home

computers-or at least terminal's connected to exercisel compater-automatic controls for automobiles, and personal petable communications equipment. The electronic wristwatch needs only a display to be feasible today.

But the biggest potential lies in the production of large ares. In telephone communications, integrated circuits in digital filters will separate channels on multiplex equipment. Integrated circuits will also switch telephone circuits and perform data processing.

Computers will be more percential, and will be organized in completely different ways. For example, memories built of integrated electronics may be distributed throughout the

#### The extrem

The author Dr. Contantill. Means is one of the next timed of electricatic engineers, actualized in the physical sciences wither themis electronics, for earned a D.5, decays in charming them the University of Calibratis and a Ph.D. degree in physical technologies and the physical Processing as in physical PhD, degree in physical rheadbdy from the Galifornia of the foundam of Falmin inclusion of the se-

Machines similar to those in existence today lover costs and with Inter-ten-around. Present and Nauro By integrated electronics, I mean all th nalispics which are referred to as microelectr well as any additional ones that result in eles tions supplied to the user as irreducible units

relogics were first investigated in the late 19 lect was to a inistanize electronics paripment masingly complex electronic functions in line minimum weight. Several approaches evol sicrossenbly techniques for individual con film structures and somiconductor integrated-Each approach evolved rapidly and conve each horrowed techniques from another. Many

machine instead of heing concentrated in a

circuits will allow the construction of larger pr

believe the way of the fature to be a combination ous approaches. The advocates of semiconductor integral already using the improved characteristics of t towiley applying each films directly to an activi-tor substrate. These advocating a technolog films are developing suphisticated techniques ment of as five semiconductor devices to the p 101.5 Bath approaches have worked well a

is equipment tailer.

Electronics, Volume 35, Humber 8, April 19, 1965

G. E. Moore is one of the new breed of electronic engineers, schooled in the physical sciences rather than in electronics. He earned a B.S. degree in chemistry from the University of California and a Ph.D. degree in physical chemistry from the California Institute of Technology. He was one of the founders of Fairchild Semiconductor and has been Director of the research and development laboratories since 1959

#### The establis head

Integrated electronics is established today. Its techniques almost mandatory for new military systems, since the refails ity, size and weight required by some of them is adhievable only with integration. Such programs as Apollo, for manued mean flight, have demonstrated the reliability of integrand electronics by showing that complete circuit func-tions are as free from failure as the best individual stansis-Most comparises in the commercial company field have

machines in design or in early production employing inte-grated electronics. These machines cost less and perform better than those which use "conventional" electronics. instruments of various sofa, especially the tapicity increating numbers employing digital techniques, are starting to use integration because it cars costs of both manufacture

and design The use of linear integrated circultry is still restricted primarily to the military. Such integrated functions are expersive and not available in the variety required to satisfy a major fraction of linear electronics. But the first applica-

#### tions are beginning to appear incommercial electronics, par-ticularly in equipment which useds low-dequercy amplifiers of small size

Reliability counts Instance every case, integrated electronics has demon-trated high reliability. Even at the present level of production-low compared to that of discrete components-it of fors reduced systems cost, and in many systems improved performance has been realized.

Integrated electronics will make electronic techniques more generally available throughout all of society, performing many functions that presently are done inadequately by other techniques or not done at all. The principal advantages will be lower cavis and greatly simplified design-payoffs from a ready upply of low-cost functional packages.

Formost applications, somiconductor integrated circuits will predominate. Semiconductor devices are the only repcouble candidates prevently in existence for the active ele-ments of integrated circuits. Pusitive semiconductor elements look attractive too, because of their potential for low cost and high reliability, but they can be used only if precision is not a prime regainite. Silicon is likely to remain the basic material, although

others will be of use in specific applications. For example, all an averide will be important in integrated microwave functions. But silicon will prodominate at lower throat noise because of the technology which has already evolved around it and its oxide, and because it is an abundant and relatively inexpensive starting material.

#### Costs and carves

Reduced cost is one of the Ng attractions of integrated electronics, and the cost advantage continues to increase or the technology evolves toward the production of keysy and Functions on a single semiconductor substate. larger circuit For simple a local s, the cost remains even is nearly investely. propertional to the number of components, the result of the

equivalent piece of semiconductor in the equivalent package containing more components. But as components are added decreased yields more than compensate for the in complexity, tending to mise the cost per comp there is a minimum cost at any given time in the e

the technology. At present, it is reached when 5 nexts are used per circuit. But the minimum is ris while the entire cost curve is failing (see griph he is look sheed five years, a plot of costs suggests the must past ner component might be expected in siabout 1,000 components per circuit (providing s

functions can be produced in moderate quantities." the manufacturing cost per component can be exonly a tenth of the present cost. The complexity for minimum compo-

created at a rate of roughly a factor of two per graph on next page). Cartainly over the short to can be expected to continue, if ner to increase longer term, the tate of increase is a bit more tanthough there is no reason to believe it will not rem constant for at least 10 years. That means by 1975 ber of components per integrated circuit for minis will be 65,000.

I believe that such a large r nouit curvle built and a

With the dimensional tolerances already being tegented circuits, is plated high-postlor can be built on centers two theorematiks of an inch a

a two-nil agaze can also contain seven I kitches of resir- is recoveringly justified tance or a few diodes. This allows at least 500 components the thermochnamic equil per linear inch or a quarter million per square indy. Thus, yields in chemical reactions, it is not even recessary to do 63,000 components need occupy only about one-fourth a large fundamental research or to replace present processes square lock.

On the allown water currently used, usually as inch or more in diameter. there is angle norm for such a structure if the components can be closely packed with no space wasted For interconnection externs. This is realiding since efforts (c) advanced for individual evolution desires. The same achieve a level of complexity above the presently available integrated circuits are already underway using multilayer anations make such array metalisation patients separated by defective films. Such a density of components can be achieved by present optical techniques and dates not require the more exatic techniques, such as electron beam operations, which are being studied to make even smaller structures.

#### increasing the yield

There is no functionertal obstacle to achieving device yields of 100%. At present, packaging nots to far exceed the cost of the semiconductor structure sheef that there is no incentive to improve yields, but they can be entired as high as

No harrier exists comparable man considerations that often limit Only the engineering of set is needed. In the early days of the particularity

control circuity, when yields were extremely low there we such incentive. Today archivary inlegrated a touts are made with yields comparable with those pattern will make larger ars economical, if other considdesirable

#### Heat problem Will kbe mealing nove the heat generated by ten

of thousands of composition a single silicon chip. If we could shrink the volume of a standard high-speed dial computer to that equired for the components framdigital computer to that salves, we would expect to to glow bright h with present power dissipation. But it was thappen with integrated circuits. Since integrated electro ic structures are two-dimensional, they have assurface available for cooling close to each conterof hest garenties. In a fitter, power is needed primarily in drive the various lines a capacitaness associated with the senters. As long as a function is conflued to a small area on a wafty, the amount of citance which must be driven is distinctly limited. In fact, shrinking dimensions on an integrated structure makes possible to operate the structure at higher speed for the same power per unit area.

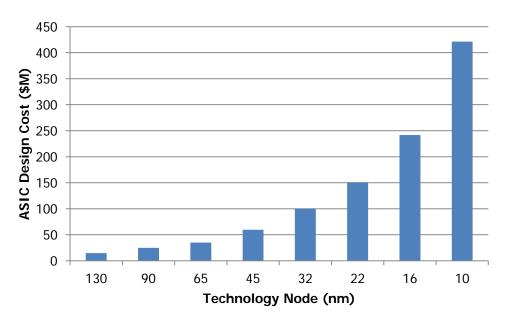

Expensive to design at advanced nodes ...

... which some commercial products can support ...

© apple.com

Fab cost for commercial electronics amortized over **one day's** worth of iPhones

... but DoD cannot.

Fab cost for a DoD IC amortized over **entire 29-year** acquisition of JSF

Source: "Cashing in with Chips" AlixPartners Semiconductor R&D outlook report, 2014.

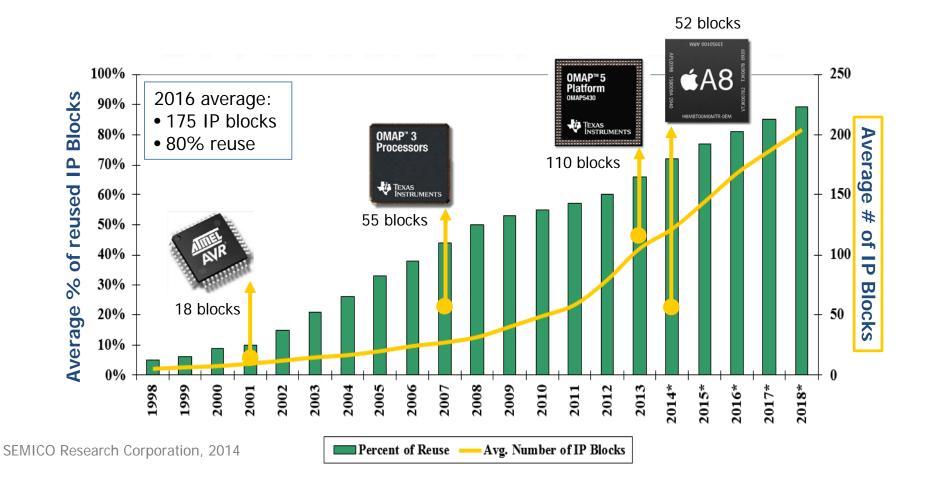

# ...and IP Reuse is Common for Multicore SoCs...

IP Reuse is increasingly important and shows no signs of slowing

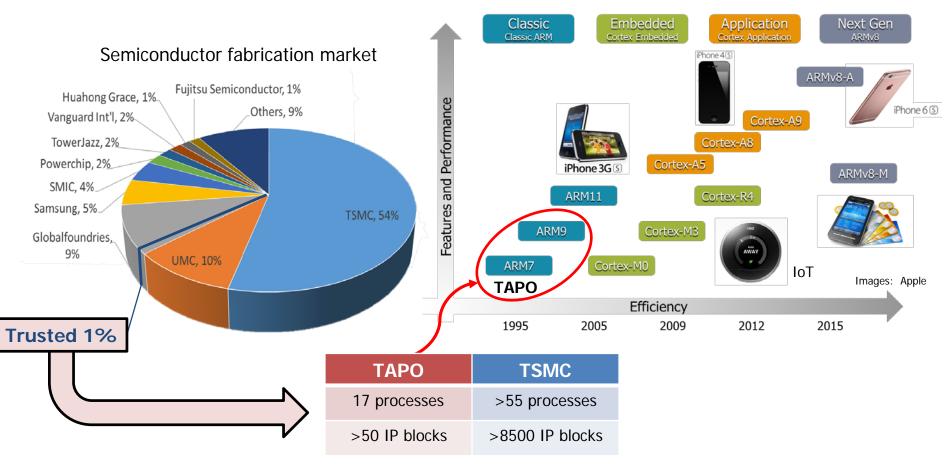

### Limited access to global pool of knowledge and talent

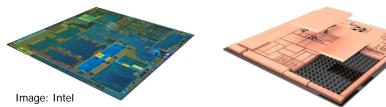

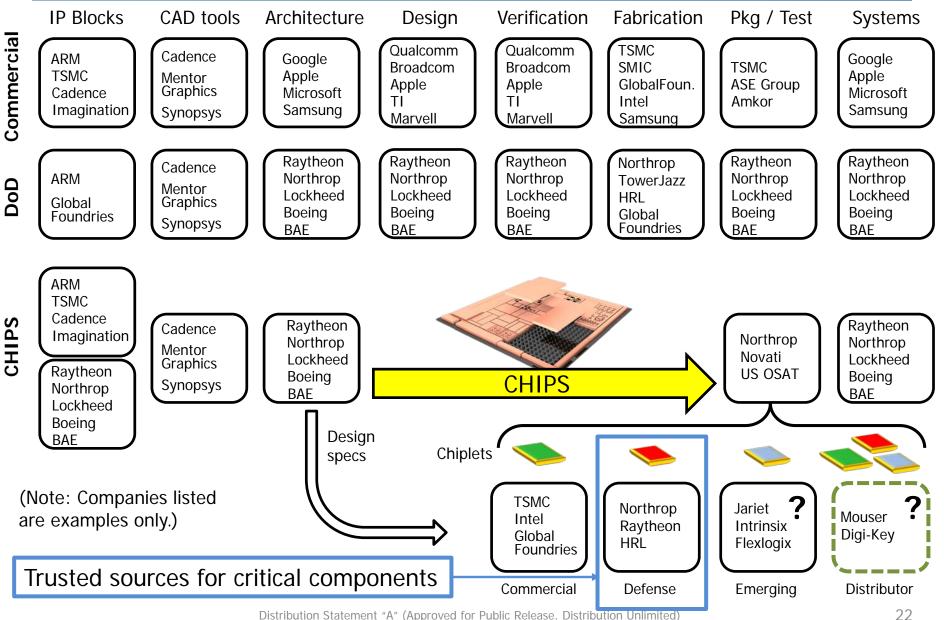

#### CHIPS is designed to expand the pool of IP and design resources

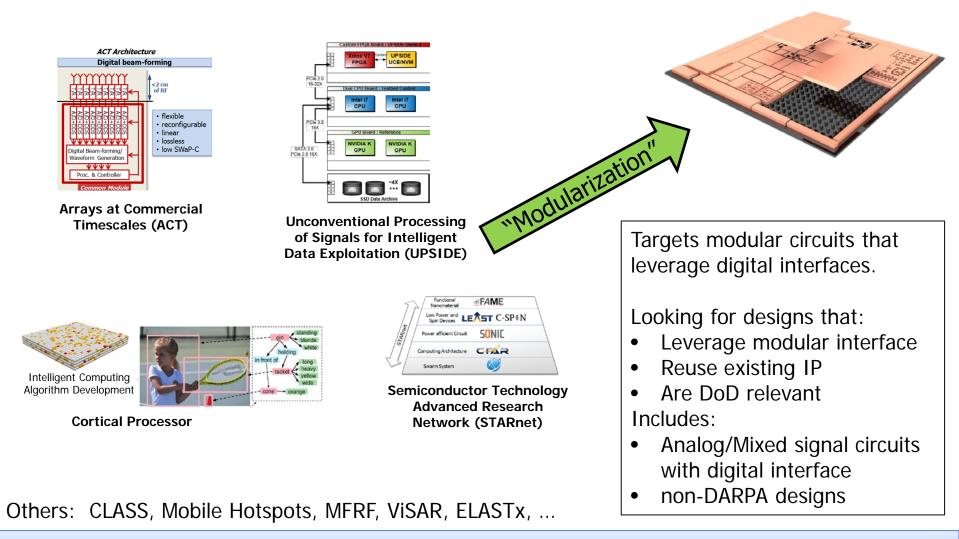

### Common Heterogeneous integration and IP reuse Strategies program

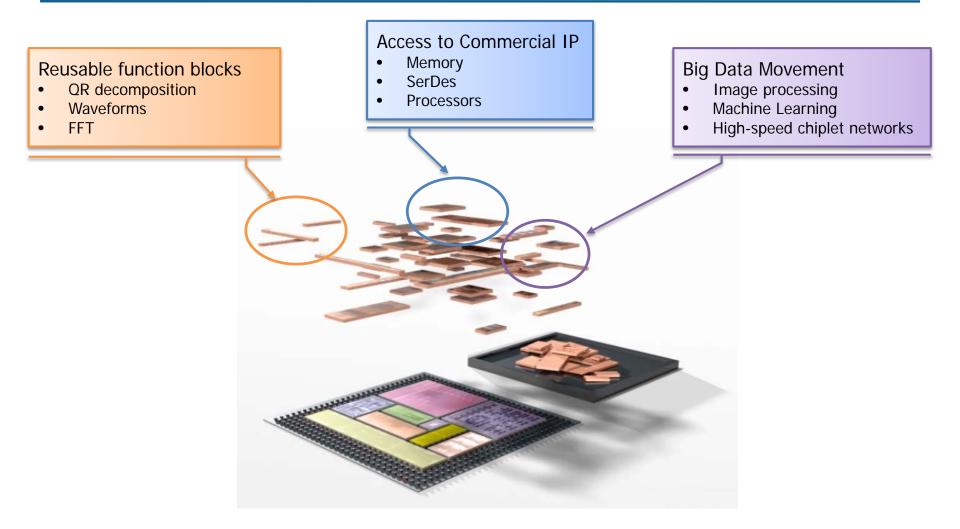

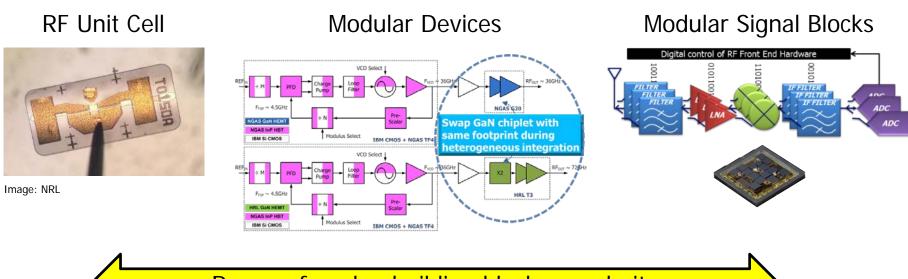

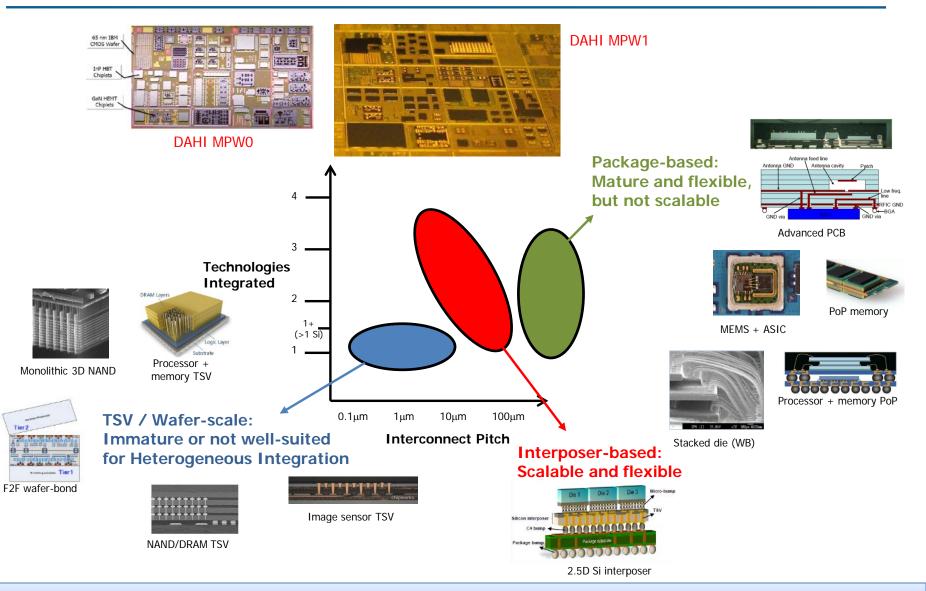

CHIPS will develop the **design tools and integration standards** required to demonstrate **modular electronic systems** that can leverage **the best of DoD and commercial** designs and technology.

Today – Monolithic

Tomorrow – Modular

### What is CHIPS?

CHIPS will develop **design tools**, **integration standards**, **and IP blocks** required to demonstrate **modular electronic systems** that can leverage **the best of DoD and commercial** designs and technology.

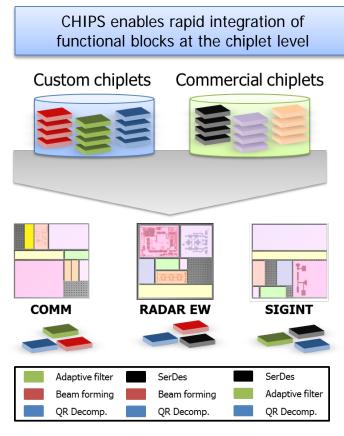

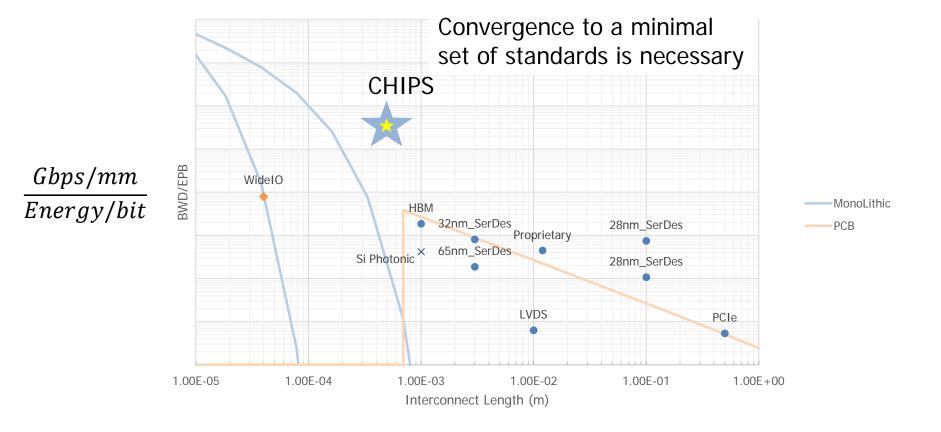

### Interface Standards: Too Many? Not Enough? How to Compare?

#### CHIPS challenge: make a usable interface standard

Interface Standards: Too Many? Not Enough? How to Compare?

#### CHIPS challenge: make a usable interface standard

### Implications: CHIPS end state vs. conventional supply chain

#### CHIPS modularity targets the enabling of a wide range of custom solutions

#### Common Heterogeneous Integration and IP Reuse Strategies Broad Agency Announcement:

https://www.fbo.gov/spg/ODA/DARPA/CMO/DARPA-BAA-16-62/listing.html

Commercial Performer Program Announcement, DARPA-PA-17-01 https://www.fbo.gov/spg/ODA/DARPA/CMO/DARPA-PA-17-01/listing.html

- What: DARPA is looking to fund and de-risk non-incremental ideas that are beyond the standard corporate R&D roadmap.

- Who: Companies that have received less than \$50M in defense contracts in the past year

- How:

- 1. Start a conversation with a Program Manager

- 2. E-mail your idea to MTOProgramAnnouncement@darpa.mil

- When: Rolling call, open all year

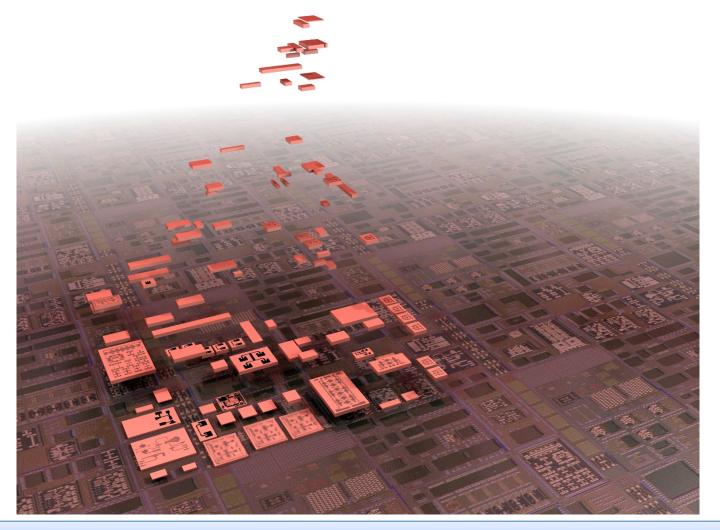

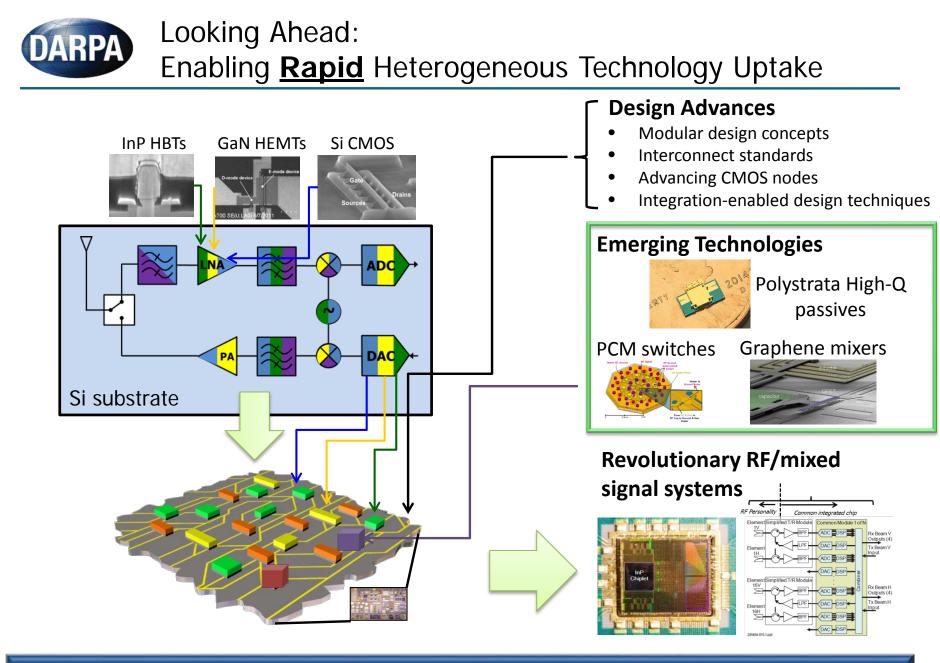

# **DARPA** CHIPS future of heterogeneous integration

### Requires a lot of pieces coming together!

www.darpa.mil

Vision for Representative Transceiver: 4+ Device Technologies

(Second three-technology integration demonstrated in Dec 2015)

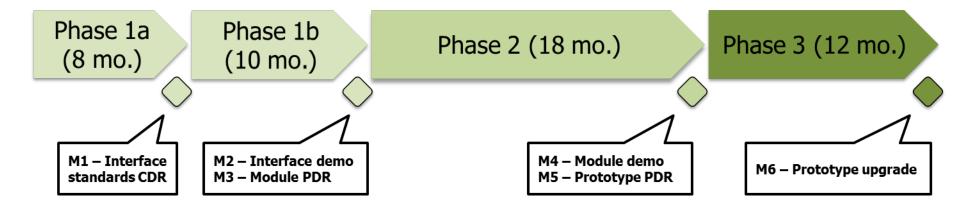

# **DARPA** CHIPS Program – Program Summary

| PHASE 1                             | PHASE 2                      | PHASE 3              |  |

|-------------------------------------|------------------------------|----------------------|--|

| Interface and IP Block Demo         | Module Demo with IP Blocks   | Rapid Module Upgrade |  |

| Integration platform Interface demo | Full system IP<br>reuse demo | Reconfigured demo    |  |

| TA1 Modular Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                           |                                                                                                                                                               |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <ul> <li>Modularize existing digital design<br/>via interface standard.</li> <li>Critical design review for standards<br/>at 8-month mark.</li> <li>Demonstrate functional IP blocks.</li> </ul>                                                                                                                                                                                                                                           | <ul> <li>Demonstrate functional digital<br/>design.</li> <li>Cost + design cycle analysis.</li> <li>Present design for Phase3.</li> </ul> | <ul> <li>Demonstrate rapid upgradability.</li> <li>Cost + design cycle analysis<br/>comparing CHIPS module versus a<br/>monolithic implementation.</li> </ul> |  |  |  |

| TA2 Modular Analog Systems                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                           |                                                                                                                                                               |  |  |  |

| <ul> <li>Modularize existing analog design via interface standard.</li> <li>Review design and interface at the 8-month mark.</li> <li>Demonstrate interconnect performance.</li> <li>Integrate blocks into PLIC.</li> <li>Analyze against SoA for performance, unit cost, NRE, and turnaround time.</li> <li>Develop business model for modular analog ecosystem.</li> <li>Develop business model for modular analog ecosystem.</li> </ul> |                                                                                                                                           |                                                                                                                                                               |  |  |  |

| TA3 Supporting Technologies                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                           |                                                                                                                                                               |  |  |  |

| Design Tools, Assembly Methods, IP in support of TA1 and/or TA2 tasks and metrics                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                           |                                                                                                                                                               |  |  |  |

- Anticipated Funding Available for Award: DARPA anticipates a funding level of approximately \$70M for the CHIPS program.

- Anticipated individual awards Multiple awards in each Technical Area are anticipated.

- Anticipated funding type 6.2 and/or 6.3

- **Types of instruments that may be awarded** Procurement contract, grant, cooperative agreement or other transaction.

| Important Dates    |             |  |  |  |

|--------------------|-------------|--|--|--|

| Proposers Day      | 21-Sep-2016 |  |  |  |

| BAA Release (est.) | 26-Sep-2016 |  |  |  |

| Abstracts Due*     | 26-Oct-2016 |  |  |  |

| FAQ Deadline*      | 23-Nov-2016 |  |  |  |

| Proposals Due*     | 7-Dec-2016  |  |  |  |

| Program Kick-Off*  | Mar-2017    |  |  |  |

\*Dates are a function of actual BAA release date.

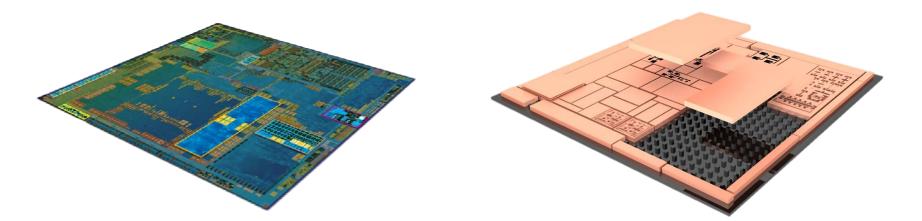

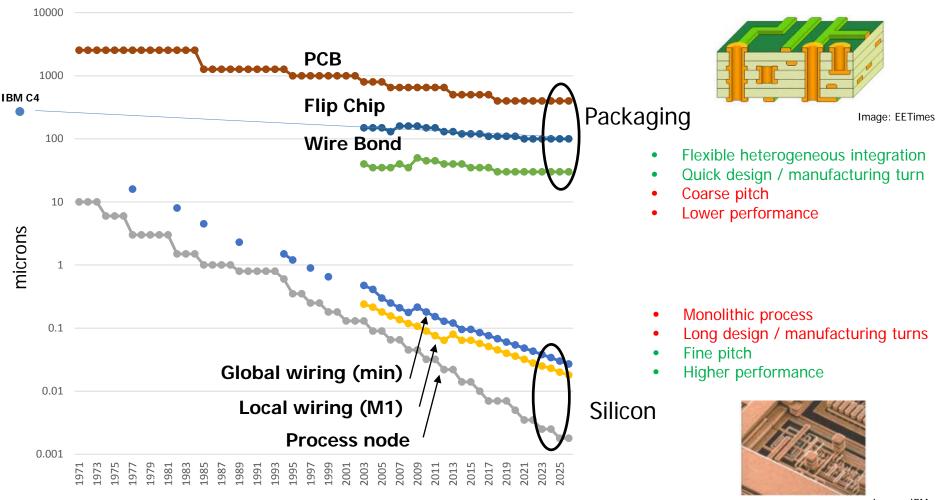

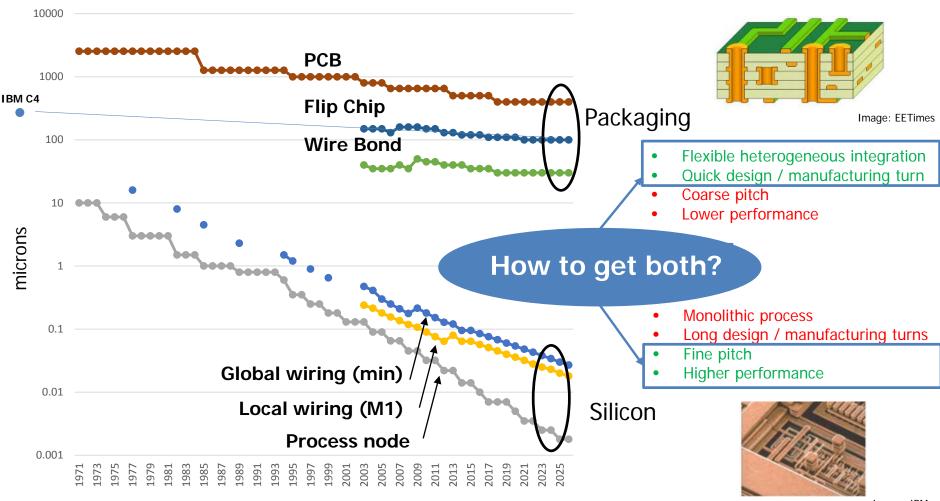

## Conventional Assembly Has Attractive Features for HI ... But Isn't Keeping Up on Pitch and Performance

Image: IBM

# Need to combine speed and flexibility of packaging with pitch and performance of advanced heterogeneous device technology.

Source: 2003-13 ITRS, Wikipedia Distribution Statement "A" (Approved for Public Release, Distribution Unlimited)

Conventional Assembly Has Attractive Features for HI ... But Isn't Keeping Up on Pitch and Performance

Image: IBM

Need to combine speed and flexibility of packaging with pitch and performance of advanced heterogeneous device technology.

Source: 2003-13 ITRS, Wikipedia Distribution Statement "A" (Approved for Public Release, Distribution Unlimited)

# Diverse Accessible Heterogeneous Integration (DAHI) Foundry for Heterogeneous Integration

Heterogeneous technology integration in accessible foundry

(first three-technology integration demonstrated in Jan 2015)

Image: Northrop Grumman

Heterogeneous Integration of a diverse array of devices on a common Si CMOS platform

*Goal:* To establish a versatile platform of heterogeneous integration that enables pervasive impact on DoD systems.

### CHIPS Summary

| Important Dates    |             |  |  |  |

|--------------------|-------------|--|--|--|

| Proposers Day      | 21-Sep-2016 |  |  |  |

| BAA Release (est.) | 26-Sep-2016 |  |  |  |

| Abstracts Due*     | 26-Oct-2016 |  |  |  |

| FAQ Deadline*      | 23-Nov-2016 |  |  |  |

| Proposals Due*     | 7-Dec-2016  |  |  |  |

| Program Kick-Off*  | Mar-2017    |  |  |  |

| TA1                         | Modular Digital Systems |  |  |  |

|-----------------------------|-------------------------|--|--|--|

| TA2                         | Modular Analog Systems  |  |  |  |

| TA3 Supporting Technologies |                         |  |  |  |

\*Dates are a function of actual BAA release date.

### <u>Questions:</u> <u>DARPA-BAA-16-62@darpa.mil</u>

# **DARPA** CHIPS Program – Structure and Timing

| PHASE 1                                                                                                      | PHAS                         | E 2                                                 | PHASE 3              |                                 |

|--------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------|----------------------|---------------------------------|

| Interface and IP Block Demo                                                                                  | Module Demo with IP Blocks   |                                                     | Rapid Module Upgrade |                                 |

| Integration platform Interface demo                                                                          | Full system IP<br>reuse demo |                                                     | Reconfigured demo    |                                 |

| Phase 1a<br>(8 mo.) Phase 1b<br>(10 mo.)<br>M1 – Interface<br>standards CDR M1 – Interface<br>M3 – Module PE | Phase<br>1<br>demo           | e 2 (18 mo.)<br>M4 – Module der<br>M5 – Prototype I | 1<br>10 M6-1         | 3 (12 mo.)<br>Prototype upgrade |

|                                                                                                              | TA1                          | Modular Digit                                       | tal Systems          |                                 |

| 1 - 1 - Sa                                                                                                   |                              | Û                                                   |                      | 1                               |

|                                                                                                              | TA3                          | Supporting To                                       | echnologies          |                                 |

|                                                                                                              |                              | Ĵ                                                   |                      | 1                               |

|                                                                                                              |                              | Modular Anal                                        | og Systems           |                                 |

# **CHIPS Program - Metrics**

| CHIPS Program Metrics                         |                        |                        |                                         |  |  |

|-----------------------------------------------|------------------------|------------------------|-----------------------------------------|--|--|

| Metric                                        | Phase 1                | Phase 2                | Phase 3                                 |  |  |

| Design level                                  |                        |                        |                                         |  |  |

| IP reuse (1)                                  | > 50% public IP blocks | > 50% public IP blocks | > 50% public IP blocks                  |  |  |

| Modular design (2)                            |                        |                        | > 80% reused, > 50%<br>prefabricated IP |  |  |

| Access to IP (3)                              | > 2 sources of IP      | > 2 sources of IP      | > 3 sources of IP                       |  |  |

| Heterogeneous integration (4)                 | > 2 technologies       | > 2 technologies       | > 3 technologies                        |  |  |

| NRE reduction (5)                             |                        | > 50%                  | >70%                                    |  |  |

| Turnaround time<br>reduction (5)              |                        | > 50%                  | >70%                                    |  |  |

| Performance Benchmarks<br>(performer defined) |                        | >95% benchmark         | >100% benchmark                         |  |  |

| Digital Interfaces                            |                        |                        |                                         |  |  |

| Data rate (scalable) (6)                      | 10 Gbps                | 10 Gbps                | 10 Gbps                                 |  |  |

| <b>Energy efficiency (7)</b>                  | < 1 pJ/bit             | < 1 pJ/bit             | < 1 pJ/bit                              |  |  |

| Latency (7)                                   | $\leq$ 5 nsec          | $\leq$ 5 nsec          | $\leq$ 5 nsec                           |  |  |

| Bandwidth density                             | > 1000 Gbps/mm         | > 1000 Gbps/mm         | > 1000 Gbps/mm                          |  |  |

| Analog interfaces                             |                        |                        |                                         |  |  |

| Insertion loss (across full bandwidth)        | < 1 dB                 | < 1 dB                 | < 1 dB                                  |  |  |

| Bandwidth                                     | $\geq$ 50 GHz          | $\geq$ 50 GHz          | $\geq$ 50 GHz                           |  |  |

| Power Handling                                | $\geq$ 20 dBm          | $\geq$ 20 dBm          | $\geq$ 20 dBm                           |  |  |

Notes:

- 1. Public IP is defined as IP blocks available through commercial vendors or shared among performers.

- 2. Reuse is defined as existing or previously designed IP that is re-implemented into the current system. Prefabricated IP is defined as IP blocks already physically instantiated.

- 3. Valid sources of IP must be those that are outside of the performer team.

- 4. Various Silicon process nodes, RF passives, or compound semiconductor devices.

- 5. The non-recurring engineering (NRE) cost and turnaround time will be compared against a benchmark design.

- 6. Minimum bus/lane data rate and should be capable of scaling to higher data rates.

- 7. Performance relating to transferring data between chiplets compared against a benchmark design.

# **DARPA** TA1: Modular Digital Systems

Don't need to start from scratch!

# **DARPA** TA2: Modular Analog Systems

Range of analog building block granularity

Seeks to realize modular pseudolithic microwave integrated circuits:

- Leverage modular building blocks

- Demonstrate performance into mm-Wave regime

- Develop sustainable attractive business models

#### Balance granularity with accessibility, reusability and cycle time

- Design tools

- Heterogeneous integration

- Modular design flows

- Assembly methods

- Fine pitch •

- Small device handling / testing

- Multi-device technology processing ۰

- IP blocks

#### Sample Digital IP

| Processor           | Interface | Memory     |

|---------------------|-----------|------------|

| Image signal        | SerDes    | Controller |

| Audio signal        | USB       | DRAM       |

| Digital signal      | PCIe      | SRAM       |

| Compression         |           | Flash      |

| GPU                 |           |            |

| CPU                 |           |            |

| Machine<br>Learning |           |            |

Key challenge will be alignment to TA1 and TA2

Technology NOT germane to CHIPS:

- New device technologies •

- Wholly new circuits •

- Security specific processes (e.g. obscuration, split fabrication) •

#### Focus is on making modularity work!

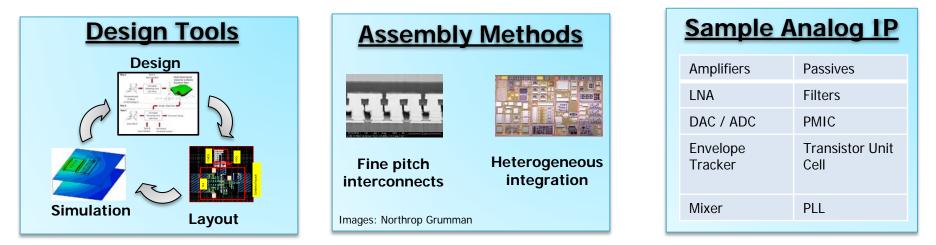

## **DARPA** Propelled by Standards and Modularity: Electronics Industry Built via Integration on PCBs

Sources: Prismark, Arstechnica, USPTO, Wikipedia, IPC, SMTA

# **DARPA** Heterogeneous Integration: Bridging the Gap

DAHI creates integration capabilities beyond current advanced interconnect technologies.

Platform gives ability to rapidly add technologies as they are developed